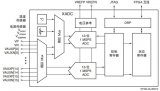

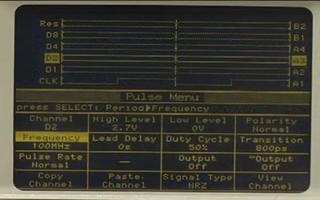

介绍一种基于FPGA技术的时间间隔测量方法,通过分析FPGA的主要技术优势及其在工业控制领域中所处的重要地位,给出设计时间间隔测量模块所选用的FPGA器件并进行硬件设计,以及所选

2011-10-13 14:53:47 2593

2593

FPGA的功耗高度依赖于用户的设计,没有哪种单一的方法能够实现这种功耗的降低。目前许多终端市场对可编程逻辑器件设计的低功耗要求越来越苛刻。

2011-11-28 11:45:56 1117

1117 以下是笔者一些关于FPGA功耗估计和如何进行低功耗设计的知识。##关于FPGA低功耗设计,可从两方面着手:1)算法优化;2)FPGA资源使用效率优化。

2014-12-17 09:27:28 9177

9177 本文探讨了对低功耗待测器件(DUT)进行低电流测量的两种不同方法:一是将电源、高精度数字多用表及待测器件进行串联,二是使用高精度测量电源。应用笔记详细介绍了怎样配置2280S系列高进度测量直流电源

2015-01-23 16:12:46 3384

3384 整个FPGA设计的总功耗由三部分功耗组成:1. 芯片静态功耗;2. 设计静态功耗;3. 设计动态功耗。

2022-11-24 20:46:41 1028

1028 高云半导体基于超低功耗的非易失FPGA GW1NZ-ZV器件现已全面量产,此产品是迄今为止功耗最低的FPGA器件。 当核电压为0.9V时,静态功耗不到28uW。

2020-01-06 10:29:07 1823

1823 FPGA功耗的基本概念,如何降低FPGA功耗?IGLOO能够做到如此低的功耗是因为什么?

2021-04-30 06:08:49

美高森美公司营销总监TIM MORIN在现今日益趋向超连接的世界(hyper-connected world)中,如何保护新的设计避免被克隆、反向工程和/或篡改是一项重大挑战。FPGA器件通过加入

2019-06-25 08:18:11

FPGA已经被广泛用于实现大规模的数字电路和系统,随着CMOS工艺发展到深亚微米,芯片的静态功耗已成为关键挑战之一。文章首先对FPGA的结构和静态功耗在FPGA中的分布进行了介绍。接下来提出了晶体管

2020-04-28 08:00:00

FPGA的功耗高度依赖于用户的设计,没有哪种单一的方法能够实现这种功耗的降低,如同其它多数事物一样,降低功耗的设计就是一种协调和平衡艺术,在进行低功耗器件的设计时,人们必须仔细权衡性能、易用性、成本

2015-02-09 14:58:01

FPGA的功耗高度依赖于用户的设计,没有哪种单一的方法能够实现这种功耗的降低,如同其它多数事物一样,降低功耗的设计就是一种协调和平衡艺术,在进行低功耗器件的设计时,人们必须仔细权衡性能、易用性、成本、密度以及功率等诸多指标。

2019-11-05 07:54:43

器件有一个整体的了解。(特权同学,版权所有)Cyclone IIIFPGA系列前所未有的同时实现了低功耗、高性能和低成本,大大提高了产品竞争力。其特性以及Cyclone III FPGA体系结构为用户

2015-04-17 12:05:21

大容量、高速率和低功耗已成为FPGA的发展重点。嵌入式逻辑分析工具无法满足通用性要求,外部测试工具可以把FPGA内部信号与实际电路联合起来观察系统真实运行情况。随着FPGA技术的发展,大容量、高速

2019-08-07 07:50:15

FPGA的功耗高度依赖于用户的设计,没有哪种单一的方法能够实现这种功耗的降低,在进行低功耗器件的设计时,人们必须仔细权衡性能、易用性、成本、密度以及功率等诸多指标。

2019-08-29 07:52:29

突破FPGA系统功耗瓶颈 FPGA作为越来越多应用的“核心”,其功耗表现也“牵一发而动全身”。随着工艺技术的越来越前沿化,FPGA器件拥有更多的逻辑、存储器和特殊功能,如存储器接口、DSP模块

2018-10-23 16:33:09

的FPGACyclone III LS器件具有200K逻辑单元、8 Mbits嵌入式存储器以及396个嵌入式乘法器,是高性能处理、低功耗应用的理想选择,包括:●汽车●消费类●显示●工业●视频和图像处理●无线具有

2019-04-15 02:21:50

目前许多终端市场对可编程逻辑器件设计的低功耗要求越来越苛刻。工程师们在设计如路由器、交换机、基站及存储服务器等通信产品时,需要密度更大、性能更好的FPGA,但满足功耗要求已成为非常紧迫的任务。而在

2019-07-15 08:16:56

针对I/O需求数目更多的低功耗应用,Actel可以提供IGLOO PLUS系列,规模分别是3万、6万和12.5万门。和相同封装的IGLOO器件相比,可以提供最多多出64%的I/O。其所有的器件都支持

2019-07-05 07:19:19

随着65nm工艺的应用以及更多低功耗技术的采用,FPGA拥有了更低的成本、更高的性能以及突破性的低耗电量,具备进入更广泛市场的条件。FPGA从业者表示,今年FPGA快速增长,而预计明年仍将是一个增长年。

2019-10-31 06:49:34

测量真实的43.2 Gb/s眼图

2019-06-28 09:14:06

我正在尝试测量spartan3(Spartan 3E入门套件)的静态功耗。为此,我使用分流电阻和使能信号确保FPGA不执行应用程序。在FPGA配置之后,在我启用应用程序运行之前,我观察到当前的消耗

2019-05-20 13:40:40

Altera 新的 Cyclone® IV 系列 FPGA 器件巩固了 Cyclone 系列在低成本、低功耗 FPGA市场的领导地位,并且目前提供集成收发器功能的型号。Cyclone IV 器件旨在

2017-11-13 11:22:50

嗨,我正在尝试测量SP605评估板上Spartan6器件的功耗。第一个问题:电路板上是否有电阻,我可以通过简单的O-scope设置来测量电压(需要电阻以便我可以计算电流)?原理图对于确定我能找到这个

2019-08-22 10:02:06

无论从微观到宏观、从延长电池寿命到减少全球变暖的温室效应等等,各种不同因素都在迅速推动系统设计人员关注节能问题。一项有关设计优先考虑事项的最新调查指出,大部分工程师已把功耗排在首位,或者是将其紧跟在性能、密度和成本之后。在功耗方面,FPGA带来了独特的挑战。为什么要设计优化FPGA功耗?

2019-08-08 07:39:45

客户关注的问题。降低FPGA功耗是降低封装和散热成本、提高器件可靠性以及打开移动电子设备等新兴市场之门的关键。

2019-09-20 06:33:32

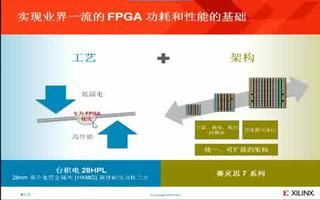

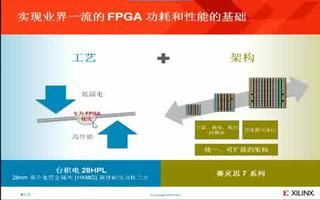

Altera公司产品和企业市场副总裁DannyBiran低功耗是一种战略优势 在器件的新应用上,FPGA功耗和成本结构的改进起到了非常重要的作用。Altera针对低功耗,同时对体系结构和生产工艺进行

2019-07-16 08:28:35

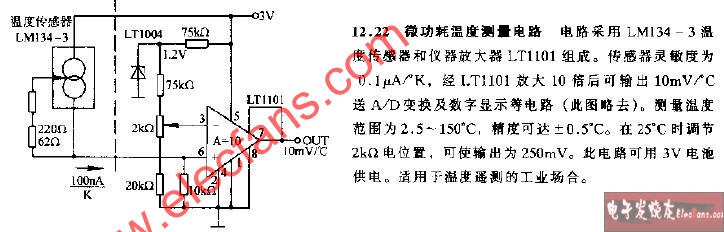

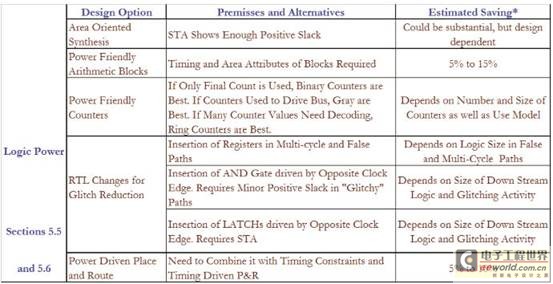

新一代 FPGA的速度变得越来越快,密度变得越来越高,逻辑资源也越来越多。那么如何才能确保功耗不随这些一起增加呢?很多设计抉择可以影响系统的功耗,这些抉择包括从显见的器件选择到细小

2012-01-11 11:59:44

`低功耗的赛灵思 FPGA 系列使总线供电的 USB 器件设计垂手可得凭借在市场中数十亿的端口数量,通用串行总线 (USB) 成为实现主机与外设之间千兆位以下连接的首选接口。不过,由于 USB 规范

2016-07-27 17:14:50

结合采用低功耗元件和低功耗设计技术在目前比以往任何时候都更有价值。随着元件集成更多功能,并越来越小型化,对低功耗的要求持续增长。当把可编程逻辑器件用于低功耗应用时,限制设计的低功耗非常重要。本文将讨论减小动态和静态功耗的各种方法,并且给出一些例子说明如何使功耗最小化。

2019-07-12 06:38:08

FPGA 实验板实物图如图所示这是整板的外设器件的示意图。FPGA 实验板接口芯片连接如图所示二、电源电路与任何电子元器件一样,FPGA 器件需要有电源电压的供应才能工作。尤其对于规模较大的器件,其功耗也相对较高,其供电系统的好坏将直接影响到整个开发系统的稳定性。所以,设计出高效率、高性能的 FP

2021-11-17 07:46:27

的方式开关器件,对比整机电流的变化值,估算这些器件的工作电流。硬件拆解法电路板在设计之初,为了方便功耗的验证与测量,可以设置一些0R(零欧姆)电阻,串接在各个电源回路里。拆解方法:如电源回路中串接了一个

2022-10-14 11:18:18

大家好,我想测量我的Virtex 5 FPGA在ML505板上的功耗(该板实际上是XUPV5-LX110T),通过在这个论坛中搜索,似乎唯一的方法是测量板上特定电阻的电流(电压) 。我在这个论坛上

2020-06-13 19:33:07

设计出色的低功耗应用需要考虑哪些因为? 如何为低功耗应用选择正确的uC外围器件?

2021-04-08 06:53:11

减小动态和静态功耗的方法有哪些?如何使FPGA设计中的功耗最小化?

2021-05-08 07:54:07

复杂器件专业技术相结合,将为系统供应商提供低功耗的芯片方案,供他们在此基础上持续提高带宽容量,并完成更智能的处理。此外,TPACK提供的芯片解决方案可以导入到最新的FPGA中,进一步降低功耗。最终实现

2019-07-31 07:13:26

如何才能实现降低FPGA设计的功耗?

2021-04-29 06:47:38

FPGA的功耗高度依赖于用户的设计,没有哪种单一的方法能够实现这种功耗的降低,如同其它多数事物一样,降低功耗的设计就是一种协调和平衡艺术,在进行低功耗器件的设计时,人们必须仔细权衡性能、易用性、成本、密度以及功率等诸多指标。

2019-08-15 08:28:42

Actel公司的ILGOO系列器件是低功耗FPGA产品,是在便携式产品设计中替代ASIC和CPLD的最佳方案。它在Flash*Freeze模式时的静态功耗最低可达到2µW,电池寿命是采用主流PLD

2020-05-13 08:00:00

。但并不是所有工艺技术都一样。例如,对于 90 nm 技术来说,Virtex-4 器件与其他 90 nm FPGA 技术之间在静止功耗方面存在显著差异,然而,在静止功耗随工艺技术缩小而增加的同时,动态

2020-12-30 08:00:00

怎么用MCU测量当前系统的运行功耗

2023-10-13 07:20:43

Actel公司的ILGOO系列器件是低功耗FPGA产品,是在便携式产品设计中替代ASIC和CPLD的最佳方案。它在Flash*Freeze模式时的静态功耗最低可达到2µW,电池寿命是采用主流PLD

2019-07-31 07:05:45

` 在项目设计初期,基于硬件电源模块的设计考虑,对FPGA设计中的功耗估计是必不可少的。笔者经历过一个项目,整个系统的功耗达到了100w,而单片FPGA的功耗估计得到为20w左右,有点过高了,功耗

2014-08-21 15:31:23

测量 ADC 的真实错误率让客户能够基于不同条件在自己的工作台上测量位错误率提供适用于 TI 低成本 FPGA 平台的固件,还有简单的 GUI 用于监控长时间的错误率

2022-09-22 06:32:27

想要学习低功耗设计,面临的第一个问题就是如何测量休眠时的功耗

正常工作时的电流和休眠时的电流相差太多,用万用表肯定不合适。

请问使用什么设备来测量?

2023-11-02 06:40:26

设计技巧为什么能够节省功耗?降低FPGA功耗的设计技巧有哪些?

2021-04-30 06:04:19

介绍一种基于FPGA技术的时间间隔测量方法,通过分析FPGA的主要技术优势及其在工业控制领域中所处的重要地位,给出设计时间间隔测量模块所选用的FPGA器件并进行硬件设计,以及

2010-12-31 17:29:36 25

25

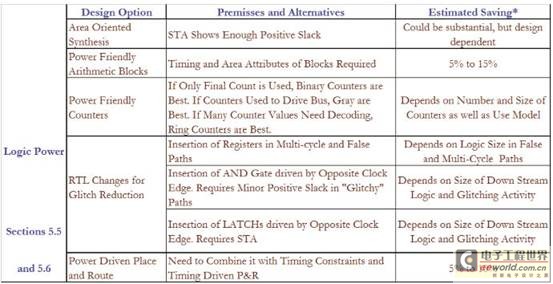

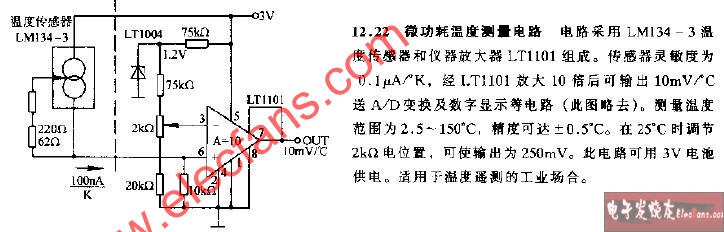

微功耗温度测量电路

2009-02-19 22:20:23 1774

1774

具有低功耗意识的FPGA设计方法

ILGOO系列低功耗FPGA产品

Actel公司的ILGOO系列器件是低功耗FPGA产品,是在便携式产品设计中替代ASIC和CPLD的最

2009-11-26 09:41:19 676

676

便携式产品具有低功耗意识的FPGA设计方法

ILGOO系列低功耗FPGA产品

Actel公司的ILGOO系列器件是低功耗FPGA产品,是在便携式产品设计中替

2009-11-30 09:46:56 674

674

低功耗Cyclone IV FPGA

Altera公司宣布,开始批量发售Cyclone IV FPGA。公司还宣布开始提供基于Cyclone IV GX的收发器入门开发套件。Altera的Cyclone IV FPGA设计用于无线、固网、广播

2010-03-31 10:42:42 1431

1431 FPGA的功耗高度依赖于用户的设计,没有哪种单一的方法能够实现这种功耗的降低,在进行低功耗器件的设计时,人们必须仔细权衡性能、易用性、成本、密度以及功率等诸多指标

2010-07-01 11:08:43 465

465 FPGA的功耗高度依赖于用户的设计,没有哪种单一的方法能够实现这种功耗的降低,如同其它多数事物一样,降低功耗的设计就是一种协调和平衡艺术,在进行低功耗器件的设计时

2010-07-06 11:06:10 981

981 本文将介绍FPGA的功耗、流行的低功耗功能件以及影响功耗的用户选择方案,并探讨近期的低功耗研究,以洞察高功率效率FPGA的未来趋势。

功耗的组成部分

2010-08-27 10:57:21 1637

1637

自从Xilinx推出FPGA二十多年来,研发工作大大提高了FPGA的速度和面积效率,缩小了FPGA与ASIC之间的差距,使FPGA成为实现数字电路的优选平台。今天,功耗日益成为FPGA供应商及其客户关注的问题。降低FPGA功耗是缩减封装和散热成本、提高器件可靠性以及打开移

2011-03-15 14:58:34 31

31 莱迪思半导体公司(NASDAQ: LSCC)近日宣布,即可获取增加至非常成功的LatticeECP3™FPGA系列的低功耗、高速和迷你封装器件。

2012-02-04 09:59:34 783

783 Cyclone V FPGA功耗优势:采用低功耗28nm FPGA活的最低系统功耗(英文资料)

2012-09-05 16:04:11 40

40 白皮书 :采用低成本FPGA实现高效的低功耗PCIe接口 了解一个基于DDR3存储器控制器的真实PCI Express (PCIe) Gen1x4参考设计演示高效的Cyclone V FPGA怎样降低系统总成本,同时实现性能和功耗

2013-02-26 10:04:25 72

72 一种可测量真实放电量的局部放电实验电路

2017-01-22 13:20:25 23

23 测量元器件

2017-03-04 17:53:55 5

5 基于FPGA的低频相位测量系统设计_李宝营

2017-03-19 11:38:26 2

2 CycloneIVFPGA器件系列概述

2017-03-17 14:41:35 7

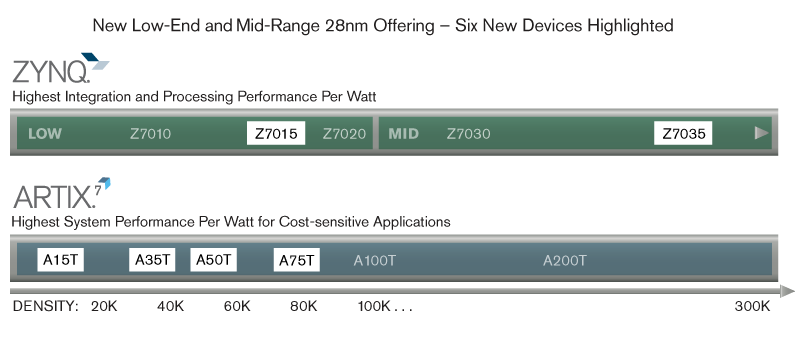

7 赛灵思 Spartan®-7 系列提供了一系列高效、低成本的 FPGA 器件。这些器件经过专门设计,能满足低成本市场的特殊需求。 摘要 Spartan®-7 FPGA 将高性能 28nm 可编程

2017-11-16 15:15:54 8367

8367

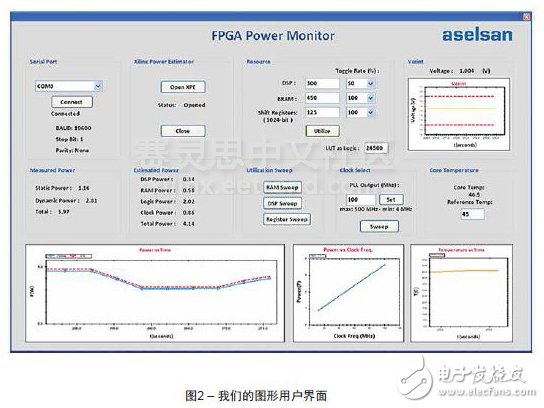

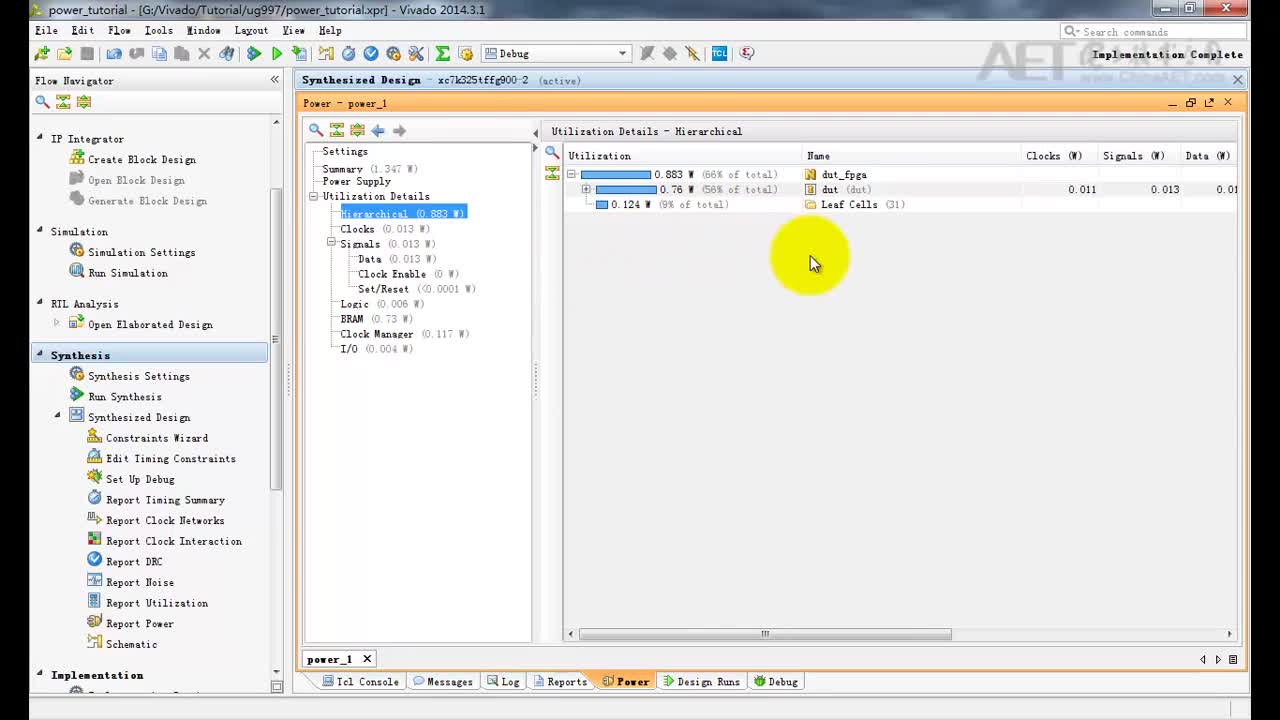

资源、速度和功耗是FPGA设计中的三大关键因素。随着工艺水平的发展和系统性能的提升,低功耗成为一些产品的目标之一。功耗也随之受到越来越多的系统工程师和FPGA工程师的关注。Xilinx新一代开发工具Vivado针对功耗方面有一套完备的方法和策略,本文将介绍如何利用Vivado进行功耗分析和优化。

2017-11-18 03:11:50 4873

4873 为设计寻找“完美”FPGA 的重要性日渐升级,其中功耗已成为主要考虑因素。功耗管理在大部分应用中都非常关键。某些标准已为单卡或者单个系统设定了功耗上限。鉴于此,设计人员必须在设计过程中更早地对功耗

2017-11-22 15:03:01 2573

2573 设计者通过优化自己的设计和注意某些具体情况,可以在FPGA设计中实现低功耗。通过一款具体的FPGA产品了解其低功耗的解决方式,为设计提供了指导。FPGA均可在相应的操作环境下进行仿真,从而了解功耗

2017-11-23 10:37:23 1248

1248 ® FPGA器件,它们在器件、设计和系统层次上的安全特性都比其他领先FPGA制造商更先进。新的数据安全特性现已成为美高森美主流SmartFusion2 SoC FPGA和 IGLOO2 FPGA器件

2018-04-28 15:50:00 880

880 采用赛灵思7系列FPGA满足严格的功耗预算

2018-06-05 13:45:00 3257

3257

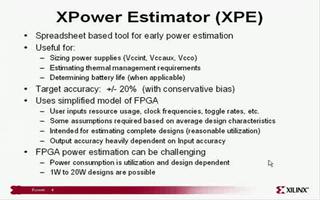

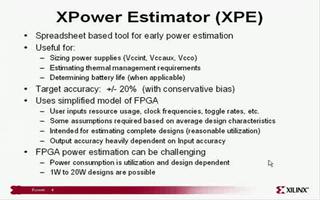

本演示中,我们将介绍利用 XPower 估计器(XPE)工具精确估计 Virtex®-5 器件的功耗所需的步骤。我们还通过在 ML550 开发板 - 进行详细的功耗测量的首选平台 - 上进行测量演示了 Virtex®-5 器件的低功耗特性。

2018-06-06 02:45:00 2951

2951

看看LatticeECP3 FPGA的功耗是多么的低,无论是在实验室中测量,还是利用莱迪思的功耗计算器软件计算。 LatticeECP3是业界最低功耗的配备SERDES的FPGA。

2018-06-15 13:36:00 4990

4990

项目设计初期会选型,工程师根据资源、IO、硬核、IP等选择对应型号的FPGA。功耗部分xilinx提供了XPE表格(Xilinx PowerEstimator),这个XPE支持zynq、目前也有各个系列的器件列表,包括最新的ultrascale + 。

2018-06-27 09:05:00 5224

5224

关键词:FPGA , 低功耗 , RTL 在项目设计初期,基于硬件电源模块的设计考虑,对FPGA设计中的功耗估计是必不可少的。笔者经历过一个项目,整个系统的功耗达到了100w,而单片FPGA的功耗

2018-09-07 14:58:01 381

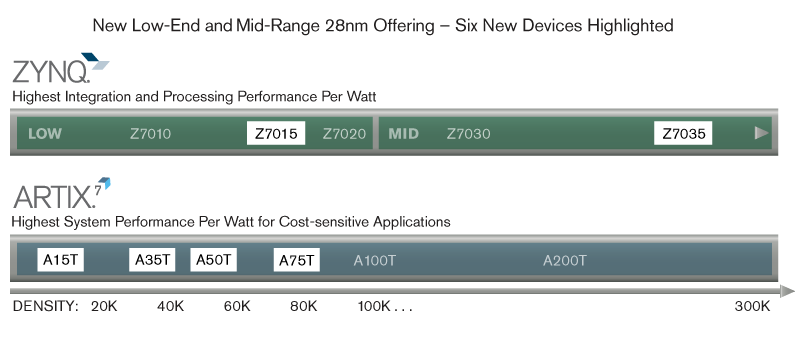

381 持续创新 28HPL 高性能低功耗工艺,成就跨越全新中低端器件,和 Artix-7 FPGA、Kintex-7 FPGA 及 Zynq-7000 SoC 产品系列的全新低功耗工业速度等级的器件敬请

2019-08-01 09:07:32 3066

3066

基站功耗与工作温度也密切相关。通常,工作温度越高,器件的漏电流越大,基站功耗也就越大。

2019-11-08 11:47:04 705

705 在针对大批量应用开发系统时,要考虑的一个重要因素是成本。有多个方面会影响总体拥有成本,而不仅仅是每个元器件的价格。这包括硅片的功耗要求、材料(BOM)总成本、设计和测试系统的工程师的效能等。选择FPGA供应商很重要,要考虑影响系统成本的方方面面,这体现在整个产品设计周期中。

2020-07-17 18:08:34 1718

1718 的功耗高度依赖于用户的设计,没有哪种单一的方法能够实现这种功耗的降低。目前许多终端市场对可编程逻辑器件设计的低功耗要求越来越苛刻。在消费电子领域,OEM希望采用FPGA的设计能够实现与ASIC相匹敌的低功耗。 尽管基于90nm工艺的FPGA的功耗已低

2020-10-28 15:02:13 2498

2498 的功耗高度依赖于用户的设计,没有哪种单一的方法能够实现这种功耗的降低。目前许多终端市场对可编程逻辑器件设计的低功耗要求越来越苛刻。在消费电子领域,OEM希望采用FPGA的设计能够实现与ASIC相匹敌的低功耗。 尽管基于90nm工艺的FPGA的功耗已低

2020-10-26 18:51:16 2583

2583 并不是所有元件都具有相同的静止功耗。根据普遍规则,器件工艺技术尺寸越小,泄漏功耗越大。但并不是所有工艺技术都一样。例如,对于 90 nm 技术来说,Virtex-4 器件与其他 90 nm FPGA 技术之间在静止功耗方面存在显著差异,

2021-01-08 17:46:48 5063

5063 功耗是我们关注的设计焦点之一,优秀的器件设计往往具备低功耗特点。在前两篇文章中,小编对基于Freez技术的低功耗设计以及FPGA低功耗设计有所介绍。为增进大家对低功耗的了解,以及方便大家更好的实现低功耗设计,本文将对FPGA具备的功耗加以详细阐述。如果你对低功耗具有兴趣,不妨继续往下阅读哦。

2021-02-14 17:50:00 6069

6069 与现有的中端FPGA相比,得益于专为低功耗设计的可编程结构、功耗优化的嵌入式存储器和DSP、低功耗高性能SERDES与I/O设计、内置协议逻辑等全方位优化措施,Avant系列产品的功耗比同类竞品器件低2.5倍。

2023-01-04 11:32:11 342

342 选择FPGA器件厂商、器件系列、工具集等,很大程度上还是要考虑设计团队成员的设计经历和偏好。话说“就熟不就生”,因为这在很大程度上会决定了设计复杂性高低和项目进度周期的快慢。当然了,其它因素诸如成本、资源、功耗、可移植、可升级等等也是需要考量的。总而言之,这也是一个需要综合考虑的权衡决策。

2023-02-13 11:26:18 514

514 点击上方 蓝字 关注我们 FPGA 高级设计之实现功耗优化 与ASICs(Application Specific Integrated Circuits)比较,相似的逻辑功能,用FPGA来实现

2023-05-19 13:50:02 815

815 摘要:莱迪思(Lattice )半导体公司在这应用领域已经推出两款低成本带有SERDES的 FPGA器件系列基础上,日前又推出采用富士通公司先进的低功耗工艺,目前业界首款最低功耗与价格并拥有SERDES 功能的FPGA器件――中档的、采用65nm工艺技术的 LatticeECP3系列。

2023-10-27 16:54:24 237

237 双脉冲测试的基本原理是什么?双脉冲测试可以获得器件哪些真实参数? 双脉冲测试是一种常用的测试方法,用于测量和评估各种器件的性能和特性。它基于一种简单而有效的原理,通过发送两个脉冲信号并分析其响应

2024-02-18 09:29:23 234

234

电子发烧友App

电子发烧友App

评论