电源管理一直是FPGA设计中的关键问题。现有一种新方法可用于测量真实FPGA器件的功耗估计值

现代的FPGA 芯片能够开发高性能应用,但在这些设计中电源管理通常是一大限制因素。FPGA 器件的资源使用最能决定设计的容量和处理速度,但是增加资源就会提高功耗。更高的功耗会提高运行成本、面积要求和结温,而设计人员必须用更多的气流和冷却系统来解决结温问题。

由于开发板或系统的总功耗极其重要,因此设计人员必须设置一个功耗预算,在资源使用和功耗问题方面兼顾平衡。所以,事先预测系统潜在功耗的能力可帮助设计人员获得先发优势。

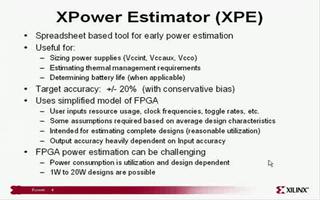

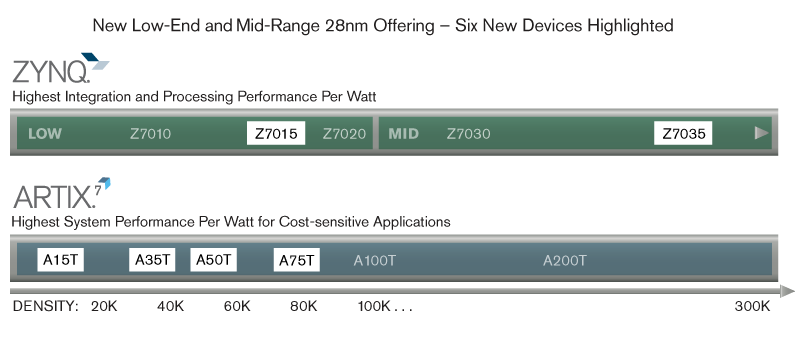

对于实现前的功耗评估,赛灵思可提供一些工具根据用户输入内容或综合报告进行功耗估计。其中一款工具就是赛灵思功耗估计器(Power Estimator,XPE)电子数据表。这款基于Excel 的功耗估计工具能让您输入资源使用、翻转率和时钟频率等设计属性,并根据器件信息计算估计的功耗值。另一款常用的工具是赛灵思功耗分析器(Power Analyzer,XPA)。在布局和布线后,XPA 会导入已生成的NCD 文件,并利用实现详细信息和仿真结果(而非用户输入)来更加准确地估计功耗。

作为备选方案,我们设计出一种新方法来测量真实器件上FPGA 设计的功耗估计值。为模拟不同的实现方案,我们创建了一个独立于器件的通用VHDL 设计,其有可能实现在FPGA 运行时通过串行通道改变激活的资源(即DSP slice、Block RAM 和slice 寄存器)的数量及相应的运行条件(结温、时钟频率和翻转率)。 我们的这种技术可以同时监控电源的电流和电压大小,便于我们轻松观察器件在不同资源使用和环境条件下的动态功耗特性。

我们已在赛灵思KC702 评估板上实现了该设计。不过,只要您的FPGA 器件支持设计中所使用的IP核,您只需做轻微修改也可在任何其它器件上实现该设计。

另一种使用该技术的方法可能是作为面向FPGA 板的VHDL 测试设计。我们假设最近设计了一个通用型Kintex®-7 开发板。客户可在不断变化的环境条件下利用未知的资源容量在开发板上实现任何设计。为了确保开发板的稳定性和稳健性,我们需要在最高和最低所需的环境温度下强加器件的工作极限,并验证FPGA 能够支持不同的资源使用情况。然而,测试每种资源使用方案需要从头开始开发一款全新的VHDL 设计,这会耗费太多时间。我们推荐的方法可帮助设计人员灵活地根据需要对测试设计进行实时控制。

实现细节

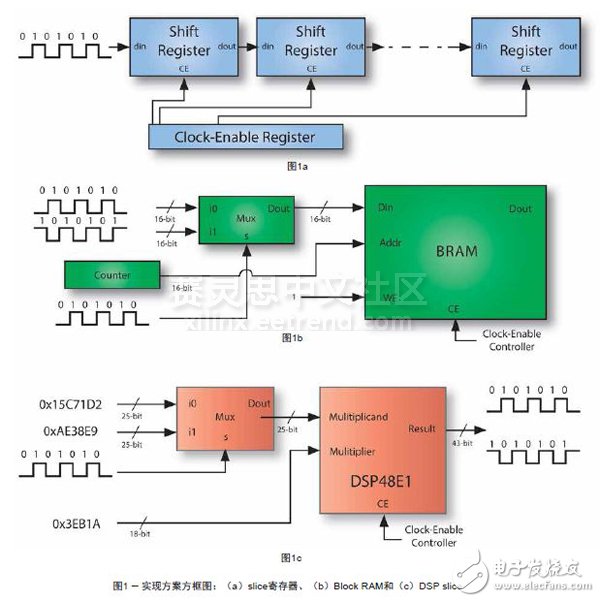

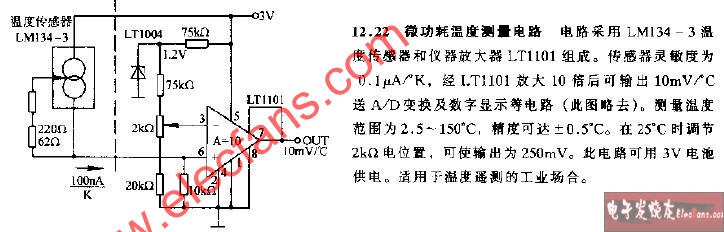

我们设法让实现方案尽可能的简单,以避免生成作为逻辑使用的s l i c e LUT,因为我们无法对其功耗进行控制。实现slice 寄存器最简单的方法是将它们组合为移位寄存器模块。图1a中的方框图给出了slice 寄存器的实现方法。 这里需要注意一个简单的问题,当我们尝试创建slice 寄存器时,综合工具常常将slice LUT 作为32 位移位寄存器(SRL32)使用,而不是使用slice 寄存器。您也可以利用以下VHDL 属性来强制综合软件使用slice寄存器:

LogiCORETM 模块存储器生成器创建作为单端口RAM 的Block RAM。将一个数位持续翻转的16 位字不停写入激活BRAM 的随机地址中,从而使它们保持被占用状态。图1b 是单个BRAM 组件的方框图。同样,我们使用DSP slice 将一个25位被乘数与一个18 位乘数相乘,得到一个43 位输出, 这就是单个DSP48E1 可以处理的最大字宽。所有DSP 组件的被乘数会被定期修改,从而使DSP 消耗动态功耗,如图1c 所示。然而,综合工具试图在综合过程中删除资源,因为这些模块的输出未与任何输出引脚连接。您可以使用以下属性使资源保持不变:

在该方案中,您可通过控制时钟使能信号来激活资源。时钟禁用后的资源只消耗非常小的功耗,可在设计中忽略不计。具体来说,具有100%翻转率的50 个DSP slice 的功耗为0.112 瓦,而当它们的时钟使能信号取消断言时功耗为0.001 瓦。不同使用率下的结果几乎相同。因此,每个资源组件都由时钟使能信号通过串行通信进行控制的设计无需采用新的设计和实现步骤即可立即仿真出改变使用率时的情况。

资源的平均翻转率是显著影响功耗的重要因素。翻转率是指特定资源在每个时钟周期内输出信号的跳变次数。您可以交替改变资源的输入以使输出在每个周期都改变其状态,从而实现恒定的100% 翻转率。例如,要调整DSP slice 的翻转率,您可以选择两个被乘数(连续交替)和一个乘数,这样输出的每位在每个周期中都会发生变化。输入信号的交替速率决定资源的翻转率;因此,我们通过串行通道就能即时控制某个资源类型的翻转率。

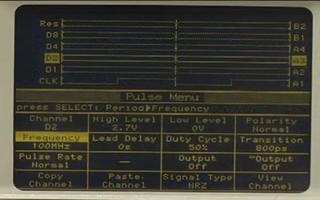

此外,功耗还与时钟频率直接成正比。我们使用混合模式时钟管理器(MMCM)生成具有可变频率的时钟。MMCM 输出的频率、相位和占空比由一组寄存器决定,而且一般只当实现设计和生成bit 流文件时才进行初始化。然而,MMCM 的动态重配置端口使我们能在FPGA 运行时改变输出时钟等特性。时钟的相位和占空比不在考虑范围内,因为相位并不影响功耗,而占空比在大多数情况下也并不会改变。

另一方面,频率与功耗高度相关。MMCM 的内部工作机理是,VCO 频率由CLKOUT0_DIVIDE 寄存器的值进行分频,以获得所需的输出频率。我们根据赛灵思应用指南XAPP888 中介绍的状态机算法为寄存器赋予新值,实现无毛刺转换。与此同时,我们根据图形用户界面(GUI)中的用户输入实时改变设计的时钟频率。然后,我们能方便地观察不同频率下设计的功耗特性。

高温条件下的功耗行为是另一项需要认真观察和验证的重要问题。芯片的内核温度取决于开发板设计、处理速度、环境温度、散热片和风扇的气流。在我们的设计中,我们利用简单的PWM 开关控制器改变位于FPGA 芯片顶部的风扇的速度,从而局部地控制结温。此外,您也可以使用热风枪等外部加热工具来缩短加热时间。

用片上传感器测量内核温度,并通过LogiCORE XADC 向导生成模数转换器XADC。当您在GUI 中输入参考温度值时,GUI 通过串行通道将参考值发送到器件,并与片上传感器测量到的内核温度进行比较。通过控制风扇的速度将结温稳定在所需的水平上。这样,您就可以观察功耗情况并绘制与内核温度的走势图,从而验证是否满足设计的功耗预算,以及功耗在所需的加热特性下是否保持在关键限值以内。

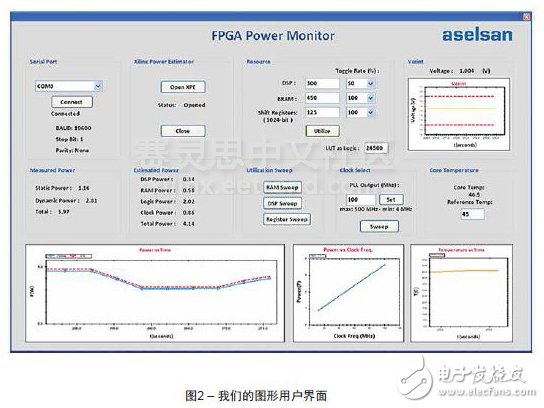

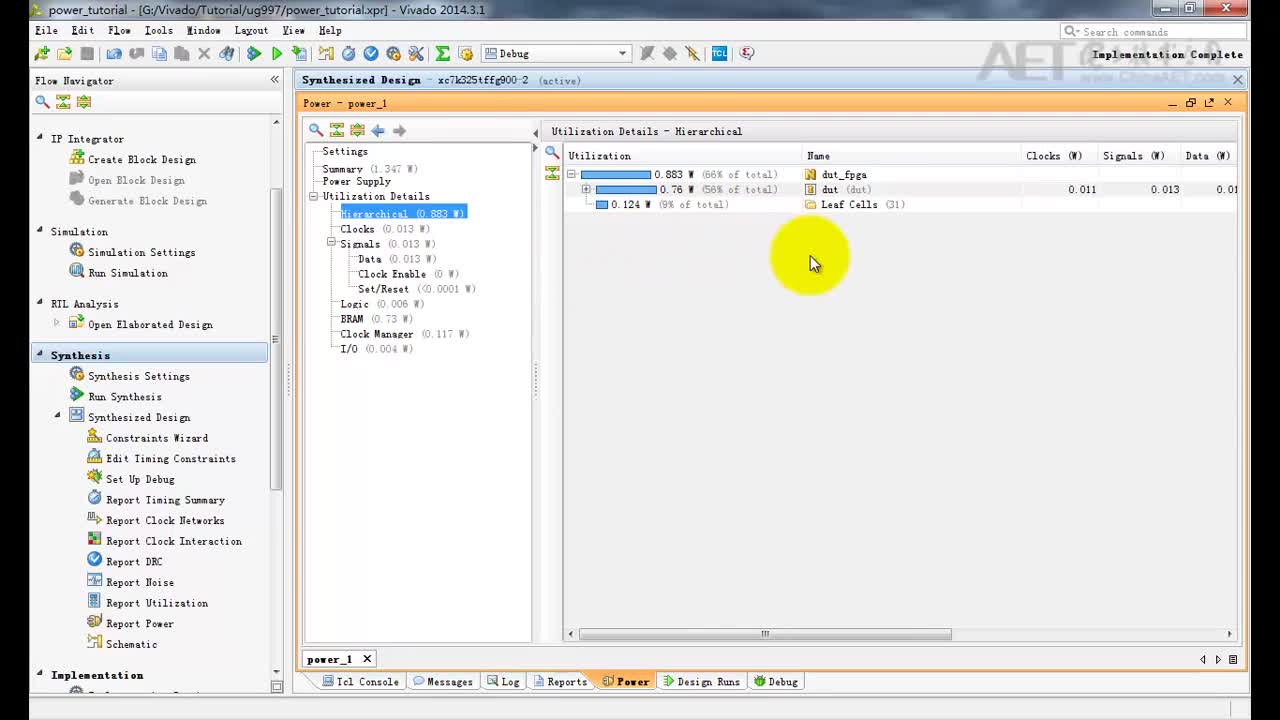

图形用户界面可用来与FPGA 器件通信,以改变上述参数。图2 给出了GUI 的屏幕截图。我们首先通过标准UART 利用其中一个可用端口连接到器件。然后,我们打开赛灵思功耗估计器将估计值与测量值进行比较。GUI 立即为使用默认参数值的估计功耗和实际功耗绘制功耗与时间关系图。您可在相关面板中修改这些参数,并在资源(Resource)面板中利用翻转率指定所用的slice 资源数量。使用扫描(Utilization Sweep)面板在等间隔下从0% 至100% 扫描特定资源的使用率,并利用每个间隔的测量功耗值绘制功耗与使用率关系图。

同样,您可在时钟选择(Clock Select)面板中改变MMCM 的输出并扫描时钟频率。在下一栏的Vccint 面板中可测量和连续绘制出FPGA 芯片的电源电压。同时,内核温度(Core Temperature)面板显示并绘制出内核温度。用户可在提供的对话框中输入参考温度以改变结温。

您可利用集成在KC702 开发板上的德州仪器(Texas Instruments)UCD9248 数字PWM 系统控制器测量电源的电压和电流电平。这种用于电源转换器的多轨和多相位PWM 控制器支持电源管理总线(PMBus)通信协议。其PWM 信号可驱动用于调节Vccint 电源电压的UCD7242 集成电路。一组PMBus 命令可用于配置IC功能。UCD7242 包含片上电压与电流感应电路,并与UCD9248 进行通信。我们的GUI 软件不断向该器件发送相应的PMBus 命令,同时接收标准PMBus 数据格式的DC/DC 转换器的电压和电流值。然后,我们将收到的字节转换为实际数值,并获得电源的电压和电流电平。

在高温下运行复杂、拥塞的设计可能会扰乱电源电压电平。不幸的是,FPGA 芯片对于输入电压的容差范围较小。超过该电平范围会导致芯片上的功能失效或者永久损坏。因此,您在设计完开发板后,还需要测试严苛工作条件下电压电平的稳定性。Vccint 面板可用来观察和验证设计开发板的电源系统是否能够承受高温下进行高速处理时的电压变化。

设计人员需要始终谨记的重要一点是:由于制造工艺变化,每个器件都会有不同的功耗。例如,在Virtex-7 FPGA 芯片制造完成后,会在测试阶段确定足够让芯片正确运行的最小电压源电平并写入电熔丝。将稳压器输出调节至这个最小电压电平可以改变静态功耗。因此,静态功耗的偏移会导致XPE 与我们的设计在结果上出现差异。例如,XPE 中估计的Kintex-7 芯片的静态功耗在典型情况与最差情况时计算相差0.7 瓦。

完美匹配XPE

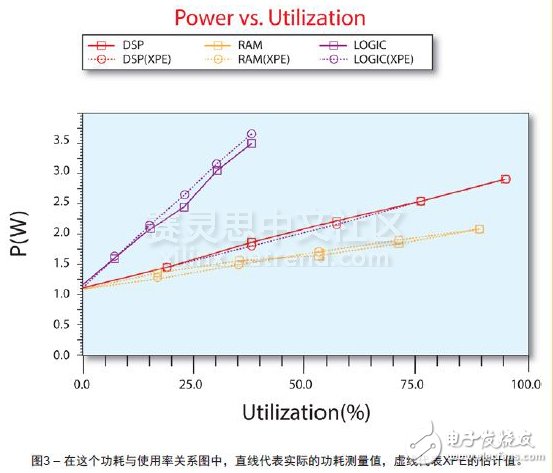

我们在很多具有可变因素的不同设计方案中对我们的设计进行了测试,以确保其精确性和可靠性。同时,还在测量值的示意图中绘出XPE 的估计结果,从而将功耗估计值与实际测量值进行比较。

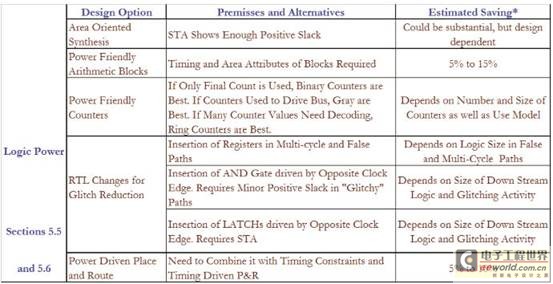

通过最初将资源使用率从零至设计最大值扫描的设计实现可观察Kintex-7 器件的功耗行为。图3 给出了扫描一种资源类型的使用率过程中功耗的变化情况。直线和虚线分别代表实际功耗测量值和XPE 的估计值。我们可以看到即使在使用率和功耗处于高值时两条曲线依然靠得非常紧密。

这些结果表明赛灵思功耗估计器计算值与实际测量值一致,可以准确地预测功耗。此外,我们还可以断定我们推荐的方法能够起到预期效果,并且可以作为XPE 的替代方案。更好的选择是将两种方法结合使用。同时采用XPE 和我们的方法来测试设计可对结果进行双重检查,确保您在XPE中修改数字时不会犯任何错误。例如,如果您没有在XPE 中正确输入时钟的平均扇出数字,或者误解了一个概念并错误填写对话框,那么得到的示意图就无法重合,即表明有错误存在,这样您就可以校正输入值,防止出现误导性的估算结果。

FPGA 开发板的额定规范,例如最大功耗或允许的内核温度范围,总是包含在开发板的数据手册中。不过,具有较高资源使用率和时钟频率的设计会超出这些额定值。因此,必须确认功率调节器能为器件提供足够的电流,而且散热系统足以将温度保持在FPGA 设计的临界值以内。我们的方法可通过增加资源使用和时钟频率来测试开发板的可靠性能否满足高性能要求。这种测试有助于确定开发板上实现的设计所具备的最高信号处理速率。此外,我们还可以了解是否需要升级开发板的功能和系统的冷却机制。

测试结果表明了我们的方法能够可靠地控制资源使用和评估功耗,因此工程师在设计前期阶段就多了一种电源管理选项。在采取进一步功能改进后,例如增加JTAG 接口、完全独立于器件的VHDL 代码以及通用的电流感应系统,这项设计将会成为FPGA 项目的关键工具。

电子发烧友App

电子发烧友App

评论