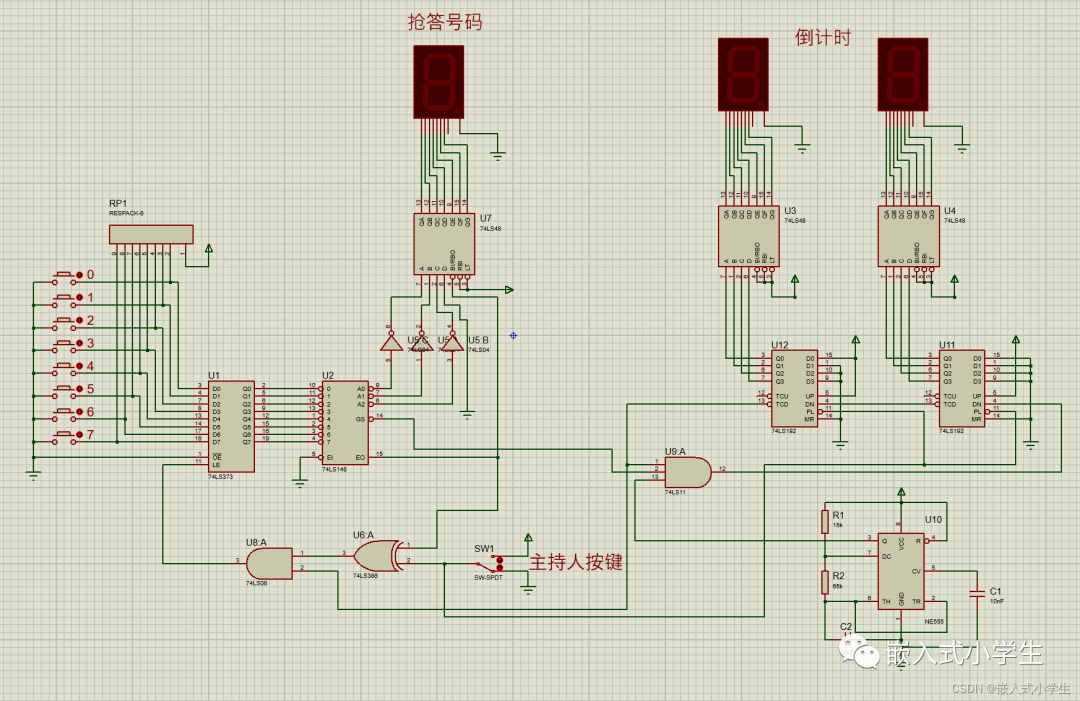

VHDL语言设计四人抢答器方案二

设计任务及要求:

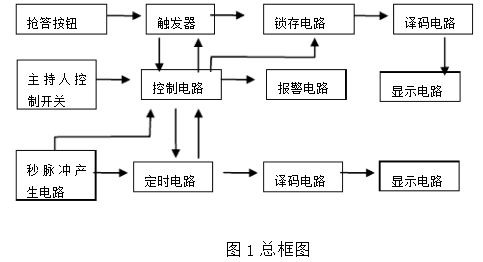

(1)设计用于竞赛抢答的四人抢答器;

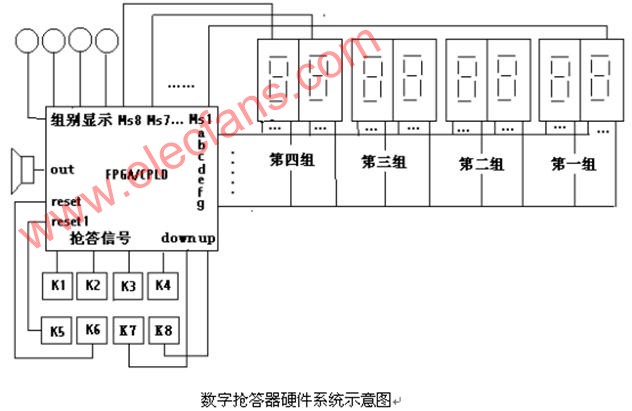

①有多路抢答,抢答台数为8;

②具有抢答开始后20秒倒计时,20秒倒计时后无人抢答显示超时,并报警;

③能显示超前抢答台号并显示犯规警报;

(2)系统复位后进入抢答状态,当有一路抢答按键按下,该路抢答信号将其余各路抢答信号封锁,同时铃声想起,直至该路按键松开,显示牌显示该路抢答台号;

(3)用VHDL语言设计符合上述功能要求的四人抢答器,并用层次化设计方法设计该电路;

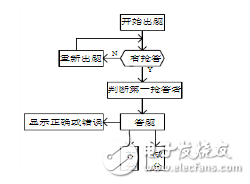

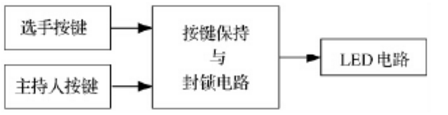

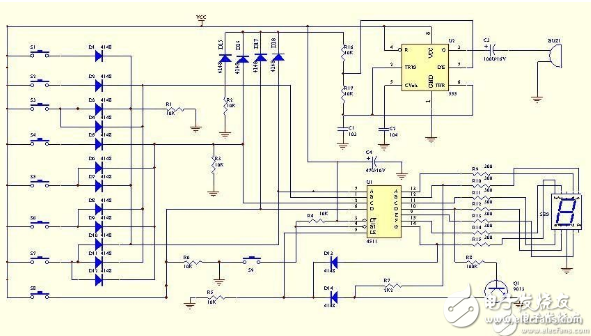

设计思路

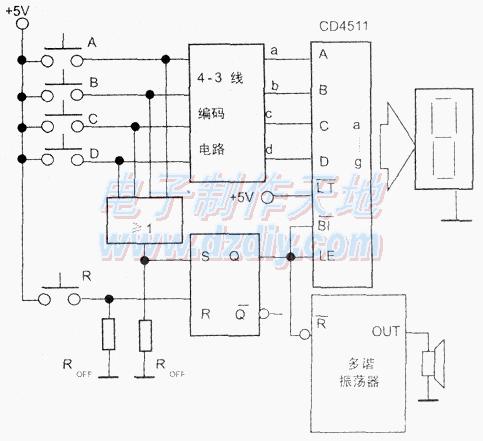

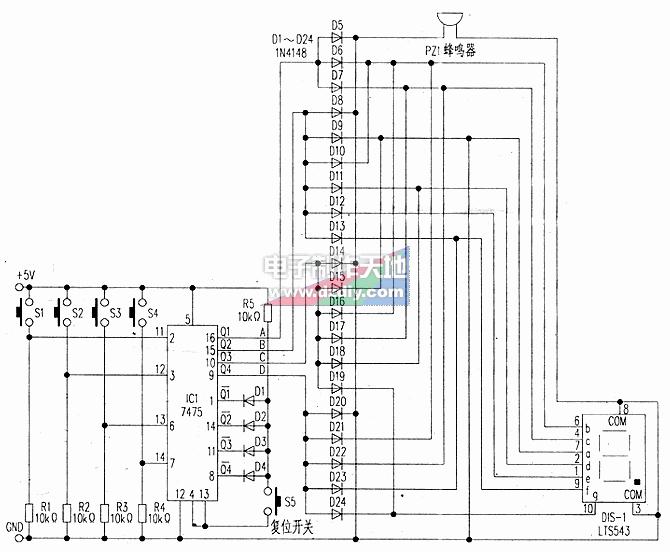

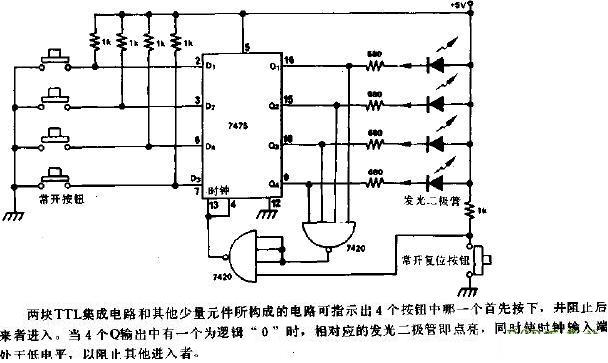

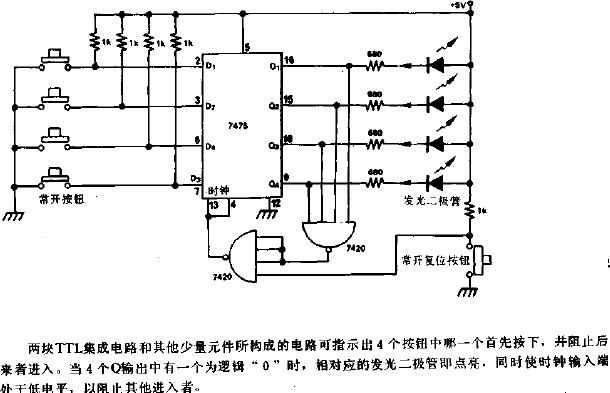

设计制作一个竞赛抢答器,每组受控于一个抢答开关,分别为S1,S2,S3,S4,低电平表示抢答有效;设置主持人控制键K,用于控制整个系统清0和抢答有效控制,按下复位键时,K=0,系统清零;抬起复位键时,K=1,抢答开始;系统具有第一抢答信号鉴别和锁存功能。在主持人将系统复位并使抢答有效开始后,第一抢答者按下抢答按钮,对应的输入引脚接低电位0,电路应记忆下第一抢答者的组别,并封锁其他各组的按钮,即其他任何一组按键都不会使电路响应;系统以两种方式指示第一抢答者:其一是通过译码程序显示其组别号;其二是在第一抢答者产生时,蜂鸣器警示;设置违规电路单元,当抢答者在主持人按下复位清零按钮之前就已经按下抢答按钮时,则给出违规信号为高电平。对应组别的红色信号灯亮;当20秒倒计时后无人抢答显示超时,并报警。

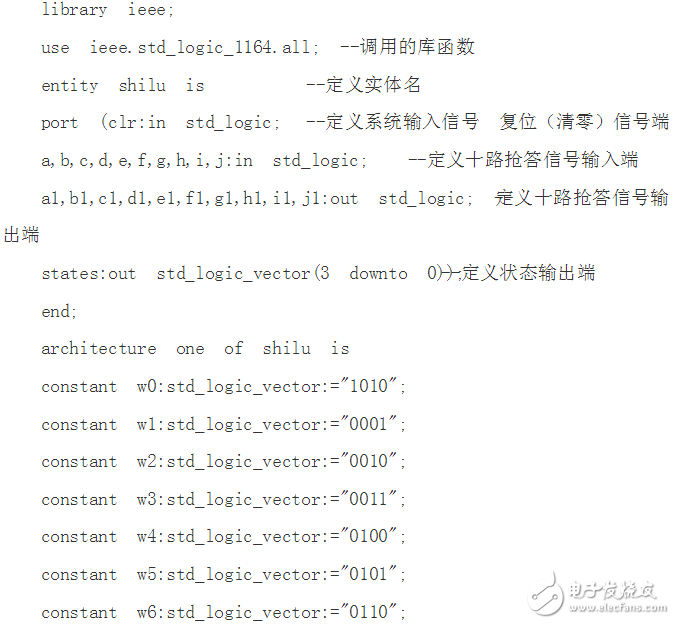

VHDL程序实现

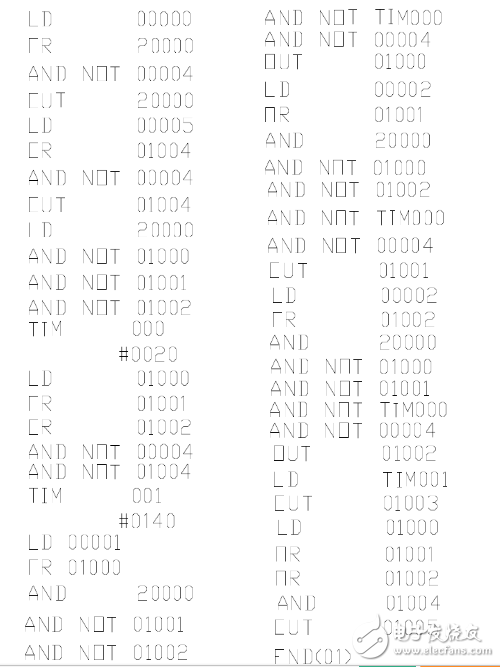

1、正常抢答程序

此模块包括正常抢答第一信号鉴别和显示抢答台号,并发生声音提示。其中S1,S2,S3,S4为抢答按钮,当对应的按钮信号为0时表示有抢答信号;K为主持人按钮,按下复位键K时, K=0,系统清零;抬起复位键时,K=1,抢答开始;G为报警信号。其VHDL源程序如下:

library ieee;

use ieee.std_logic_1164.all;

use ieee. std_logic_arith.all;

use ieee. std_logic_unsigned.all;

--------------------------------------------------------------------

entity qiangda is

port( S1,S2,S3,S4 : in std_logic; --输入:表示4个人,为0表示有抢答

K : in std_logic; --主持人抢答开始键

G : out std_logic; --报警信号

ledag : out std_logic_vector (6 downto 0);

Dout : out std_logic_vector(3 downto 0) ); --抢答结果显示

end qiangda;

--------------------------------------------------------------------

architecture behave of qiangda is

signal Enable_Flag : std_logic;--允许抢答控制变量,为1表示允许抢答

signal S : std_logic_vector(3 downto 0);

signal D : std_logic_vector(3 downto 0);

begin

process(S1,S2,S3,S4,K) --允许抢答控制

begin

S<=S1&S2&S3&S4;

If (K=‘1’) then

Enable_Flag<=‘1’;

elsif(S/=“1111”) then

Enable_Flag<=‘0’;

end if;

end process;

process(S1,S2,S3,S4,K) --抢答结果显示

begin

if(K=‘0’) then

D<=“0000”;

Elsif (Enable_Flag=‘1’) then

if(S1=‘0’) then

D(0)<=‘1’;

G<=‘0’;

elsif(S2=‘0’) then

D(1)<=‘1’;

G<=‘0’;

elsif(S3=‘0’) then

D(2)<=‘1’;

G<=‘0’;

elsif(S4=‘0’) then

D(3)<=‘1’;

G<=‘0’;

end if;

dout<=d;

end if;

end process;

process(d) --显示抢答成功者号码

begin

case d is

when “0000”=>ledag<=“0111111”;

when “0001”=>ledag<=“0000110”;

when “0010”=>ledag<=“1011011”;

when “0100”=>ledag<=“1001111”;

when “1000”=>ledag<=“1100110”;

when others=>ledag<=“0000000”;

end case;

end process;

end behave;

2、抢答倒计时程序

此模块为抢答20s倒计时程序,在主持人按下按钮K后此模块即开始工作,在20s倒计时完后会有声音提示,G为声音报警信号。

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY COUNT IS

PORT (CLK, Enable_Flag: IN STD_LOGIC;

H,L: OUT STD_LOGIC_VECTOR (3 DOWNTO 0);

G:OUT STD_LOGIC); --声音报警

END COUNT;

ARCHITECTURE COUNT_ARC OF COUNT IS

BEGIN

PROCESS (CLK, Enable_Flag)

VARIABLE HH, LL: STD_LOGIC_VECTOR (3 DOWNTO 0);

BEGIN

IF CLK‘EVENT AND CLK=’1‘THEN

IF Enable_Flag=’1‘THEN

IF LL=0 AND HH=0 THEN

G<=’1‘;

ELSIF LL=0 THEN

LL: =“1001”;

HH: =HH-1;

ELSE

LL: =LL-1;

END IF;

ELSE

G<=’0‘;

HH: =“1001”;

LL: =“1001”;

END IF;

END IF;

H<=HH;

L<=LL;

END PROCESS;

END COUNT_ARC;

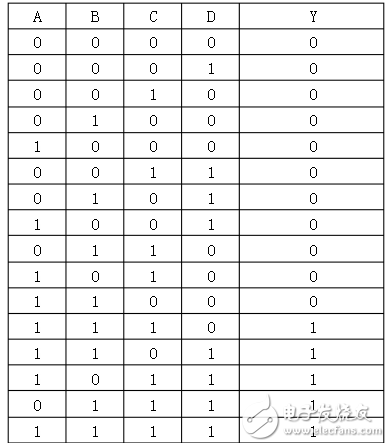

3、超前犯规抢答程序

此模块为违规电路。当抢答者在主持人复位系统之前就已按下抢答按钮,即当RESET=0时,有抢答信号出现,则Y=11表示某组违规,当RESET = 1时,显示违规组别。其中K为主持人按钮,S1,S2,S3,S4为抢答按钮,R1,R2,R3,R4为对应组别犯规红色显示灯。其VHDL源程序如下:

LIBRARY ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

ENTITY wg IS

PORT(K: IN std_logic;

S1, S2, S3, S4: IN std_logic;

R1, R2, R3, R4: OUT std_logic; --红色灯指示超前抢答台号

y: OUT std_logic_VECTOR (1 DOWNTO 0) );

END wg;

ARCHITECTURE a OF wg IS

SIGNAL TEMP1: STD_LOGIC;

SIGNAL TEMP2: STD_LOGIC_VECTOR (1 DOWNTO 0);

BEGIN

TEMP1<=S1 OR S2 OR S3 OR S4 ;

TEMP2<=K&TEMP1;

process(TEMP2) --显示抢答成功者号码

begin

case TEMP2 is

when “01”=>Y<=“11”;

when “10”=>Y<=“00”;

when “11”=>Y<=“00”;

when others=>Y<=“00”;

end case;

if(K<=‘0’) then

if(S1=‘0’) then

R1<=‘0’;

elsif(S2=‘0’) then

R2<=‘0’;

elsif(S3=‘0’) then

R3<=‘0’;

elsif(S4=‘0’) then

R4<=‘0’;

end if;

end if;

end process;

电子发烧友App

电子发烧友App

评论