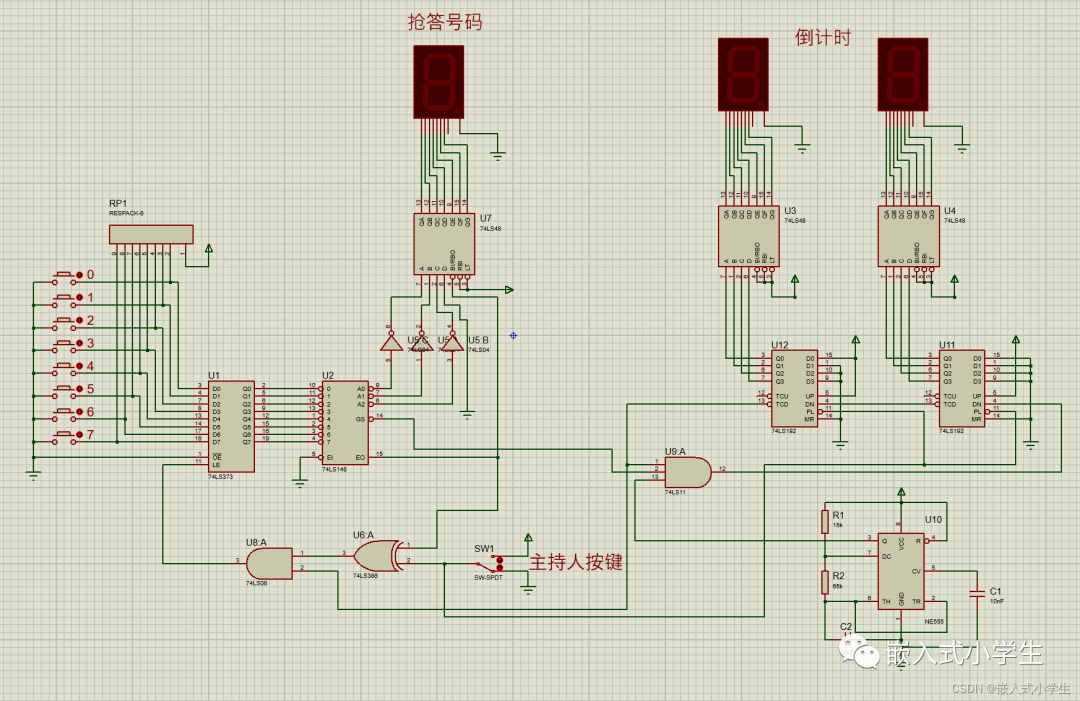

VHDL语言设计四人抢答器方案三

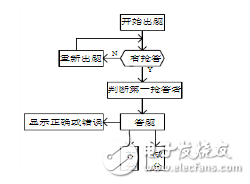

问题描述

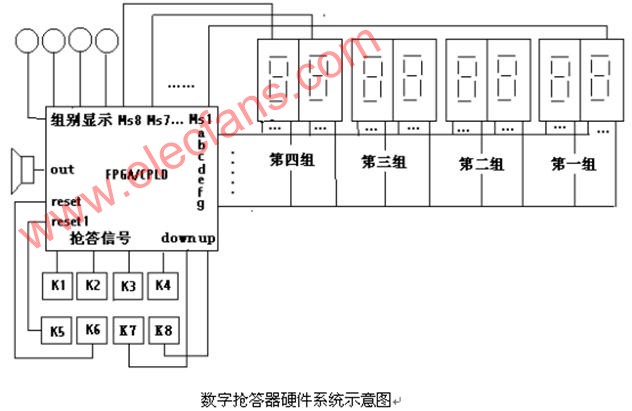

设计一个4人参加的智力竞赛抢答计时器。电路具有回答问题时间控制功能。要求回答问题时间小于等于100妙(显示为0~99),时间显示采用倒计时方式。当达到限定时间时,发出声响以示警告;当有某一参赛者首先按下抢答开关时,相应显示灯亮并伴有声响,此时抢答器不再接受其他输入信号。

功能要求

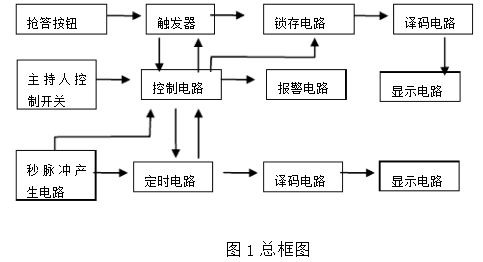

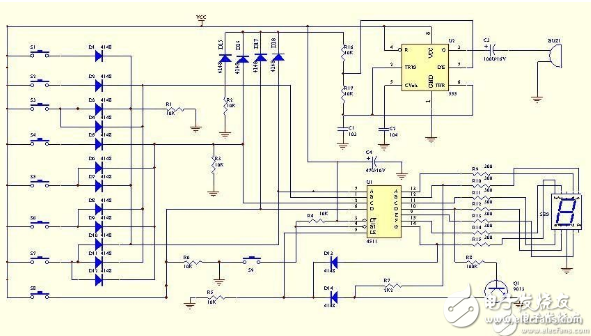

1、用feng模块将选手按下按键信号输出高电平给锁存模块lockb,进行锁存的同时发出aim信号实现声音提示,并使count模块进行答题时间的倒计时,在计满100妙后送出声音提示;

2、用ch41a模块将抢答结果转换为二进制数;

3、用sel模块产生数码管片选信号;

4、用ch42a模块将对应数码管片选信号,送出需要的显示信号;

5、用七段译码器dispa模块进行译码。

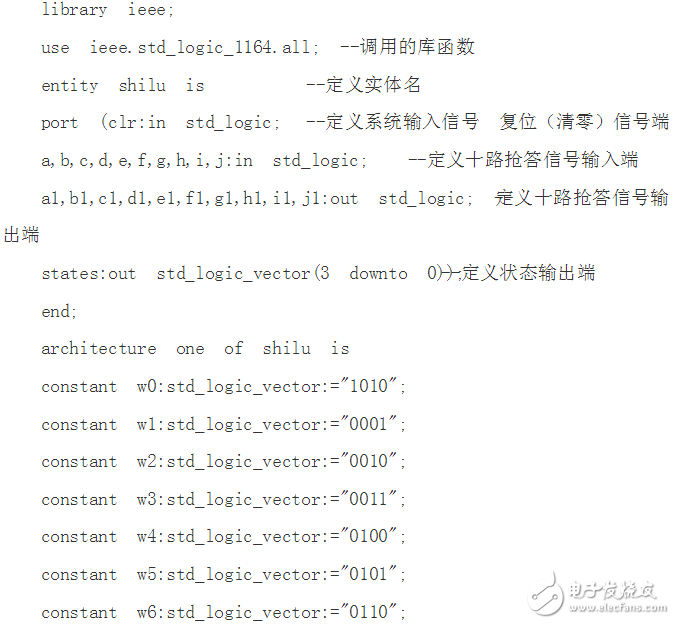

各模块VHDL源代码

1、抢答鉴别模块FENG的VHDL源程序

--feng.vhd

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY FENG IS

PORT(CP,CLR:IN STD_LOGIC;

Q :OUT STD_LOGIC);

END FENG;

ARCHITECTURE FENG_ARC OF FENG IS

BEGIN

PROCESS(CP,CLR)

BEGIN

IF CLR=‘0’THEN

Q<=‘0’;

ELSIF CP‘EVENT AND CP=’0‘THEN

Q<=’1‘;

END IF;

END PROCESS;

END FENG_ARC;

2、片选信号产生模块SEL的VHDL源程序

--sel.vhd

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY SEL IS

PORT(CLK:IN STD_LOGIC;

a:OUT INTEGER RANGE 0 TO 7);

END SEL;

ARCHITECTURE SEL_ARC OF SEL IS 片选信号产生模块SEL

BEGIN

PROCESS(CLK)

VARIABLE AA:INTEGER RANGE 0 TO 7;

BEGIN

IF CLK’EVENT AND CLK=‘1’THEN

AA:=AA+1;

END IF;

A<=AA;

END PROCESS;

END SEL_ARC;

3、锁存器模块LOCKB的VHDL源程序

-lockb.vhd

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY LOCKB IS

PORT(D1,D2,D3,D4:IN STD_LOGIC;

CLK,CLR:IN STD_LOGIC;

Q1,Q2,Q3,Q4,ALM:OUT STD_LOGIC);

END LOCKB;

ARCHITECTURE LOCK_ARC OF LOCKB IS

BEGIN

PROCESS(CLK)

BEGIN

IF CLR=‘0’THEN

Q1<=‘0’;

Q2<=‘0’;

Q3<=‘0’;

Q4<=‘0’;

ALM<=‘0’; 模块LOCKB

ELSIF CLK‘EVENT AND CLK=’1‘THEN

Q1<=D1;

Q2<=D2;

Q3<=D3;

Q4<=D4;

ALM<=’1‘;

END IF;

END PROCESS;

END LOCK_ARC;

4、转换模块CH41A的VHDL源程序

--ch41a..vhd

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY CH41A IS

PORT(D1,D2,D3,D4:IN STD_LOGIC;

Q:OUT STD_LOGIC_VECTOR(3 DOWNTO 0));

END CH41A;

ARCHITECTURE CH41_ARC OF CH41A IS 转换模块CH41A

BEGIN

PROCESS(D1,D2,D3,D4)

VARIABLE TMP:STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

TMP:=D1&D2&D3&D4;

CASE TMP IS

WHEN “0111”=>Q<=“0001”;

WHEN “1011”=>Q<=“0010”;

WHEN “1101”=>Q<=“0011”;

WHEN “1110”=>Q<=“0100”;

WHEN OTHERS=>Q<=“1111”;

END CASE;

END PROCESS;

END CH41_ARC;

5、3选1模块CH31A的VHDL源程序

--ch31a.vhd

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY CH31A IS

PORT(SEL:IN STD_LOGIC_VECTOR(2 DOWNTO 0);

D1,D2,D3:IN STD_LOGIC_VECTOR(3 DOWNTO 0);

Q : OUT STD_LOGIC_VECTOR(3 DOWNTO 0));

END CH31A;

ARCHITECTURE CH31_ARC OF CH31A IS

BEGIN

PROCESS(SEL,D1,D2,D3)

BEGIN

CASE SEL IS

WHEN “000”=>Q<=D1;

WHEN “001”=>Q<=D2;

WHEN “111”=>Q<=D3;

WHEN OTHERS=>Q<=“1111”;

END CASE;

END PROCESS;

END CH31_ARC;

6、倒计时模块COUNT的VHDL源程序

倒计时模块COUNT如图16-7所示,该模块实现答题时间的倒计时,在计满100s后送出声音提示。

--count.vhd

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY COUNT IS

PORT(CLK,EN:IN STD_LOGIC; 倒计时 模块COUNT

H,L:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

SOUND:OUT STD_LOGIC);

END COUNT;

ARCHITECTURE COUNT_ARC OF COUNT IS

BEGIN

PROCESS(CLK,EN)

VARIABLE HH,LL:STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

IF CLK’EVENT AND CLK=‘1’THEN

IF EN=‘1’THEN

IF LL=0 AND HH=0 THEN

SOUND<=‘1’;

ELSIF LL=0 THEN

LL:=“1001”;

HH:=HH-1;

ELSE

LL:=LL-1;

END IF;

ELSE

SOUND<=‘0’;

HH:=“1001”;

LL:=“1001”;

END IF;

END IF;

H<=HH;

L<=LL;

END PROCESS;

END COUNT_ARC;

7、显示译码模块DISP的VHDL源程序

--disp.vhd

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY DISP IS 显示译码模块DISP

PORT(D:IN STD_LOGIC_VECTOR(3 DOWNTO 0);

Q:OUT STD_LOGIC_VECTOR(6 DOWNTO 0));

END DISP;

ARCHITECTURE DISP_ARC OF DISP IS

BEGIN

PROCESS(D)

BEGIN

CASE D IS

WHEN“0000”=>Q<=“0111111”;

WHEN“0001”=>Q<=“0000110”;

WHEN“0010”=>Q<=“1011011”;

WHEN“0011”=>Q<=“1001111”;

WHEN“0100”=>Q<=“1100110”;

WHEN“0101”=>Q<=“1101101”;

WHEN“0110”=>Q<=“1111101”;

WHEN“0111”=>Q<=“0100111”;

WHEN“1000”=>Q<=“1111111”;

WHEN“1001”=>Q<=“1101111”;

WHEN OTHERS=>Q<=“0000000”;

END CASE;

END PROCESS;

END DISP_ARC;

电子发烧友App

电子发烧友App

评论