滤波器和接口设计程序 - ADI实验室电路:带抗混叠滤波器的宽带接收机

2012年12月14日 14:16 来源:ADI 作者:秩名 我要评论(0)

本部分说明放大器/ADC与滤波器的接口设计的一般方法。为了实现最佳性能(带宽、SNR、SFDR等),必须考虑放大器和ADC对该一般电路的一些设计限制:

放大器应具有数据手册针对最佳性能而推荐的合适直流负载。

放大器与滤波器提供的负载之间必须使用大小合适的串联电阻,这是为了防止通带中出现不合需要的峰化现象。

ADC的输入应通过外部并联电阻降低,并且应使用合适的串联电阻将ADC与滤波器隔离。此串联电阻也能降低峰化。

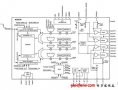

图5所示的一般化电路适用于大多数高速差分放大器/ADC接口,将用作讨论的基础。这种设计方法利用多数高速ADC相对较高的输入阻抗和驱动源(放大器)相对较低的阻抗,通常可以最大程度地降低滤波器的插入损耗。

基本设计流程如下:

选择ADC外部端接电阻RTADC,使得RTADC 和RADC 的并联阻抗介于200 Ω和400 Ω之间。

根据经验和/或ADC数据手册建议选择RKB ,通常在5 Ω与36 Ω之间。

通过下式计算滤波器负载阻抗:

ZAAFL = RTADC || (RADC + 2RKB)

选择放大器外部串联电阻RA。如果放大器差分输出阻抗在100 Ω至200 Ω之间,则RA。应小于10 Ω。如果放大器输出阻抗为12 Ω或更小,则RA。应介于5 Ω和36 Ω之间。

选择RTAMP ,使得放大器的总负载ZAL对于所选的特定差分放大器是最佳的,计算公式如下:

ZAL = 2RA + (ZAAFL || 2RTAMP)

计算滤波器源阻抗:

ZAAFS = 2RTAMP || (ZO + 2RA)

利用滤波器设计程序或表格,以及源阻抗ZAAFS 、负载阻抗ZAAFL、滤波器类型、带宽、阶数等,设计滤波器。带宽应比采样速率的一半高大约40%,以确保DC至fs/2频率范围内的平坦度足够好。

程序产生的最终并联电容值应减去ADC内部电容CADC。程序会给出差分并联电容的值CSHUNT2 ,最终共模并联电容为CAAF2 = 2(CSHUNT2 – CADC)。

完成上述初步计算后,应快速检查一下电路的下列项目。

CAAF2的值应比 CADC大好几倍,至少应为10 pF。这是为了最大程度地降低滤波器对 CADC变化的敏感度。

ZAAFL 与 ZAAFS 的比值应等于或小于7左右,使得该滤波器在大多数滤波器表格和设计程序的限制以内。

CAAF1的值至少应为5 pF,以便最大程度地降低滤波器对寄生电容和组件变化的敏感度。

电感 LAAF的值应合理,至少应有数nH。

某些情况下,滤波器设计程序提供的解决方案可能不止一个,特别是对于高阶滤波器。此时应选择组件值组合最为合理的一种解决方案。此外,所选的配置应结束于并联电容,以便能与ADC输入电容结合。

电路优化技术和权衡

该接口电路的参数相互影响,因此,几乎无法优化电路的所有关键特性(带宽、带宽平坦度、SNR、SFDR、增益等)。然而,通过改变 RA 和 RKB,可以最大程度地降低通常出现在带宽响应中的峰化。

请注意图6中通带峰化如何随着输出串联电阻RA的值提高而降低。但是,此电阻的值越高,信号衰减就越大,放大器必须驱动更大的信号以填充ADC的满量程输入范围。

RA 的值也会影响SNR性能。较大的值一方面会降低带宽峰化,但另一方面,往往也会略微提高SNR,因为驱动ADC满量程所需的信号电平更高。

ADC输入端串联电阻RKB的选择应能最大程度地降低ADC内部采样电容的任何残余电荷注入引起的失真。提高此电阻往往也会降低带宽峰化。

但是,提高 RKB 会使信号衰减增大,放大器必须驱动更大的信号以填充ADC的输入范围。优化通带平坦度的另一个办法是少许改变滤波器并联电容CAAF2。

ADC输入端接电阻RTADC的选择一般应使ADC净输入阻抗介于200 Ω和400 Ω之间。降低其值会降低ADC输入电容的影响,并且可能使滤波器设计更加稳定,但不利的一面是会增大电路的插入损耗。提高其值也会降低峰化。

图6. 通带平坦度性能与放大器输出串联电阻RA的关系

要在这些因素之间取得平衡可能比较困难。本设计对每个参数一视同仁,因此,所选的值代表了所有设计特点的接口性能。某些设计中,根据系统要求,可能会选择不同的值,以便优化SFDR、SNR或输入驱动电平。

本设计的SFDR性能取决于两个因素:图1所示的放大器和ADC接口组件值,以及AD9467通过内部寄存器的内部前端缓冲偏置电流设置。表1和图4所示的最终SFDR性能数值是在按照AD9467数据手册所述优化SFDR之后获得的。

该特定设计中可以权衡的另一个因素是ADC满量程设置。对于利用此设计(优化SFDR)获得的数据,ADC满量程差分输入电压设置为2 V p-p。满量程输入范围变为2.5 V p-p可以使SNR性能提高大约1.5 dB,但会略微降低SFDR性能。输入范围由载入AD9467内部寄存器的值设置,详情参见数据手册。

注意,本设计中的信号通过0.1 μF电容交流耦合,以便抑制放大器、其端接电阻与ADC输入端之间的共模电压。有关共模电压的更多信息,请参阅AD9467数据手册。

无源组件和PCB寄生效应考虑

该电路或任何高速电路的性能都高度依赖于适当的PCB布局,包括但不限于电源旁路、受控阻抗线路(如需要)、组件布局、信号布线以及电源层和接地层。有关高速ADC和放大器的PCB布局布线详细信息,请参阅教程MT-031 和 MT-101。

滤波器中的无源组件应使用低寄生效应的表贴电容、电感和电阻。所选的电感为Coilcraft 0603CS系列。滤波器使用的表贴电容为5%、C0G、0402型,以确保稳定性和精度。

常见变化

针对要求较窄带宽、较低功耗的应用,可以使用差分放大器 ADL5561 。ADL5561的带宽为2.9 GHz,功耗仅40 mA。如果要求更低的功耗和带宽,也可以使用ADA4950-1 ,其带宽为1 GHz,功耗仅10 mA。如需更高的带宽,可以使用6 GHz差分放大器ADL5565,它与上述器件引脚兼容。

电路评估与测试

本电路使用修改的AD9467-250EBZ 电路板和基于 HSC-ADC-EVALCZ FPGA的数据采集板。这两片板具有对接高速连接器,可以快速完成设置并评估电路性能。修改的AD9467-250EBZ板包括本笔记所述的评估电路,HSC-ADC-EVALCZ数据采集板与Visual Analog评估软件一起使用,此外还使用SPI控制软件器来适当控制ADC并采集数据。

本文导航

- 第 1 页:ADI实验室电路:带抗混叠滤波器的宽带接收机

- 第 2 页:滤波器和接口设计程序

上周热点文章排行榜

上周资料下载排行榜

创新实用技术专题

疯PK:2015,大陆IC设计赶超台湾?

热评

- LM3S9B96开发板手册及原理图

- NI推出Single-Board RIO嵌入式介面

- LED手电筒电路图

- 3.15投诉:揭开天翼3G手机的“欺骗”

- STM32F103ZET6红牛电路图

- 高通发布全新设计DragonBoard板

- 3gqq.com 网页登录

- 新款 Apple TV 将在3月8日出货

- 小米手机2工程机月底将上市

- protel99se正式汉化版免费下载

博文

- 一个女生对电子信息工程专业的感悟

- 请问KEIL软件使用及流水灯设计,要掌握到什么程度和深度才是过关呢?请大侠们给以指点迷经

- 《论模电与爱情》

- 电子工程师爆料——撕掉电子业现状强大的遮羞布

- 我是小小技术员(一)

- 拯救大学生

- 《昨夜无眠,为了一个学生》

- 5V-USB充电器电路图,有详细制作步骤

- 大三了

- 华为思考人生

用户评论

查看全部 条评论

查看全部 条评论>>