麦瑞半导体公司(Micrel Inc.)发佈了新型可高度配置的双锁相环(PLL)时脉产发生器系列产品,优化了超低抖动、超强串扰隔离和增强型电源杂讯抑制。

2012-10-31 10:24:48 1258

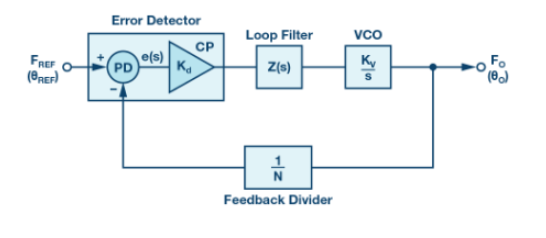

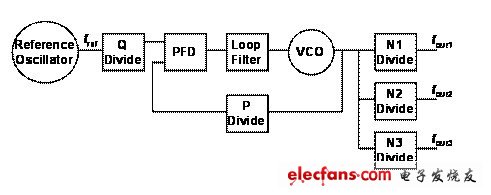

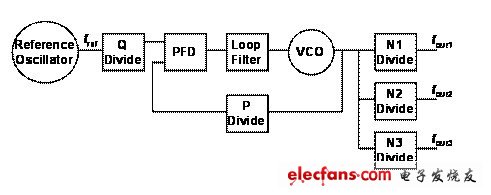

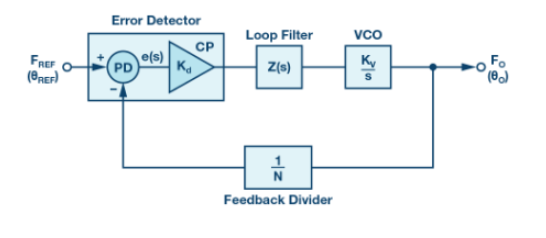

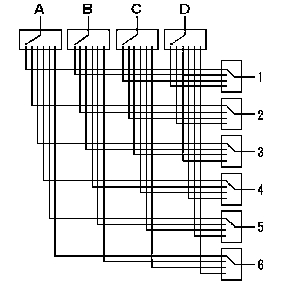

1258 基本配置:时钟净化电路 锁相环的最基本配置是将参考信号(FREF)的相位与可调反馈信号(RFIN)F0的相位进行比较,如图1所示。 图1. PLL基本配置 图2中有一个在频域中工作的负反馈控制环路

2021-03-02 16:34:02 3806

3806

。输入 PLL1 参考时钟设置为 100MHz。 问题是由于更改DLYDIV_SEL 是重新配置PLL,是否必须遵循19.6.4.3 中定义的PLL 复位和重新配置流程?在更改 PLL

2023-04-18 08:25:33

如何用PLL对时钟进行配置呢?PLL配置时钟唤醒后还需要重新配置RCC吗?

2021-11-22 06:30:33

预安装分为哪几种呢?可卸载预安装功能的配置步骤有哪些呢?

2022-03-03 06:26:21

我们正在研究 iMXRT1170 微控制器,并希望在 ENET_1G 接口上实现最佳数据速率。你能帮我们找到为此目的的最佳内存配置吗?更具体地说,我们应该为以下选择哪种存储器(例如,闪存、OCRAM

2023-03-22 06:39:39

配置系统时钟实验1 使用 HSE一般情况下,我们都是使用 HSE,然后 HSE 经过 PLL 倍频之后作为系统时钟。通常的配置是: HSE=8M, PLL 的倍频因子为: 9,系统时钟就设置成

2021-08-12 07:51:30

您好:

我正在使用AD9122芯片。在官方提供Datasheet上最后提供了一配置DA的寄存器的例程,我按照配置方法进行配置。结果出现PLL无法锁定。

配置列表如下

0x00

2023-12-22 08:13:42

最近在使用AD9510这款芯片配置时钟,目前程序已经能够将输入频率直接分频输出,但是PLL锁相环这部分始终没能够配置成功。请问想要PLL锁相环控制VCO输入一个固定的频率到AD9510里面,寄存器该怎么配置?或者配置顺序是怎样的?电路如下:

2019-03-23 15:04:29

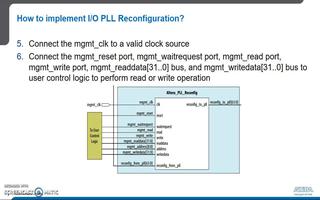

Altera可重配置PLL使用手册在实际应用中,FPGA的工作时钟频率可能在几个时间段内变动,对于与之相关的锁相环(PLL),若PLL的输入时钟在初始设定的时钟频率的基础上变化不太大时,PLL一般

2009-12-22 11:27:13

HSI为24M,用HSI配置PLL 48M时钟作为HCLK时,无法用SW口进行仿真,只要HCLK不使用PLL,就可以正常进行仿真,请教一下PLL的参数该如何配置啊?多谢!!!!!!

现PLL配置参数

2024-03-13 09:50:57

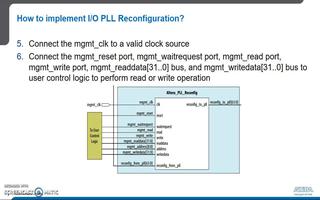

和 ALTPLL_RECONFIG 控制器实例来对物理介质附加子层(PMA) 控制、物理代码子层 (PCS)、 多用锁相环 (PLL) 以及通用锁相环 (PLL) 进行重配置。

2017-11-14 10:53:11

在配置PLL过程中,打开了megawizard plug-in manager后,下拉菜单中没有IO这个选项,更别说选ATLPLL了,求问这是什么情况!PLL配置教程原帖http

2017-03-22 09:58:41

IO口既要当输入又要当输出口时,是不是可以不用在代码生成器里配置,只要在用到的时候再配置输入输出就好了??

2018-07-23 02:37:09

专家你好:

OMAP_l138开发中遇到如下问题,请指教

DSP核链接后可以配置到300M,且程序下载等都正常,ARM核链接后PLL0只能配置到150M,测试环境是winXP CCS3.3 .

2018-06-21 20:18:44

版本3.45.1i尝试配置上述设备上的内部振荡器为64 MHz(16MHz的4xPLL)。我选择了内部RC振荡器、FOSC和16MHZ_HF。如果选择启用PLL,则CONFIG1H的PLCFG得到

2020-04-02 10:44:26

PLL_P是16、17位,为什么配置时的代码是这样:RCC->PLLCFGR = PLL_M | (PLL_N > 1) -1)1) -1)

2017-01-31 23:50:16

有没有人用STM32F103系列做过PMBus的主机呀?和I2C再配置上有什么区别吗?

2024-03-13 07:41:56

STM32为什么必须先配置时钟再配置GPIO?

2018-10-03 08:44:53

STM32时钟配置(超频配置),时钟三种不同的时钟源可被用来驱动系统时钟(SYSCLK):● HSI振荡器时钟● HSE振荡器时钟● PLL时钟具体的系统时钟配置方法及步骤:1.使用HSE配置系统

2021-08-10 06:00:33

进了STOP模式后,PLL停掉了,所以,如果开始的时钟配置,用的是PLL,那么唤醒后,需要重新配置RCC。如果使用的是PLL,及时是用MSI作为时钟源,放大出来的,比如4M的MSI,PLL放大到

2021-08-18 08:17:53

DDR3 PLL配置。1.DDR3PLLCTL1寄存器的ENSAT位(6位)写1(使得PLL得倒最佳操作)2.DDR3PLLCTL0寄存器的BYUPASS写1(设置PLL旁路模式)3.将PLLM

2018-01-24 21:27:10

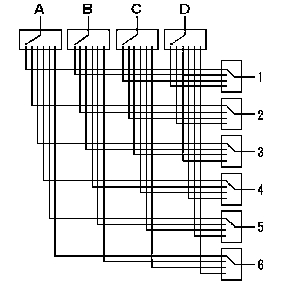

动态配置是用户可以在 PLL 工作过程中通过专门的输入输出接口直接控制锁相环的配置参数,包括: 参考时钟分频系数(M); 反馈时钟分频系数(N); 输出时钟分频系数(C0-4); 输出相位

2022-10-27 08:14:31

Xilinx FPGA入门连载24:PLL实例之基本配置 1 工程移植可以复制上一个实例sp6ex7的整个工程文件夹,更名为sp6ex8。然后在ISE中打开这个新的工程。 2 新建IP核文件

2019-01-21 21:33:40

`Xilinx FPGA入门连载24:PLL实例之基本配置特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm 1 工程移植可以复制上一个实例

2015-11-16 12:09:56

本帖最后由 一只耳朵怪 于 2018-6-21 09:34 编辑

am57xx上有两个网卡,我们想通过一个更新板卡系统数据,一个更新采集数据,但不知道为什么先配置eth0的ip再配置eth1

2018-06-21 06:25:42

在对tms320C6747 PLL配置时,PLLDIV2默认值为1,若修改为其他值,就会报错,而且仿真器也连不上,请问问题出在哪?

2020-05-26 07:56:32

任何频率合成器的目标是根据给定的输入参考频率产生期望的输出频率,然而,可用的输入频率与所需的输出频率之间的关系并不总是明显的。问题总是隐约可见:是否存在另一个更好的配置?对于我的PLL,将提供更好

2019-01-29 10:35:26

,输出PLLP值超过规定范围:有这个提示信息,再也不怕配置出错了。PLL的倍频和分频值有人觉得前面倍频N值很大(如下图),这样会不会出问题?答案肯定是不会。但不建议将参数N设置为最大值。特定时钟频率有些

2020-05-18 07:00:00

和关闭,使用我认为是20MS的γ-DelaysMs(20)。当我增加XTalthFRQ 8000000, 12000000时,延迟变慢。我错过了配置中的一些东西。我需要配置PLL吗?

2020-03-30 08:25:35

我尝试使用内部时钟通过PLL 配置系统时钟为80M 但是用SysCtlClockGet 得到的数值是66M, SysCtlClockSet(SYSCTL_SYSDIV_2_5 | SYSCTL_MAIN_OSC_DIS | SYSCTL_OSC_INT |SYSCTL_USE_PLL);

2018-08-16 06:20:20

`例说FPGA连载30:PLL例化配置与LED之功能概述特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1c0nf6Qc 本实例使用Quartus II

2016-09-09 18:29:24

`例说FPGA连载31:PLL例化配置与LED之PLL的IP核配置特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1c0nf6Qc 本实例使用了一个

2016-09-12 17:31:43

`我想用50M的外部时钟通过pll配置出来一个clk3=4.8Mhz的时钟,但是配置出来的时钟上升沿和主时钟对不齐。还有红线后面那个是怎么回事呀,谢谢大家啦`

2017-12-16 15:12:44

参考了官网和各路大神写的一些关于PLL动态重配置的资料,虽然有收获但是还是感觉大神们写的太高端,不够详细,对于我这种学渣看起来还是迷迷糊糊。所以整理了一下自己的经验,把整个过程记录了下来。没有很多语言全部是截图大家凑合看吧。附有源代码和Word文档。

2017-10-12 12:32:44

您好,我有几个问题想咨询:

1 锁相环路滤波器中开环带宽和相位裕度怎么设置?

2 在通过spi配置寄存器时,寄存器配置是否有顺序要求,还有在配置drg模式参数前是否需要等到pll lock后再配置

2023-12-07 08:04:12

`勇敢的芯伴你玩转Altera FPGA连载63:PLL IP核创建于配置特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1i5LMUUD 可以复制上一个

2018-04-20 21:45:06

在源文件中配置好了PLL,PSC,DDR2等一些参数,为什么在AISgen工具中还要配置,

2020-08-04 10:24:37

嗨,我想用用户可配置的占空比生成时钟。这意味着用户将实时更改占空比。即没有新的比特流文件。所以我从寄存器定义开始,并配置微控制器。我已经开始为Spartan-6使用PLL_BASE时钟管理组件。我只

2019-06-20 15:02:21

STM32CubeMX配置LED(一)本作者是一个刚刚使用32cubemx的小白,采用版本是32cubemx_v5.4.0,再配置过程中我将会初学的经验和大家交流。

2022-01-05 06:22:19

嗨,我想生成一个具有指定频率的时钟,我需要做的所有配置都是使用PLL实现的。请引导我阅读相关文档和示例。非常感谢快速反应。谢谢,kamlendra

2020-05-20 10:57:14

基于特定的开发板上的时钟策略:倍频/分频系数需要在使能 PLL 之前进行配置,所以需要在 Open PLL 之前将所有系统的时钟分频器系数以及PLL的倍频系数配置好。整个时钟的配置流程如下所示:(1

2021-08-23 09:12:44

FUT/FREF看起来是一个有理数,PLL配置为整数-N模式以获得最佳抖动性能(FS0)。有人知道是否有一种方法来禁用这个默认函数&仍然在分数模式,而不是整数模式的程序部分? 以上

2018-10-01 15:22:06

是否可以动态配置逻辑而不是像pll或gtx这样的源。在另一个世界中,动态重新配置的限制是什么以上来自于谷歌翻译以下为原文Is it possible to dynamicly reconfigure

2019-03-14 18:14:19

的,后来并没有改变,找了一圈,说要关闭pll后再配置,结果还是无效。解决办法:先使用内部时钟HIS,不开启pll,最开始的时钟仅仅保证eeprom可以读取参数或者其他方式确定后续需要设置的时钟,然后读取e...

2021-08-12 06:24:57

C6747芯片在仿真器在线下载调试的模式下,若不使用GEL文件,自己写的芯片初始化程序经常跑飞或者运行速度很忙,咨询以下问题:1 PSC,PLL,CACHE,SYSCFG四个模块寄存器配置流程细节

2020-07-30 11:35:28

求大神分享一种高档FPGA可重构配置方法

2021-04-29 06:16:54

`玩转Zynq连载22——[ex03] 基于Zynq PL的PLL配置实例更多资料共享腾讯微云链接:https://share.weiyun.com/5s6bA0s百度网盘链接:https

2019-09-06 08:13:18

在配置主频时主要有四个变量影响;input clock, PLLM, PLLD, OUTPUT_DIVIDE,有几个问题没想明白:

1.如果有Inputclock,没有配置PLLM,PLLD,有

2018-06-19 04:35:00

请问哪位大神配置过AD9510,我现在想通过配置PLL输出一个1.6M的时钟,配了好几次都不成功,希望大家给指导一下,谢谢了!还有就是那个PLL参考输入REFIN是多少了?

2018-09-17 15:45:06

6455的PLL1可以按照技术手册配置,但是PLL2只有一个DIV。这个PLL2是怎么配置?直接写PLLDIV1(0x029C0118)这个寄存器就当配置了?手册那个配置步骤只适合配置PLL1啊!!!

2018-08-02 09:17:37

PLL配置段代码。但是发现该段代码如下

2018-08-06 07:33:54

了两件事:使用带 HSI 的 PLL 来实现 8MHz 时钟,其中不需要 PLL 并且可以完全跳过(将 HSI 除以 2,然后再乘以 2)使用等待状态,而对于 8MHz 则不需要即使使用此配置,核心

2022-12-30 07:20:03

土壤检测实验室仪器设备配置方案配置明细【山东云唐·YT-GT】可应用于大种植户、种植基地、农资商、农技服务公司等

序号

名称

2021-03-25 10:11:39

大型肥料厂配置实验室检测仪器的方案-检测方案配置【山东云唐·YTTRX05】使用绿色植物培肥使用绿色植物培肥主要是通过在田间种植绿肥作物,并将其翻入土中来培肥土壤。栽培绿肥主要以豆科作物为主,如

2021-03-30 14:05:56

用可再配置FPGA实现DSP功能

2010-07-16 17:56:43 10

10 本文档主要是以Altera公司的Stratix II系列的FPGA器件为例,介绍了其内嵌的增强型可重配置PLL在不同的输入时钟频率之间的动态适应,其目的是通过提供PLL的重配置功能,使得不需要对

2010-11-02 15:17:24 27

27 配置一个最佳的RF/微波开关系统

随着通信业的高速增长,组成这些不同通信系统的各种元器件的测试量也随之有了巨大增长。这些产品的测试要求和步骤均有较大的不同,

2009-02-08 23:13:59 531

531

FPGA Cyclone器件中PLL的配置方法

2016-02-23 11:04:13 5

5 配置三层交换机-接口配置

2016-12-24 23:29:53 0

0 新版LAMP源码的安装和配置最佳手册

2017-09-09 09:04:15 0

0 DSP在线升级与资源优化再配置

2017-10-20 09:53:27 5

5 下面我们来看本实例如何配置一个PLL硬核IP,并将其集成到工程中。如图8.18所示,在新建的工程中,点击菜单“ToolsàMegaWizard Plug-In Manager”。

2018-04-24 11:30:02 6654

6654

如何在 Arria 10 中实现 I/O 锁相环 (PLL) 重配置

2018-06-20 00:57:00 3438

3438

不仅仅从频率和相位上比较稳定,而且其时钟网络延时也相比内部逻辑产生的分频时钟要小得多。下面就如何配置一一个PLL做一些说明。

2019-03-06 11:14:26 2

2 得到的时钟不仅仅从频率和相位上比较稳定,而且其时钟网络延时也相比内部逻辑产生的分频时钟要小得多。”下面就如何配置一一个PLL做一些说明。

2019-03-07 16:23:37 2600

2600 先用FPGA的外部输入时钟clk将FPGA的输入复位信号rst_n做异步复位、同步释放处理,然后这个复位信号输入PLL,同时将clk也输入PLL。设计的初衷是在PLL输出有效时钟之前,系统的其他部分都保持复位状态。

2020-03-29 17:19:00 2456

2456

本文档的主要内容详细介绍的是在FPGA上编写通过SPI总线配置外部PLL芯片AD9518和ADC9268的程序免费下载。

2021-03-10 15:50:00 50

50 在FPGA中配置PLL的步骤及使用方法

2021-05-28 10:01:17 20

20 不需要对标准 BGP 行为或配置进行修改就可以完成工作。这样就不必考虑为交换机分配 ASN 编号的事情,有助于在数据中心建立最佳 ASN 配置,并避免在分配错误的脊网络 ASN 时进行的次优路由

2021-07-28 18:10:00 1951

1951 广义的来说,FPGA的配置包括直接使用下载电缆对FPGA器件进行编程、对外部EEPROM和FLASH进行编程、使用MPU对FPGA器件进行编程、外部EEPROM和FLASH对器件进行编程

2021-09-06 09:41:56 6052

6052 在FPGA上编写的通过SPI总线配置外部PLL芯片AD9518和ADC9268的程序(开关电源技术与设计潘永雄.pdf)-在FPGA上编写的通过SPI总线配置外部PLL芯片AD9518和ADC9268的程序,适合感兴趣的人学习参考

2021-09-16 11:37:05 61

61 灯)原理同样先上一张图:这次我们配置sysclk使用的是内部高速时钟 HSI。从上图时钟树可看出HSI可以直接作为SYSCLK的时钟,但是HSI最高只有8M,比较慢,我们采用的是先HSI的2分频 经过 PLL 倍频之后作为系统时钟。通常的配置是:HSI/2=4M,PLL 的倍频因子为:16,系统时钟就

2021-11-26 18:51:10 64

64 STM32F4外部晶振配置system_stm32f4xx.c这个文件里面有晶振使用的配置,一般情况下,跑一个单片机需要做系统晶振初始化,以STM32为例,主循环需要先配置SystemInit

2021-12-24 19:21:12 50

50 文章目录使用cubemx配置stm32(二)__核心配置cubemx工程搭建实现单片机点灯程序CubeMX新建工程CubeMX图形配置调试时钟信号来源**CubeMX图形配置时钟树**CubeMX

2021-12-27 18:48:21 0

0 电子发烧友网站提供《EF3 PLL动态配置.pdf》资料免费下载

2022-09-27 10:26:04 0

0 电子发烧友网站提供《ELF2 FPGA PLL动态配置.pdf》资料免费下载

2022-09-26 15:13:06 0

0 Lattice和Actel的FPGA使用称为反熔丝的非易失性配置技术,其主要优点是系统设计更加简单、不需要外部存储器和配置控制器、功耗低、成本低和FPGA配置时间更快。最大的缺点在于配置是固定的。

2022-12-01 11:08:45 862

862 现在配置对象已经是单例了,但还有一个问题,它的每个配置项的值都是默认值,我们当然是希望它在创建对象的时候是使用配置文件中的值啦。下面看需求三怎么实现。

2023-05-04 10:00:45 453

453 通常情况下,一个IS-IS进程下配置一个NET即可。当区域需要重新划分时,例如将多个区域合并,或者将一个区域划分为多个区域,这种情况下配置多个NET可以在重新配置时仍然能够保证路由的正确性。由于

2023-05-04 11:31:46 696

696

PLL(Phase Locked Loop):为锁相回路或锁相环,用来统一整合时脉讯号,使内存能正确的存取资料。PLL用于振荡器中的反馈技术。许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步,利用锁相环路就可以实现这个目的。

2023-05-29 09:51:32 443

443

pll锁相环的作用 pll锁相环的三种配置模式 PLL锁相环是现代电子技术中广泛应用的一种电路,它的作用是将一个特定频率的输入信号转换为固定频率的输出信号。PLL锁相环的三种配置模式分别为

2023-10-13 17:39:48 1102

1102 配置BGP的前提是要保证各个自治区域的路由均可达,所以要首先在AS 2 配置OSPF使AS 2 通畅,然后再配置BGP。由于BGP的路由黑洞问题,需要在BGP路由经过的所有路由器上配置BGP。

2024-01-06 10:07:02 123

123

(1)

(1) (2)

(2)

(3)

(3)

电子发烧友App

电子发烧友App

评论