您的位置:电子发烧友网 > 电子技术应用 > 行业新闻 > 国外电子 >

深入赛灵思Kintex-7 FPGA内部 - 深入赛灵思Kintex-7 FPGA内部:透视HKMG技术

2012年04月13日 16:09 来源:电子发烧友网原创 作者:电子大兵 我要评论(0)

深入赛灵思Kintex-7 FPGA内部

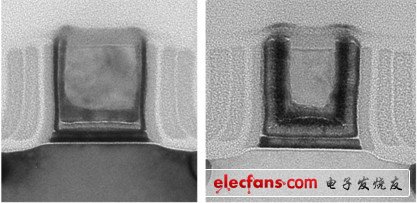

台积电的HPL NMOS 和 PMOS晶体三极管在Kintex-7 FPGA中,如下图所示。两个晶体管被用作后栅极工艺,TiN/HfO2/oxide栅极绝缘层被堆积在第一层。

台积电HPL NMOS (左) PMOS (右)

多晶硅被剥离,不同的金属门被堆积到NMOS和PMOS门区域。

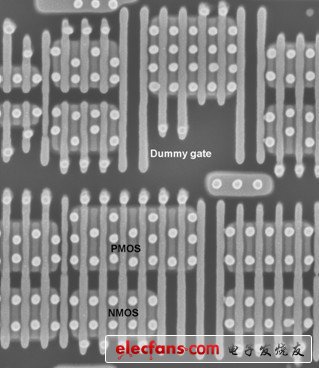

Kintec-7 FPGA门布局设计

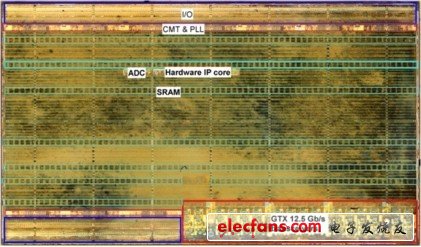

高逻辑密度为Kintex-7 FPGAs设计的一大特色,内部设计为478,000个逻辑单元。其他特色包括:三十二个串行传输速度高达12.5 Gb/s高性能连接收发器,34Mb RAM和1,920 个DSP分割区,DSP性能高达2,845 GMACS以及16通道双通道12位多相串行ADC。

——电子发烧友网版权所有,转载请注明出处!

本文导航

- 第 1 页:深入赛灵思Kintex-7 FPGA内部:透视HKMG技术

- 第 2 页:深入赛灵思Kintex-7 FPGA内部

标签: