电子发烧友网核心提示:本文为玩转赛灵思Zedboard开发板(3):基于Zynq PL的流水灯,内容精彩,敬请对电子发烧友网保持密切关注。基于Zynq PL的流水灯是使用PL做流水灯实验,目的是为

2012-12-05 14:25:41 12770

12770 电子发烧友网核心提示 :本文介绍了最新的Xilinx Zynq-7000 FPGA开发板 Zedboard 。Zedboard是基于Xilinx Zynq-7000扩展式处理平台(EPP)的低成本开发板,也是行业首个面向开源社区的Zynq-7000扩展

2012-11-26 15:09:01 55135

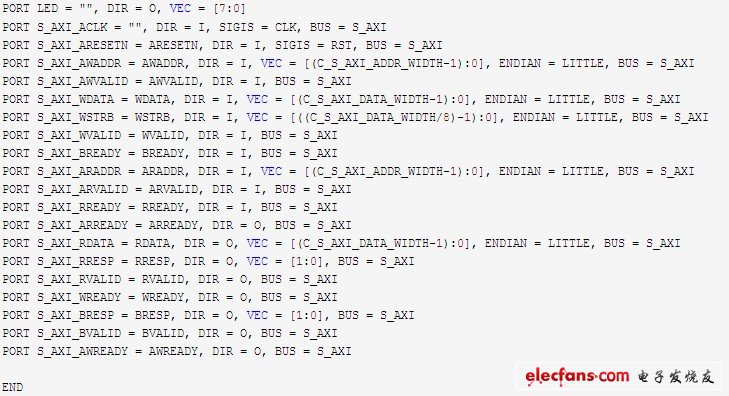

55135 。AXI4-Lite接口的特性如下: 1) 突发长度为1。 2) 所有访问数据的宽度和数据总线宽度相同。 3) 支持数据总线宽度为32位或64位。 4) 所有的访问相当于AWCACHE和ARCACHE

2020-09-27 11:33:02 8051

8051

FPGA+ARM是ZYNQ的特点,那么PL部分怎么和ARM通信呢,依靠的就是AXI总线。这个实验是创建一个基于AXI总线的GPIO IP,利用PL的资源来扩充GPIO资源。通过这个实验迅速入门开发

2020-12-25 14:07:02 2957

2957

电子发烧友网核心提示 : ZedBoard开发板 上的Zynq是一个ARM PS(processing system, 双核A9 + 存储管理 + 外设)+ PL(programable Logic) 结构,如果不使用PL,zynq的开发和普通的ARM 开发一样。不同

2012-11-26 15:49:47 14399

14399 电子发烧友网编辑现为读者整合《玩转赛灵思Zedboard开发板》系列文章, 其中包括在ZedBoard开发板上的一些应用实例。本文主要讲述Zedboard上的嵌入式linux应用,包括使用SDK设计最简单的linux应用程序、linux交叉编译环境搭建、设备驱动编写等内容...

2013-01-24 13:38:18 16892

16892 ( - 用户在此处添加端口 - 用户端口结束 - 请勿修改此行之外的端口 - Axi从设备总线接口S00_AXIS的端口s00_axis_aclk:在std_logic中;s00_axis_aresetn:在

2020-08-20 13:59:52

PL端的编写和使用,接下来是PS端的介绍AXI_Lite总线使用方法(上)pl端读写BRAM一、总览如图,main函数实现的功能主要是初始化中断,中断来自WRRD模块发送数据完毕,中断触发为上升沿。具体功能往下看。我们首先来看#define。不知道还有没有记得..

2022-01-10 08:00:55

电子发烧友网讯:由赛灵思(xilinx)公司和华强PCB网赞助,电子发烧友网主办的玩转FPGA,赛灵思设计大赛已经圆满结束。本活动旨在建立一个FPGA技能展示和技术交流平台,鼓励广大参赛者发挥

2012-09-06 11:52:48

Spartan-6开发板 二等奖奖品: Xilinx Spartan-6开发板 三等奖奖品: 电子发烧友T恤+赛灵思小礼品 大赛获奖名单 一等奖 姚佳毅(yjysdu)——车牌

2012-09-06 11:54:16

与技术学院教授史治国:浙江大学信息与电子工程学系副教授徐文波:毕业于北京邮电大学硕士研究生,FPGA图书作者活动奖品一等奖二等奖三等奖幸运奖1名5名10名若干iPad2+Xilins Spartan-6开发板Xilins Spartan-6开发板电子发烧友T恤赛灵思官方期刊杂志`

2012-04-23 09:31:16

)二等奖:Xilinx Spartan-6开发板(5名)三等奖:电子发烧友T恤(10名)小奖品:赛灵思官方期刊杂志【活动时间及流程】4月23日—7月31日报名阶段:4月23日至7月20日期间,参赛者报名

2012-04-24 14:40:58

经过准备,"玩转FPGA,赛灵思超值开发板等你拿"设计大赛正式上线,现已开始接受报名.报名地址:https://www.elecfans.com/activities/fpga/

2012-04-23 15:31:01

LZAedkCwQtllAEyw提取码:ld9cFPGA软件无线电开发(全阶视频教程+开发板+实例)详情链接:http://url.elecfans.com/u/5e4a12f2ba`

2019-11-12 10:23:42

芯片可以做到了最优状态。因此,对于用Zynq做开发的工程师而言,如何玩转AXI HP总线就成为了必修课。本实例(zstar_ex56)通过一个简单的AXIHP总线主机的读时序和写时序逻辑,来带领读者掌握

2019-11-26 09:47:20

无线电开发(全阶视频教程+开发板+实例)详情链接:http://url.elecfans.com/u/5e4a12f2ba`

2019-11-28 10:11:38

`玩转Zynq连载3——AXI总线协议介绍1 更多资料共享 链接:https://share.weiyun.com/5s6bA0s 1 AXI协议简介AMBA AXI(Advanced

2019-05-06 16:55:32

。ROHM与安富利公司共同开发赛灵思7系列FPGA及Zynq®–7000 All Programmable SoC的评估套件Mini-Module Plus 用的电源模块。安富利公司已经开发出多款赛灵思

2018-12-04 10:02:08

`赛灵思FPGA原理图例子之s3astarter 赛灵思一向是FPGA领域里的领先者,运用FPGA需要深入的理解它的工作原理,小编亲子整理了s3astarter 的经典fpga原理图分享给电子工程师们。赛灵思FPGA原理图例子之s3astarter [hide][/hide]`

2012-03-16 10:41:19

赛灵思公司(Xilinx)日前宣布NEC子公司NEC Display Solutions有限公司的三款DLP数字影院投影仪产品,均采用了赛灵思Virtex®-5 FPGA系列产品。

2019-08-19 07:12:03

赛灵思Spartan开发板使用困境记录原理图和接口主要是对照核心板的原理图,一般的接法就是赛灵思系列的单片机,连接好电源和下载器,记得预先安好驱动,驱动安装成功与否能够在设备管理器处查看。作者困境

2021-07-13 08:42:10

赛灵思Verilog(FPGACPLD)设计小技巧

2012-08-19 22:52:02

尊敬的赛灵思客户朋友们:在此,我谨代表赛灵思公司与您分享一个激动人心的喜讯: 3 月1 日,赛灵思公司宣布全球第一片28nmFPGA 芯片(7K325T) 成功量产了!该里程碑式信息的发布,不仅是赛

2012-03-22 15:17:12

赛灵思有哪几种ISE设计套件配置版本 ?

2021-04-30 06:30:50

最近在用赛灵思的DDR3,用的AXi4接口,我写入的地址是按照突发长度来的,连续给8个读的地址,但是在DDR3端,dq_addr 一直在1418,1000,1010,0003,0002 等几个地址中

2016-06-24 10:38:18

赛灵思的FPGA用什么开发工具编程,有没有大佬分享一下安装包

2018-05-24 17:51:38

赛灵思(XILINX)全新7系列FPGA详述

2012-08-14 12:20:22

FPGA是用altera多还是赛灵思的多呢,我买的开发板是altera的,但是很多人推荐说学习赛灵思的好

2016-01-09 21:27:25

`FPGA设计大赛奖品.苹果iPad2+赛灵思Xilinx Spartan-6开发板 等你拿,FPGA发烧友、工程师们,心动了么,那就赶快猛戳这里报名吧一等奖奖品:iPad2+Xilinx

2012-04-25 09:32:46

N32G430C8L7_STB开发板用于32位MCU N32G430C8L7的开发

2023-03-31 12:05:12

赛灵思 EGO1 口袋实验开发板-全套包括:开发板使用手册、及配置实验共8个,都有原码和公司每个实验指导书的pdf 还包括:EGO1板卡文件、引脚约束文件、及硬件手册。

2018-10-05 22:22:18

` 本帖最后由 MGJOY 于 2017-4-10 15:07 编辑

本周三,4月12日,赛灵思FPGA技术及应用线上公开课。欢迎大家观看、学习交流~分享主题【赛灵思FPGA人工智能领域技术及应用】嵌入式视觉领域技术和解决方案机器学习方面的技术和解决方案ADAS/自动驾驶方面的应用`

2017-04-10 15:06:16

能做赛灵思方案的,请联系

2019-01-21 19:31:40

图如下:需要强调的是,AXI的五个通道,每个通道都有握手机制,接下来我们就来分析一下AXI-Lite的源码来更深入的了解AXI机制。突发式读当地址出现在地址总线后,传输的数据将出现在读数据通道上。设备

2018-01-08 15:44:39

`{:4_122:}{:4_122:}抢楼啦!!“赛灵思”抢楼活动第二轮中奖楼层公布号外号外{:4_104:}:为了答谢各位坛友们的大力支持,我和我的小伙伴们决定在增加5个中奖楼层,让各位中奖的几率

2013-10-11 10:40:34

小弟我是学习FPGA嵌入式的新手,最近在学习使用zedboard开发板,在研究zedboard_CTT_V14.4官方例程的时候,按照附录的程序,一直报错,表示添加的外设DEVICE_ID没有定义

2015-04-22 20:54:49

系列,为用户从端点到边缘再到云端多种不同技术的快速创新提供支持。 Peng的战略包括三大要点: “数据中心加速”提为发展新重点: 赛灵思正在加强与关键数据中心客户、生态系统合作伙伴及软件应用开发

2018-03-23 14:31:40

PYNQ-Z2平台完善该项目的开源设计,并进一步提升性能。项目计划①根据文档,对赛灵思PYNQ-Z2快速入门②通过学习赛灵思PYNQ-Z2的软件和系统,了解实际应用案例,熟悉开发过程③基于赛灵思PYNQ-Z2

2019-01-09 14:49:25

` 非常感谢此次发烧友论坛和芯灵思举办的芯灵思开发板前楼活动,让本人此次有机会体验SINA31s的开发板套件。快递很给力,前天贴出快递单号今天下午就收到了板子。越是迫不及待的打开欣赏了一番,现在

2015-11-06 01:00:03

感谢电子发烧友、感谢芯灵思这次获得了芯灵思八核A83T开发板套件的试用机会,昨天收到货包装非常精致,采用青色硬纸盒包装(包含上下盖),产品包装正面右上角用白色中英文标注了芯灵思的品牌标示,左侧

2017-05-01 14:20:17

折腾此类开发板,比如普中科技51单片机、威锐视Red 5 FPGA开发板等,闲话少说,直奔主题,很高兴和大家分享这一期的芯灵思A83T开发套件试用体验。二、开箱体验昨天中午收到了这款难得芯灵思A83T

2017-04-30 17:46:23

本帖最后由 可乐丸子 于 2017-7-5 21:36 编辑

项目概述:芯灵思A83T开发板可以配合树莓派、网络摄像头、USB摄像头打造家庭网络监控,芯灵思A83T开发板可以作为家庭网络监控

2017-07-01 10:58:03

Altera和赛灵思20年来都在FPGA这个窄众市场激烈的竞争者,然而Peter Larson基于对两个公司现金流折现法的研究表明,赛灵思是目前FPGA市场的绝对领先者。

2019-09-02 06:04:21

今年年初,赛灵思率先在FPGA领域提出目标设计平台概念,旨在通过选用开放的标准、通用的开发流程以及类似的设计环境,减少通用工作对设计人员时间的占用,确保他们能集中精力从事创新性的开发工作。

2019-08-13 07:27:15

赛灵思 MATLAB & Simulink Add-on插件是将 ModelComposer 和 System Generator forDSP完美结合的统一工具。

2021-01-28 06:33:40

大家好,我正在使用vivado 2014.4制作zc702板,我想使用axi lite ipif ip。首先我不能把它称为IP,因为Vivado找不到它,所以我直接使用vhdl文件到我的项目

2020-04-09 12:23:27

[]合成了内存),输出端口合成为ap_fifo,这意味着,由于AXi4Lite不支持fifo结构,因此只能使用AXI4Stream接口/总线从输出端口result []读取数据。我也是这个嵌入式总线和接口

2019-02-28 13:47:30

回收Xilinx带板芯片, 回收工厂赛灵思XILINX系列IC:XC3S1500FGG676EGQ、XC5VLX50-1FFG676、XC5

2021-12-17 10:02:19

国外的融合技术专家展示了一项基于FPGA的数据采集系统,用于合成孔径成像技术。采用了Xilinx ISE设计软件,支持ARM AMBA AXI4接口。文风犀利,观点新颖,FPGA中使用ARM及AMBA总线中不可多得的资料在赛灵思FPGA中使用ARM及AMBA总线[hide][/hide]

2012-03-01 15:48:17

基于赛灵思的FPGA的EtherCAT主站总线控制 ,论坛有做运动控制这方面的技术吗?目前我已实现带32轴同步运行,同步抖动±75ns,控制精度125us。感兴趣的可以一起探讨下

2018-07-23 12:00:39

和功能测试覆盖了完整LTE协议栈及其应用。射频前端采用本地多输入多输出(MIMO)设计,可支持5MHz、10MHz、15MHz和20MHz多种不同带宽。 这个仿真器中心采用三个赛灵思Virtex®-5

2019-06-17 06:36:10

`Zing是一块由北京威视锐公司推出的基于赛灵思可扩展处理平台架构的高性能开发板。它使用了赛灵思最新推出的Zynq-7000系列芯片,它采用 28nm制程工艺,具有高性能、低功耗等特点,其最主要

2020-10-21 14:32:12

FAST包处理器的核心功能是什么如何使用赛灵思FPGA加速包处理?

2021-04-30 06:32:20

全球可编程逻辑解决方案领导厂商赛灵思公司 (Xilinx Inc.) 宣布,为推进可编程势在必行之必然趋势,正对系统工程师在全球发布赛灵思新一代可编程FPGA平台。和前代产品相比,全新的平台功耗降低

2019-08-09 07:27:00

嗨,我开始使用Vivado了。我正在尝试配置从Dram读取数据的自定义IP,处理它们然后将结果发送到Bram控制器。我想过使用AXI主接口制作自定义IP。但是,我不知道将AXI主信号连接到我的自定义逻辑,以便我可以从Dram读取数据并将结果发送到Bram。谢谢。

2020-05-14 06:41:47

怎么利用赛灵思FGPA实现降采样FIR滤波器?这种滤波器在软件无线电与数据采集类应用中都很常见。

2019-08-15 08:21:22

“玩转FPGA:iPad2,赛灵思开发板等你拿”活动持续火爆进行中……………………活动得到了广大电子工程师积极强烈的支持,为了回报电子工程师和网站会员,现在只需提交fpga设计方案,就有机会获得赛灵

2012-07-06 17:24:41

嗨,我将通过测试验证这一点,但我对AXI-Lite外设“寄存器写入”如何出现在AXI-Lite总线上有疑问。AXI标准表明数据和地址可以非常相互独立地出现,从灵活性的角度来看这是很好的,但是

2019-04-12 13:45:01

了空洞位于球的BGA侧,而不是PCB侧。从同一托盘检查其他BGA设备显示焊球有一些斑驳的外观,没有预期的光泽和光滑。有没有类似的经历?结果是你的CM的流程问题了吗?有没有人从赛灵思获得有缺陷的BGA?你们中有多少人做5DX排尿检查?

2020-06-17 13:27:03

刚开始学赛灵思的FPGA,求他的ISE软件下载地址,我在网上没搜到。谢谢了

2012-08-02 09:52:12

请问各位大神,谁有赛灵思XC7V2000T这块FPGA的开发板原理图,求一份,多谢

2015-09-07 17:05:03

,ar)共用一组信号的接口(arw,w,b,r)。关于总线互联的设计凡是设计中用到Axi4总线的设计总离不开总线互联。在Xilinx FPGA使用中,VIvado针对Axi4总线提供了丰富的IP,对于

2022-08-02 14:28:46

` 本帖最后由 HelloWii 于 2015-9-9 11:52 编辑

买了一块芯灵思开发板,这款板子总的来说是相当不错的,性能稳定,资源相当丰富,而且还配有学习视频,这些呢,是我自己通过学习

2015-09-09 11:38:25

芯灵思SinImx6ul开发板支持三种启动方式,分别是SD卡、 NandFLASH 、 USB下图是启动模式选择NXP Imx6ul芯片的特点是接口多,功耗低,A7处理器,全工业级,性价比好。

2018-10-30 09:53:53

芯灵思SinlinxA33开发板 使用MIPI DSI屏幕我这里用的是从芯灵思买的mipi屏幕,其它型号屏幕也可以参考首先准备好相关屏幕驱动mb709_mipi.c将到mb709_mipi.c

2019-01-02 09:49:36

芯灵思的开发板子有用过的朋友吗?这款板子怎么样啊

2015-07-13 10:07:31

详解赛灵思All Programmable Smarter Vision解决方案

2021-06-02 06:56:12

嗨,我在Vivado 2016.3模块设计中集成了PCIe DMA BAR0 AXI Lite接口和AXI IIC IP。在DMA IP端,它显示S_AXI_Lite端口,但在AXI_IIC IP端

2020-05-14 09:09:35

,永久,_0_0_0tri_mode_eth_macIP:Design_Linking常驻2017.04节点锁定C:\赛灵思\ Vivado \ 2017.1 \ DATA \ IP

2020-08-21 11:07:27

丝印查不到系列型号,引脚数量也对不上赛灵思所有型号规格,赛灵思也没有韩国产地

2023-02-24 17:01:32

电子发烧友网讯:赛灵思FPGA 7系列芯片正以燎原之势席卷整个行业。在本文,电子发烧友网小编将带领大家一起走近Xilinx的FPGA 7系列芯片,从全新FPGA 7系列芯片的介绍、芯片优点、芯片

2012-09-06 16:24:35

) 的灵活可编程 VESADisplayPort v.1.1a 解决方案。该 IP 可随时提供给赛灵思的客户,但在用户展开设计之前,建议先了解与该标准的部分关键功能有关的其它背景信息,如olicy Maker

2012-03-01 11:10:18

高价回收赛灵思系列IC长期回收赛灵思系列IC,高价求购赛灵思系列IC。深圳帝欧长期回收ic电子料,帝欧赵生***QQ1816233102/879821252邮箱dealic@163.com。帝欧回收

2021-04-06 18:07:50

Spartan-6开发板 三等奖奖品: 电子发烧友网T恤+赛灵思小礼品 那接下来我们就展示一下奖品阵容吧!先给大家看看我们的iPad 2吧。图 一等奖奖品之iPad 2#p#赛灵思Spartan-6开发板

2012-09-06 14:33:50

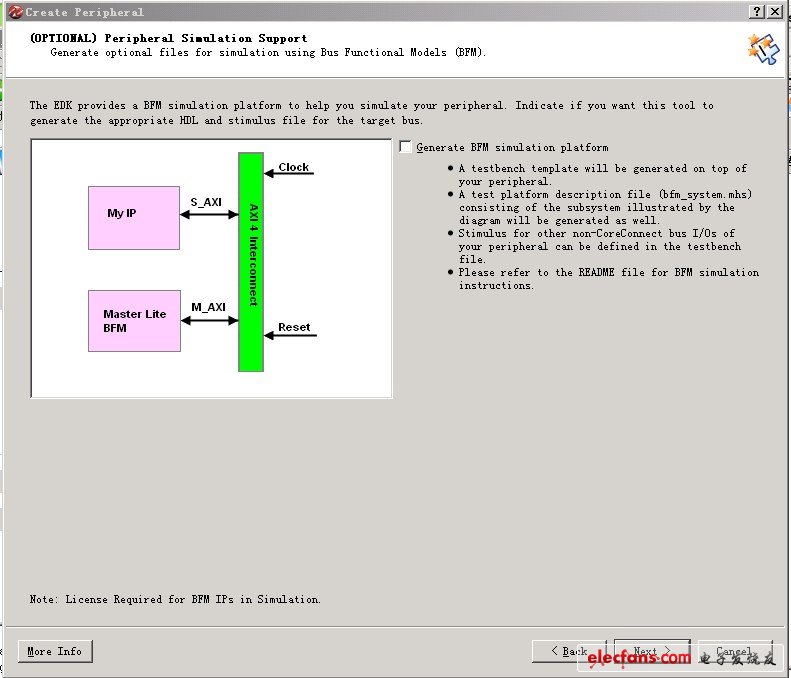

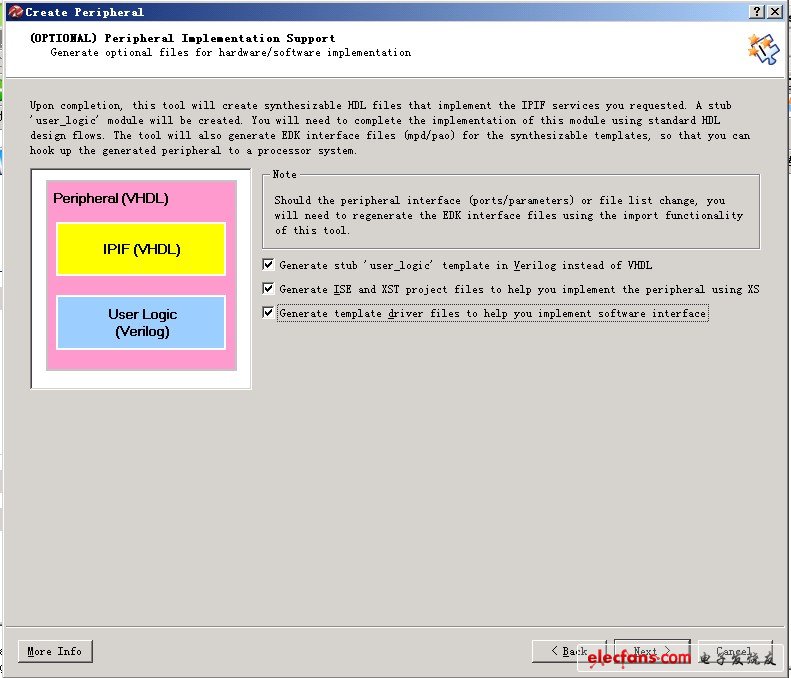

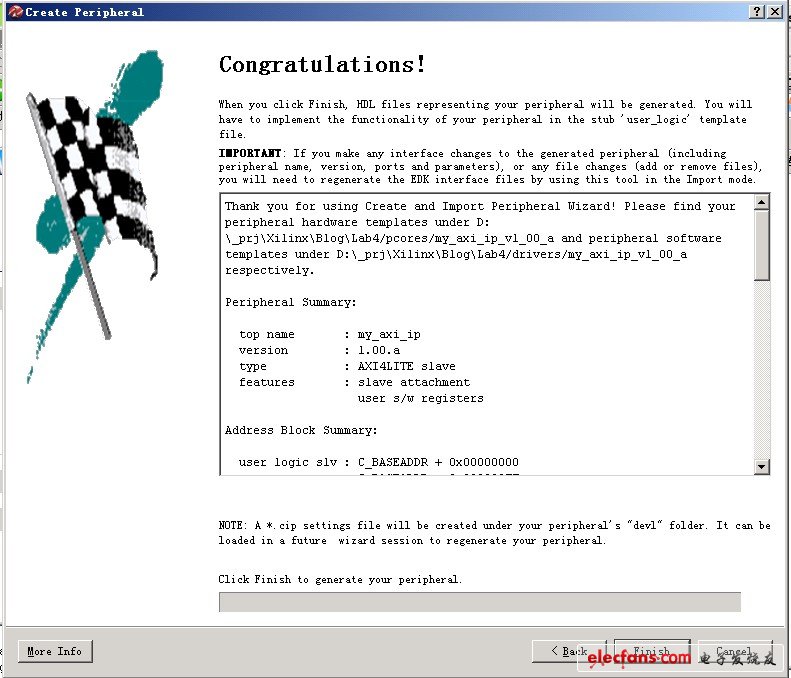

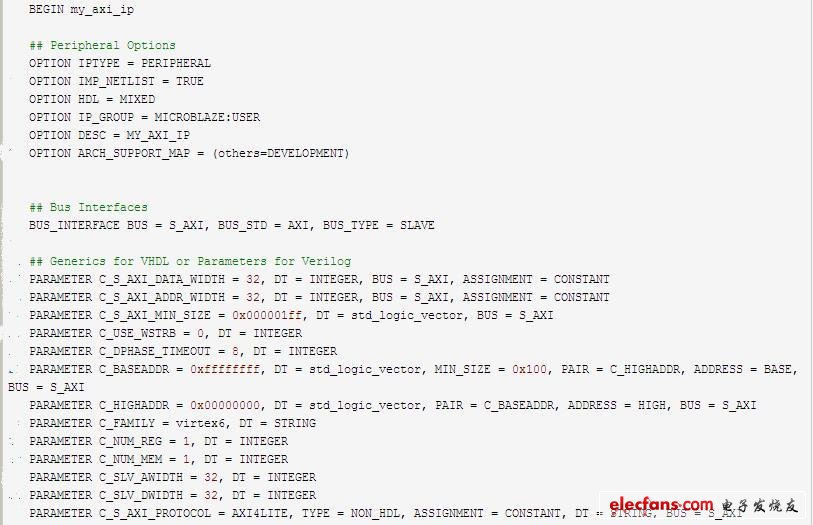

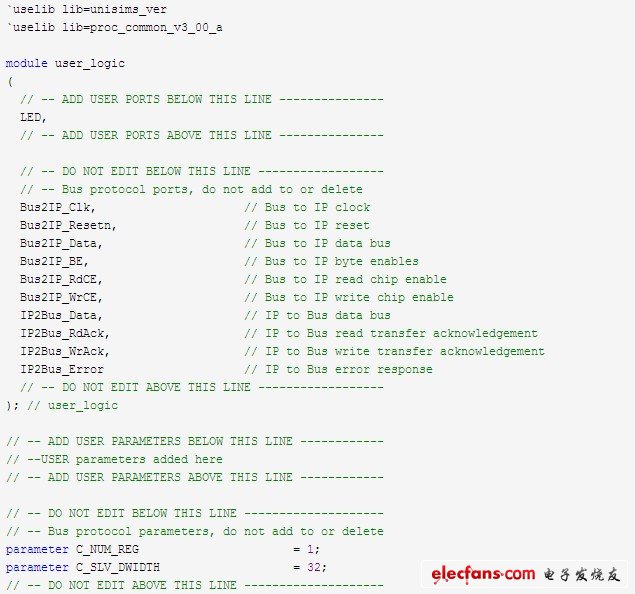

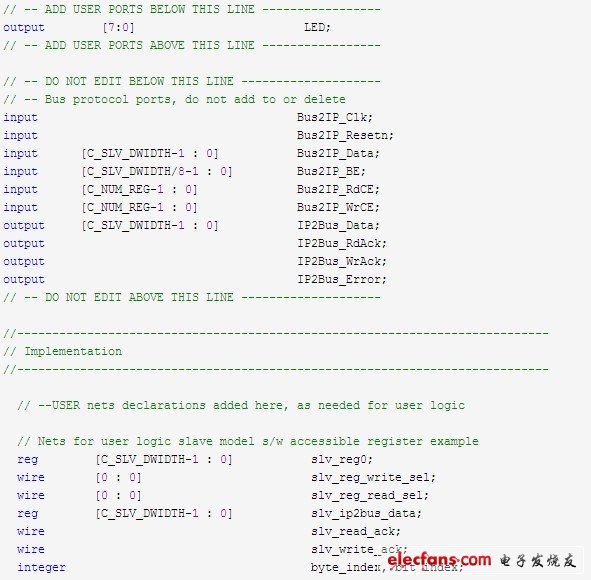

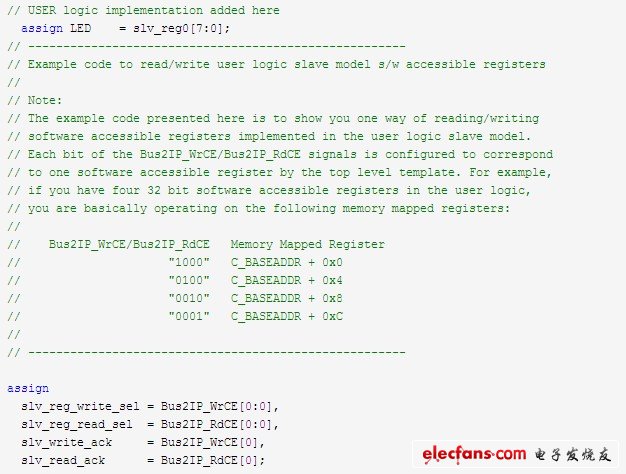

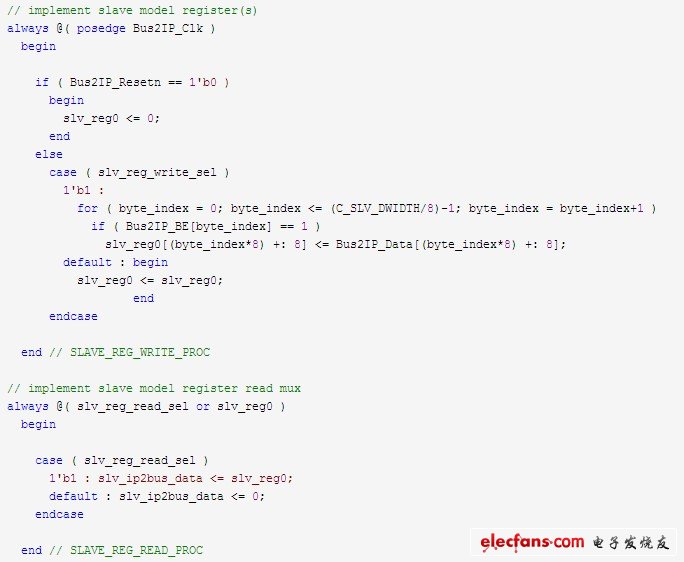

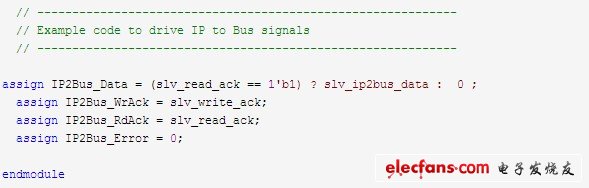

本小节通过使用XPS中的定制IP向导(ipwiz),为已经存在的ARM PS 系统添加用户自定IP(Custom IP ),了解AXI Lite IP基本结构,并掌握AXI Lite IP的定制方法,为后续编写复杂AXI IP打下基础。

2017-02-10 20:37:12 5407

5407 本文先总结不同AXI IP核的实现的方法,性能的对比,性能差异的分析,可能改进的方面。使用的硬件平台是Zedboard。 不同的AXI总线卷积加速模块的概况 这次实现并逐渐优化了三个版本的卷积加速模块,先简要描述各个版本的主要内容。

2018-06-29 14:34:00 7834

7834

这将创建一个附带 BD 的 Vivado 工程,此 BD 包含 AXI VIP (设置为 AXI4-Lite 主接口) 和 AXI GPIO IP。这与我们在 AXI 基础第 3 讲一文 中完成的最终设计十分相似。

2020-04-30 16:24:50 2068

2068

XDMA是Xilinx封装好的PCIE DMA传输IP,可以很方便的把PCIE总线上的数据传输事务映射到AXI总线上面,实现上位机直接对AXI总线进行读写而对PCIE本身TLP的组包和解包无感。

2020-12-28 10:17:23 2692

2692 在《AXI-Lite 自定义IP》章节基础上,添加ilavio等调试ip,完成后的BD如下图: 图4‑53 添加测试信号 加载到SDK,并且在Vivado中连接到开发板。 Trigger Setup

2020-10-30 17:10:22 2041

2041

和接口的构架 在ZYNQ中,支持AXI-Lite,AXI4和AXI-Stream三种总线,但PS与PL之间的接口却只支持前两种,AXI-Stream只能在PL中实现,不能直接和PS相连,必须通过

2020-11-02 11:27:51 3880

3880

AXI4 是一种高性能memory-mapped总线,AXI4-Lite是一只简单的、低通量的memory-mapped 总线,而 AXI4-Stream 可以传输高速数据流。从字面意思去理解

2022-07-04 09:40:14 5818

5818 在 AXI 基础第 6 讲 - Vitis HLS 中的 AXI4-Lite 简介中,使用 C 语言在 HLS 中创建包含 AXI4-Lite 接口的 IP。在本篇博文中,我们将学习如何导出 IP

2022-08-02 09:43:05 579

579

在 Vivado 中自定义 AXI4-Lite 接口的 IP,实现一个简单的 LED 控制功能,并将其挂载到 AXI Interconnect 总线互联结构上,通过 ZYNQ 主机控制,后面对 Xilinx 提供的整个 AXI4-Lite 源码进行分析。

2023-06-25 16:31:25 1914

1914

中的一个参数来选择。 集成设计环境(IDE)。AXI数据总线的宽度可定制。该IP可通过AXI4互连驱动AXI4-Lite或AXI4内存映射从站。运行时间与该内核的交互需要使用Vivado逻辑分析器功能。

2023-10-16 10:12:42 410

410

以AXI4为例,有AXI full/lite/stream之分。 在Xilinx系列FPGA及其有关IP核中,经常见到AXI总线接口,AXI总线又分为三种: •AXI-Lite,AXI-Full以及

2023-10-31 15:37:08 386

386

电子发烧友App

电子发烧友App

评论