232 ------------------------------------------

233 -- Component declaration for verilog user logic

234 ------------------------------------------

235 component user_logic is

236 generic

237 (

238 -- ADD USER GENERICS BELOW THIS LINE ---------------

239 --USER generics added here

240 -- ADD USER GENERICS ABOVE THIS LINE ---------------

241

242 -- DO NOT EDIT BELOW THIS LINE ---------------------

243 -- Bus protocol parameters, do not add to or delete

244 C_NUM_REG : integer := 1;

245 C_SLV_DWIDTH : integer := 32

246 -- DO NOT EDIT ABOVE THIS LINE ---------------------

247 );

248 port

249 (

250 -- ADD USER PORTS BELOW THIS LINE ------------------

251 LED : out std_logic_vector(7 downto 0);

252 -- ADD USER PORTS ABOVE THIS LINE ------------------

253

254 -- DO NOT EDIT BELOW THIS LINE ---------------------

255 -- Bus protocol ports, do not add to or delete

256 Bus2IP_Clk : in std_logic;

257 Bus2IP_Resetn : in std_logic;

258 Bus2IP_Data : in std_logic_vector(C_SLV_DWIDTH-1 downto 0);

259 Bus2IP_BE : in std_logic_vector(C_SLV_DWIDTH/8-1 downto 0);

260 Bus2IP_RdCE : in std_logic_vector(C_NUM_REG-1 downto 0);

261 Bus2IP_WrCE : in std_logic_vector(C_NUM_REG-1 downto 0);

262 IP2Bus_Data : out std_logic_vector(C_SLV_DWIDTH-1 downto 0);

263 IP2Bus_RdAck : out std_logic;

264 IP2Bus_WrAck : out std_logic;

265 IP2Bus_Error : out std_logic

266 -- DO NOT EDIT ABOVE THIS LINE ---------------------

267 );

268 end component user_logic;

269

270 begin

271

272 ------------------------------------------

273 -- instantiate axi_lite_ipif

274 ------------------------------------------

275 AXI_LITE_IPIF_I : entity axi_lite_ipif_v1_01_a.axi_lite_ipif

276 generic map

277 (

278 C_S_AXI_DATA_WIDTH => IPIF_SLV_DWIDTH,

279 C_S_AXI_ADDR_WIDTH => C_S_AXI_ADDR_WIDTH,

280 C_S_AXI_MIN_SIZE => C_S_AXI_MIN_SIZE,

281 C_USE_WSTRB => C_USE_WSTRB,

282 C_DPHASE_TIMEOUT => C_DPHASE_TIMEOUT,

283 C_ARD_ADDR_RANGE_ARRAY => IPIF_ARD_ADDR_RANGE_ARRAY,

284 C_ARD_NUM_CE_ARRAY => IPIF_ARD_NUM_CE_ARRAY,

285 C_FAMILY => C_FAMILY

286 )

287 port map

288 (

289 S_AXI_ACLK => S_AXI_ACLK,

290 S_AXI_ARESETN => S_AXI_ARESETN,

291 S_AXI_AWADDR => S_AXI_AWADDR,

292 S_AXI_AWVALID => S_AXI_AWVALID,

293 S_AXI_WDATA => S_AXI_WDATA,

294 S_AXI_WSTRB => S_AXI_WSTRB,

295 S_AXI_WVALID => S_AXI_WVALID,

296 S_AXI_BREADY => S_AXI_BREADY,

297 S_AXI_ARADDR => S_AXI_ARADDR,

298 S_AXI_ARVALID => S_AXI_ARVALID,

299 S_AXI_RREADY => S_AXI_RREADY,

300 S_AXI_ARREADY => S_AXI_ARREADY,

301 S_AXI_RDATA => S_AXI_RDATA,

302 S_AXI_RRESP => S_AXI_RRESP,

303 S_AXI_RVALID => S_AXI_RVALID,

304 S_AXI_WREADY => S_AXI_WREADY,

305 S_AXI_BRESP => S_AXI_BRESP,

306 S_AXI_BVALID => S_AXI_BVALID,

307 S_AXI_AWREADY => S_AXI_AWREADY,

308 Bus2IP_Clk => ipif_Bus2IP_Clk,

309 Bus2IP_Resetn => ipif_Bus2IP_Resetn,

310 Bus2IP_Addr => ipif_Bus2IP_Addr,

311 Bus2IP_RNW => ipif_Bus2IP_RNW,

312 Bus2IP_BE => ipif_Bus2IP_BE,

313 Bus2IP_CS => ipif_Bus2IP_CS,

314 Bus2IP_RdCE => ipif_Bus2IP_RdCE,

315 Bus2IP_WrCE => ipif_Bus2IP_WrCE,

316 Bus2IP_Data => ipif_Bus2IP_Data,

317 IP2Bus_WrAck => ipif_IP2Bus_WrAck,

318 IP2Bus_RdAck => ipif_IP2Bus_RdAck,

319 IP2Bus_Error => ipif_IP2Bus_Error,

320 IP2Bus_Data => ipif_IP2Bus_Data

321 );

322

323 ------------------------------------------

324 -- instantiate User Logic

325 ------------------------------------------

326 USER_LOGIC_I : component user_logic

327 generic map

328 (

329 -- MAP USER GENERICS BELOW THIS LINE ---------------

330 --USER generics mapped here

331 -- MAP USER GENERICS ABOVE THIS LINE ---------------

332

333 C_NUM_REG => USER_NUM_REG,

334 C_SLV_DWIDTH => USER_SLV_DWIDTH

335 )

336 port map

337 (

338 -- MAP USER PORTS BELOW THIS LINE ------------------

339 LED => LED,

340 -- MAP USER PORTS ABOVE THIS LINE ------------------

341

342 Bus2IP_Clk => ipif_Bus2IP_Clk,

343 Bus2IP_Resetn => ipif_Bus2IP_Resetn,

344 Bus2IP_Data => ipif_Bus2IP_Data,

345 Bus2IP_BE => ipif_Bus2IP_BE,

346 Bus2IP_RdCE => user_Bus2IP_RdCE,

347 Bus2IP_WrCE => user_Bus2IP_WrCE,

348 IP2Bus_Data => user_IP2Bus_Data,

349 IP2Bus_RdAck => user_IP2Bus_RdAck,

350 IP2Bus_WrAck => user_IP2Bus_WrAck,

351 IP2Bus_Error => user_IP2Bus_Error

352 );

353

354 ------------------------------------------

355 -- connect internal signals

356 ------------------------------------------

357 ipif_IP2Bus_Data <= user_IP2Bus_Data;

358 ipif_IP2Bus_WrAck <= user_IP2Bus_WrAck;

359 ipif_IP2Bus_RdAck <= user_IP2Bus_RdAck;

360 ipif_IP2Bus_Error <= user_IP2Bus_Error;

361

362 user_Bus2IP_RdCE <= ipif_Bus2IP_RdCE(USER_NUM_REG-1 downto 0);

363 user_Bus2IP_WrCE <= ipif_Bus2IP_WrCE(USER_NUM_REG-1 downto 0);

364

365 end IMP;

137行

LED : out std_logic_vector(7 downto 0);

定义IP的端口为LED,这里需要和之前修改MPD文件一致。

232-268行为元件声明

1 ------------------------------------------

2 -- Component declaration for verilog user logic

3 ------------------------------------------

4 component user_logic is

5 generic

6 (

7 -- ADD USER GENERICS BELOW THIS LINE ---------------

8 --USER generics added here

9 -- ADD USER GENERICS ABOVE THIS LINE ---------------

10

11 -- DO NOT EDIT BELOW THIS LINE ---------------------

12 -- Bus protocol parameters, do not add to or delete

13 C_NUM_REG : integer := 1;

14 C_SLV_DWIDTH : integer := 32

15 -- DO NOT EDIT ABOVE THIS LINE ---------------------

16 );

17 port

18 (

19 -- ADD USER PORTS BELOW THIS LINE ------------------

20 LED : out std_logic_vector(7 downto 0);

21 -- ADD USER PORTS ABOVE THIS LINE ------------------

22

23 -- DO NOT EDIT BELOW THIS LINE ---------------------

24 -- Bus protocol ports, do not add to or delete

25 Bus2IP_Clk : in std_logic;

26 Bus2IP_Resetn : in std_logic;

27 Bus2IP_Data : in std_logic_vector(C_SLV_DWIDTH-1 downto 0);

28 Bus2IP_BE : in std_logic_vector(C_SLV_DWIDTH/8-1 downto 0);

29 Bus2IP_RdCE : in std_logic_vector(C_NUM_REG-1 downto 0);

30 Bus2IP_WrCE : in std_logic_vector(C_NUM_REG-1 downto 0);

31 IP2Bus_Data : out std_logic_vector(C_SLV_DWIDTH-1 downto 0);

32 IP2Bus_RdAck : out std_logic;

33 IP2Bus_WrAck : out std_logic;

34 IP2Bus_Error : out std_logic

35 -- DO NOT EDIT ABOVE THIS LINE ---------------------

36 );

37 end component user_logic;

323-352行为user_logic元件例化。VHDL是不区分大小写的。

1 ------------------------------------------

2 -- instantiate User Logic

3 ------------------------------------------

4 USER_LOGIC_I : component user_logic

5 generic map

6 (

7 -- MAP USER GENERICS BELOW THIS LINE ---------------

8 --USER generics mapped here

9 -- MAP USER GENERICS ABOVE THIS LINE ---------------

10

11 C_NUM_REG => USER_NUM_REG,

12 C_SLV_DWIDTH => USER_SLV_DWIDTH

13 )

14 port map

15 (

16 -- MAP USER PORTS BELOW THIS LINE ------------------

17 LED => LED,

18 -- MAP USER PORTS ABOVE THIS LINE ------------------

19

20 Bus2IP_Clk => ipif_Bus2IP_Clk,

21 Bus2IP_Resetn => ipif_Bus2IP_Resetn,

22 Bus2IP_Data => ipif_Bus2IP_Data,

23 Bus2IP_BE => ipif_Bus2IP_BE,

24 Bus2IP_RdCE => user_Bus2IP_RdCE,

25 Bus2IP_WrCE => user_Bus2IP_WrCE,

26 IP2Bus_Data => user_IP2Bus_Data,

27 IP2Bus_RdAck => user_IP2Bus_RdAck,

28 IP2Bus_WrAck => user_IP2Bus_WrAck,

29 IP2Bus_Error => user_IP2Bus_Error

30 );

这几个文件修改后保存。

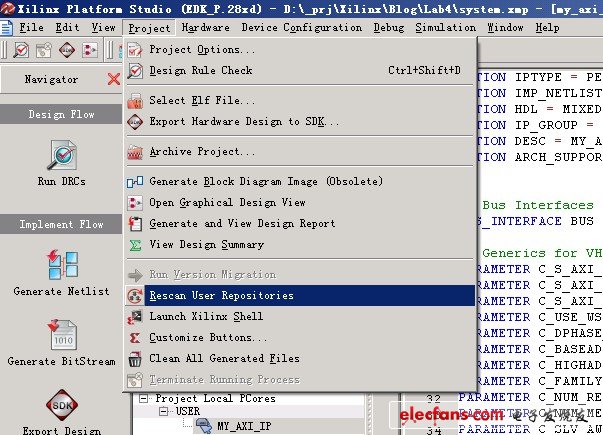

Project->Rescan User Repositories(更新用户仓库?),让XPS识别到对IP所做的修改

三、将自定义IP核添加到PS系统

同第三篇一样,需要将IP添加到PS系统中。

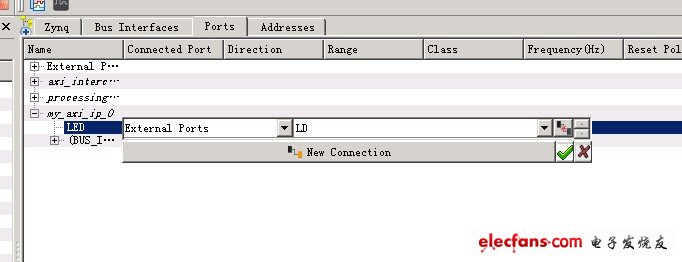

在Ports标签中,需要将我们定义的LED端口设置为外部端口,外部引脚名按照Zedboard的习惯,定义为LD

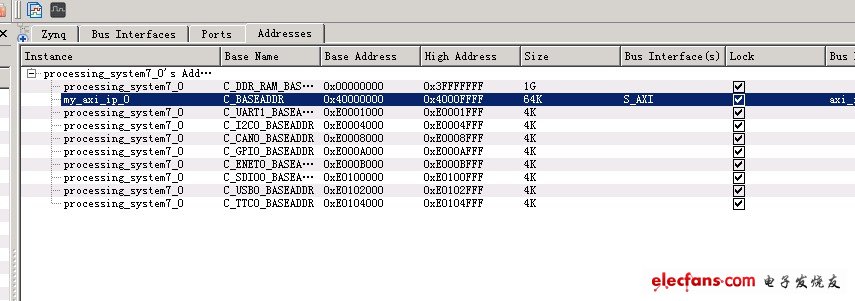

在Address标签中,设定IP的地址。XPS支持自定义定制范围、空间大小等。可以使用默认设置,也可以手动设置。这里我设置基地址为 0x40000000,其实也就是我们设定的数据寄存器的地址为0x40000000。如果有更多的寄存器,会以4字节offset 地址的方式访问即可。

最后一样修改ucf文件,完成约束。

1 NET LD[0] LOC = T22 | IOSTANDARD=LVCMOS33; # "LD0"

2 NET LD[1] LOC = T21 | IOSTANDARD=LVCMOS33; # "LD1"

3 NET LD[2] LOC = U22 | IOSTANDARD=LVCMOS33; # "LD2"

4 NET LD[3] LOC = U21 | IOSTANDARD=LVCMOS33; # "LD3"

5 NET LD[4] LOC = V22 | IOSTANDARD=LVCMOS33; # "LD4"

6 NET LD[5] LOC = W22 | IOSTANDARD=LVCMOS33; # "LD5"

7 NET LD[6] LOC = U19 | IOSTANDARD=LVCMOS33; # "LD6"

8 NET LD[7] LOC = U14 | IOSTANDARD=LVCMOS33; # "LD7"

最后对这个系统编译,生成bitstream文件,并将硬件配置导入到SDK,并启动SDK。

电子发烧友App

电子发烧友App

评论