引 言

随着移动通信的发展。通信网络覆盖范围已经成为衡量通信网络运行的重要标准,直接影响着运营商的经济效益。而直放站的发展应用,已成为提高运营商网络质量,解决网络盲区或弱区问题,增强网络覆盖的主要手段之一。一个基站可以与几个直放站相连,可以组成链状、星型、树型等灵活的拓扑结构,使基站的覆盖范围大大增加。同时,既节省空间,又降低成本,提高了组网的效率。

但由于传统模拟直放站设备间没有统一的协议规范,无法满足系统厂商与直放站厂商的兼容,无法实现基站和直放站之间更有效的互通,从而限制了两者之间控制和数据的可靠传输。2003年6年,由包括爱立信、华为、NEC、北电网络及西门子5大集团合力制定了CPRI(Common Public RADIo Interface)接口。该组织成立的主要目的是制定这个接口的标准协议,从而使该接口成为一个公共的可用的指标。开放的CPRI接口为3G基站产品和2G数字直放站在增加效益,提高灵活性方面提供了便利。

1 CPRI协议概述

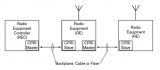

CPRI规范定义了物理层和链路层两层协议,能实现数字基带IQ信号传输时分复用,其协议结构图如图1所示。物理层用千兆以太网的标准,传输的数据采用8 B/10 B编解码,通过光模块串行发送,为达到所要求的灵活度和成本效益,线路比特速率有*.4 Mb/s,1228.8 Mb/s和2 457.6 Mb/s三种。链路层定义了一个同步的帧结构。帧结构包括基本帧和超帧,每个基本帧的帧频为3.84 MHz,包括16个时隙,根据线路比特率的不同,每个时隙的大小分别为1 B。2 B,4 B。其中第一个时隙为控制时隙,其余15个时隙为I/O数据时隙,用来传送I/O数据流。超帧则由256个基本帧构成,256个基本帧的控制时隙共同构成超帧的控制结构(如图2所示),同时,定义了快速C/M通道(以太网)和慢速C/M通道(HDLC),用于传送控制类和管理类的数据,可以对直放站进行维护。

2 硬件实现方案

2.1 方案对比

对于CPRI硬件实现方案,有以下几种方案可以选择:

(1)PMC方案。采用PMC7830或PMC7832芯片,这一类芯片把CPRI协议全部集成在芯片内部,只留出接口,使用简单方便,可完全支持用于无线基站连接的公共射频接口(CPRI)规范。

(2)用带ROCKET IO的FPGA实现CPRI协议,此方法灵活性高,但开发时间周期会比较长,影响产品开发。

(3)FPGA与SCAN25100相结合。由FPGA实现CPRI的成解帧及相关接口设计,SCAN25100负责完成8 B/10 B编解码和高速串并转换。链路层的帧协议修改方便,而物理层则由芯片完成,使用简单,性能稳定。开发成本较低,且扩展性好。

(4)FPGA与TLK4015相结合。TLK4015是4通道、0.6~1.5 Gb/s通道收发器,当系统需要多的通道数时,使用该方案可以减少电路板尺寸。

2.2 硬件详细设计

该设计采用第3种的硬件实现方案,整个硬件实现由5个部分组成,如图3所示,分别为CPRI链路层协议实现模块,CPRI物理层协议实现模块、光传输模块、时钟管理模块和系统配置与监控模块。

2.2.1 CPRI链路层协议实现模块

CPRI链路层只是定义了一个同步的帧结构,而里面的IQ数据和控制管理数据都是由用户按需求自由处理的,采用FPGA实现CPRI的成帧、解帧及相关的控制,处理灵活,方便以后服务增加进行升级。在下面的软件部分做详细介绍。

2.2.2 CPRI物理层协议实现模块

采用国半的CPRI串行/解串器SCAN25100。SCAN25100是专门为CPRI协议设计的高速串并转换芯片,除了串并转换之外,还有8 B/10 B编解码功能,其内部结构框图如图4所示。

图4中的TXCLK和RXCLK都是双边沿采集数据,降低了频率要求,光纤接口(DOUT和RIN)的速率由TXCLK决定,当TXLCK为61.44 MHz时,经8 B/10 B编码,再并串转换后,DOUT的速率就是1 228.8 Mb/s。对于RXCLK也就是接收过程的时钟,可以采用芯片内部自动恢复模式。当作为RE端时,内部振荡器产生的30.72 MHz时钟SYSCLK可以直接作为参考时钟REFCLK,省去一个精准的外部时钟,而且可以利用芯片上的两个锁相环路自动将远程射频单元同步到负责基带处理工作的基站。当作为REC端时,需要由时钟芯片产生30.72 MHz的时钟给SCAN25100当参考时钟。具体应用时,可以使用芯片的配置引脚进行芯片工作模式配置,也可以用MDIO接口对芯片内部寄存器进行编程,达到配置芯片的目的。

此外,该芯片还提供了延迟校准测量功能,通过读内部相应的寄存器值,再进行简单的换算后,就可以得到数据的传输延迟,其准确度达到±800 ps。SCAN25100很好地满足CPRI物理层的功能,性能稳定,省去了8 B/10 B编解码和接收端的时钟恢复,减轻FPGA开发压力。

2.2.3 光纤传输模块

由于CPRI光口的传输速率有*.4 Mb/s,1228.8 Mb/s和2 457.6 Mb/s三种,所以光纤模块应该选用多模光纤模块,可以满足3种速率的不同选择。实现多块单板之间的通信,形成链状和星型混全组网,提高整个数字直放站系统的覆盖范围。

2.2.4 时钟管理模块

对于数字直放站系统,需要用到好几个低抖动、低相位噪声时钟,如SCAN25100,FPGA等,而且电平有LVDS,LVPECL,CMOS等。时钟是整个系统的核心,其性能直接影响整个系统的工作。

AD9516是一款将低相位噪声时钟发生和小于1 ps低抖动14通道时钟分配功能集成在一起的时钟集成电路。内部集成了1个整数n分频的频率合成器、2个参考输入端、1个压控振荡器(VCO)、可编程驱动器、可调延迟线和14个时钟驱动器,包括LVPECL,IVDS和CMOS三种电平模式输出。由于片内集成了VC0,省去了外部振荡器,同时也提高了系统设计的稳定性。3种电平模式时钟输出,丰富了接口方式,给系统设计提供了便利,因此,该系统中采用ADI的时钟芯片AD9516。

2.2.5 系统配置及监控

利用单片机对时钟芯片等进行初始化配置,与FPGA进行通信,实现相应的系统监控功能。

2.3 电路接口设计和PCB布板问题

2.3.1 接口电平

SCAN25100的串口输出是CML差分电平模式,而光纤模块的接口电平是LVPECL差分电平模式,为了实现稳定可靠工作,需要进行接口电平转换,其接口转换如图5所示。

在该系统中,当CML差分输出时,芯片已经在差分输出加了电阻.而光纤模块的LVPECL电平中已经有隔直电容,所以在处理两者之间的接口电平时显得十分简单,可以把两者直接相连就可以解决接口电平匹配问题。

2.3.2 PCB布板

由于是GHz级的设计,对PCB设计的要求较高.对高速差分布线,特别是光模块和SCAN25100接口走线(图4中的DOUT和RIN),应该尽量短且不同层布线,减少收发之间的串扰,增加回流过孔减少其他信号耦合,设计好高速差分走线的阻抗匹配,保证高速串行信号的完整性。

3 软件实现

3.1 单片机

实现SPI通信协议.完成对时钟芯片、A/D与D/A的初始化配置,使得时钟芯片提供多路时钟分别给FPGA.SCAN25100,A/D与D/A。实现I2C通信协议,完成单片机与FPGA之间的通信,从而对数字中频进行设置及监控。实现485总线对整个系统进行监控。

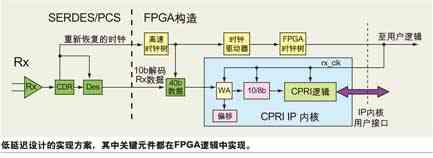

3.2 FPGA

主要是完成CPRI的链路层协议。主要分为3个模块,发送、接收、CPRI启动过程模块。其结构如图6所示,FPGA内部实现CPRI的成解帧和数字上下变频(DDc及DUC.这里不在讨论),发送模块负责把数字下变频数据通过CPRI帧发送给SCAN25100,接收模块则把接收的CPRI帧提取出数字上变频需要的数据。只有当启动模块完成后。输出1个控制信号,数字中频和CPRI之间才能互相传递数据。

3.2.1 发送模块

按照CPRI基本帧和超帧结构,把DDC(数字下变频)的IQ数据信号与相应的控制信号成帧后发送给SCAN25100,SCAN25100再进行8 B/10 B编码,从光模块发送出去。如图7所示,TXMGR模块产生IQ数据和控制数据的使能信号;TXCTRL模块则对CPRI超帧的控制时隙进行状态转换,产生不同的控制信号,从而从FIFO中选择读出不同的控制信号;TXDDR模块则是把数据通过时钟双边沿进行发送。

3.2.2 接收模块

将从SCAN25100接收到的数据进行同步头(K28.5)检测,进行CPRI解帧工作,把控制信号和IQ数据信号分解出来,IQ数据信号送到DUC(数字上变频)。如图8所示,RXDDR模块则是通过时钟双边沿接收数据;RxMGR模块通过检测帧头产生IQ数据和控制数据的使能信号;RXCTRL模块则对CPRI超帧的控制时隙进行状态转换,产生不同的控制信号,从而把接收到不同的控制信号写入FIFO,提供给其他模块。

3.2.3 CPRI启动过程模块

CPRI规范中的启动过程,此过程是相当重要的,需要软件和硬件共同完成。协商确定物理层的协议、慢速通道(HDLC)和快速通道(以太网)的传输速率,完成REC和RE之间的链路建立,从而进行正常的通信过程。在设计过程中,理清各个状态的作用,利用状态机实现启动过程,整个流程如图9所示。

4 实际测试结果

4.1 自环测试

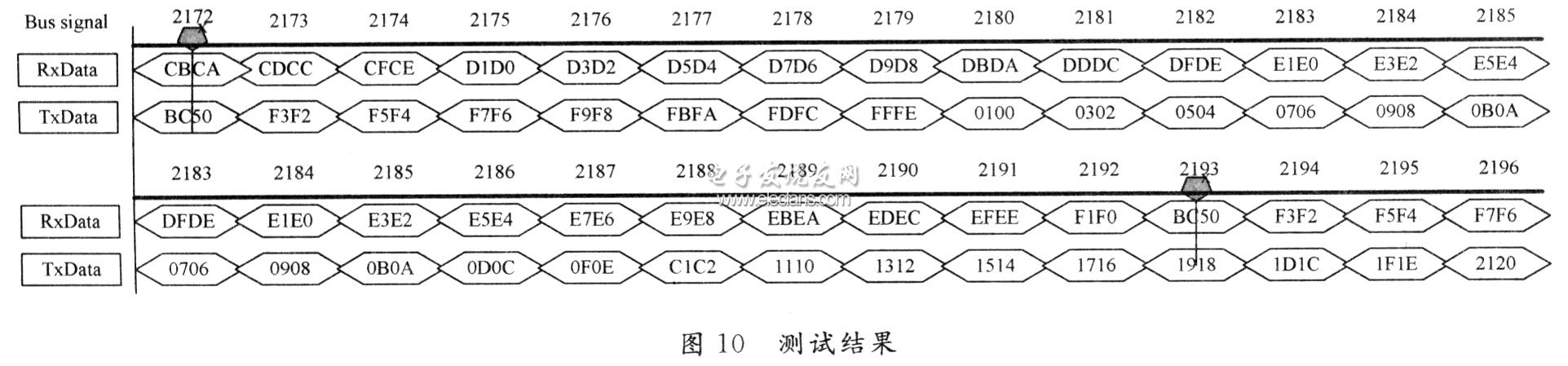

在实验室常温环境下进行实际测试,采用Chips-cope抓取发送和接收的数据进行比较的方法。也就是说,产生一段测试数据,按CPRI帧格式发送给sCAN25100,通过光模块自环回来,如图3所示,然后用Chipscope抓取接收回来的数据,与发送的数据进行对比,确认链路是正常通信。

经过反复测试,该系统已经能正常稳定通信,如图10所示。发送数据(Txdata)帧头为OxBC50,发送时刻为2172,随后的发送数据的高8位和低8位分别以2累加。接收数据(RxData)在2193时刻接收到帧头OXBC50,随后接收到的数据也是高8位和低8位分别以2累加,而且跟发送的数据是一样的。

4.2 联合测试

CPRI模块的成解帧都是在FPGA内部完成的,而数字中频模块(DDC,DUC)也全部在FPGA里面完成设计,如图6所示。两部分的接口显得非常简单,只需要把两部分代码整合成一个工程就行。同样,在实验室常温环境下进行测试,整个系统能正常稳定的工作。

5 结 语

CPRI是规范基站内部REC和RE之间的接口标准协议。该设计把CPRI的两层协议分开设计实现,FPGA实现CPRI链路层,设计灵活。芯片SCAN25100实现物理层,由于芯片具备自动同步及准确校准时延等功能,方便后续设计分布式远程射频基站系统。通过对电路板的实际测试,调整电路设计及PCB部分布线设计,不断地调整优化设计,CPRI模块正常稳定工作,该模块已经和其他模块(DDC,DUC等)通过了联合测试。

电子发烧友App

电子发烧友App

评论