摘 要:单载波频域均衡(SC-FDE)是数字通信中克服多径衰落的有效技术。宽带通信系统中应用单载波频域均衡系统设计,实现137.5 MHz 载波下27.5 Mbps 的码元传输速率。同时在系统中添加1/2 码率卷积码与(239,223)里德-所罗门(RS)码的级联信道纠错编码,提高系统的可靠性。完成单载波频域均衡系统设计,分析设计系统的关键技术,最终在现场可编程门阵列硬件平台上进行系统实现、调试和验证,完成系统实际误码率的测试。

在现代无线数字通信系统中,信号的传输从窄带变为宽带,而宽带无线通信的信道是频率选择性衰落的多径信道。多径效应引起的时延扩展导致严重的符号间干扰(Inter Symbol Interference,ISI),严重影响通信的可靠性,因此需要采用一种有效的方法抵抗信道的影响[1]。目前提出的方法主要有:单载波时域均衡(Single Carrier Time Domain Equalization,SC-TDE)、单载波频域均衡(Single Carrier Frequency Domain Equalization,SC-FDE)和正交频分复用(Orthogonal Frequency Division Multiplexing,OFDM)技术。SC-TDE 在接收端采用一个自适应均衡器来补偿符号间干扰[2]。它的主要部件就是一个或多个横向滤波器,而横向滤波器抽头系数的数目由多径时延来确定。在高速无线通信系统中较大的时延会导致复杂度很高。3GPP(3rd Generation Partnership Project)的长期演进计划中,提出了上行采用单载波技术,下行采用OFDM 技术的方案。

OFDM 系统在发射端通过快速傅里叶逆变换(Inverse Fast Fourier Transform,IFFT)将数据符号并行调制到正交的子载波上,克服了频率选择性衰落造成的影响,在频域实现均衡。其频谱利用率高,系统复杂度较低(与信道最大时延扩展的对数成正比),但是它对定时误差和载波同步敏感,且每个OFDM 符号的多路子载波在时域叠加会产生很大的峰值平均功率比,因而对射频前端的要求较高。SC-FDE 技术综合了OFDM 技术和单载波传输的优点[3-5],同时文献[6]分析指出对于一般的SC-FDE 和OFDM 系统,在低信噪比下OFDM 系统的误码性能略优于SC-FDE 系统,而在高信噪比下,SC-FDE 系统要优于OFDM 系统。本文设计的系统可以实现137.5 MHz 载波下的27.5 Mbps 码元传输速率,实现了宽带SC-FDE 系统。

1 系统设计

1.1 SC-FDE 系统模型

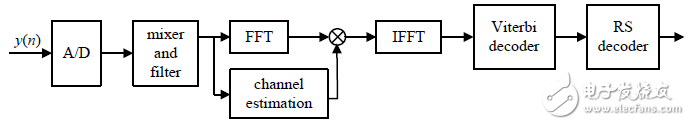

在传统的单载波系统中,接收机主要由A/D 变换、混频滤波、信道估计、信道均衡等模块组成[7-8]。本文在单载波频域均衡传输系统中添加了信道编译码模块,以获得更好的误码率性能。系统采用的是1/2 码率的卷积码和RS 码级联的方案。为提高系统的传输速率,使用了正交相移键控(Quadrature Phase Shift Keying,QPSK)的调制方式,系统框图见图1。

图1 SC-FDE 系统框图

1.2 系统帧结构

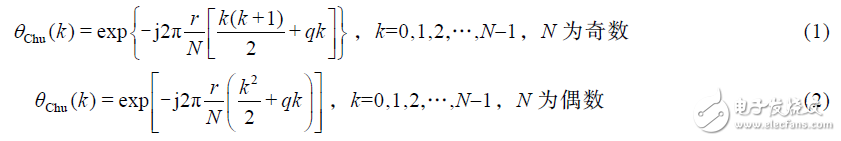

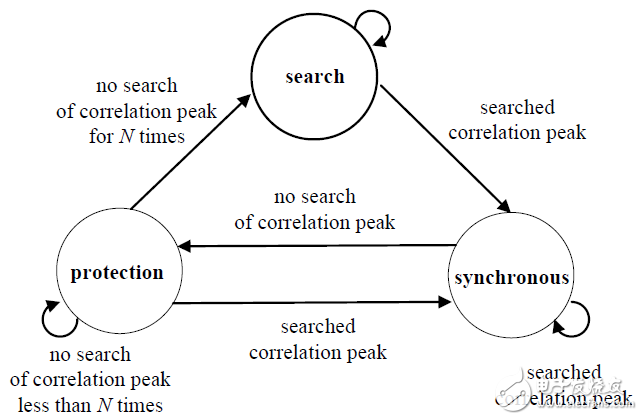

单载波频域均衡系统中使用的数据帧结构是基于独特字(Unique Word,UW)的帧结构,接收端使用UW 完成帧同步、信道估计、循环前缀的功能。而作为UW 的序列应该满足在时域上和频域上均具有较小的起伏。常用的UW 字有Newsman 序列、Frank-Zadoff 序列等。本文使用的是伪叠加序列(Zadoff-Chu)序列,其定义为:

式中:N 表示序列长度;r 是与N 互质的正整数;q 取任意值。

Zadoff-Chu 序列的算法在各种信道环境下的性能都很优越,Zadoff-Chu 序列具有良好的周期自相关和互相关特性,其幅值恒定,并且具有傅里叶变换保持特性。

系统传输帧由2 个完全相同的64 位Zadoff-Chu 序列和1 920 个数据位构成,见图2。每一帧起始位置的2 段Zadoff-Chu序列用来充当循环前缀,完成帧同步、信道估计、噪声估计等功能。数据帧连续传输[9]。

图2 系统帧结构

图3 三态同步图示

2 宽带单载波频域均衡系统中关键技术

2.1 帧同步与频偏估计

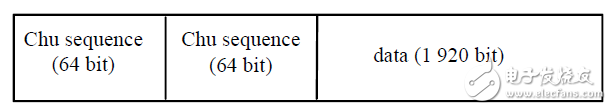

本设计利用UW 完成帧同步,对接收到的每一帧头部的2 段64 位Zadoff-Chu 序列与本地的Zadoff-Chu 序列做相关运算,由于序列自相关特性,会得到一对相关峰(理想情况)或一对主峰和若干对副峰(存在多径)。根据相关峰完成峰值搜索,最终完成信号帧同步[10]。

帧同步采用有限状态机设计完成。状态机的实现采用了基于搜索态-同步态-保护态的三态同步机制,见图3。

频偏估计同样采用搜索到的相关峰来完成,假设载波频偏为Δf,每帧有N 个符号,每个符号的周期为T。设当前帧的主相关峰为p(n),前一帧的主相关峰为p(n–1),则2 个主峰的相位差满足:

式中:Δφ 表示相位差;arctan 表示取反正切角; p*表示取 p 的共轭值。

载波的频偏为:

式中:Re[]表示取复数的实部;Im[]表示取复数的虚部。

由于相偏相对较小,实际设计中可以只使用虚部完成计算,以降低复杂度。设计帧长度为2 048 位,故采用本方法所能纠正的最大频偏为:

。

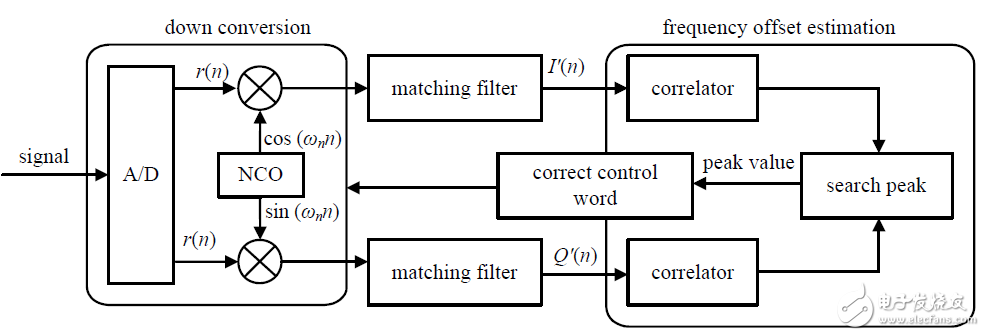

同步与频偏估计的实现框图见图4。

图4 同步与频偏估计

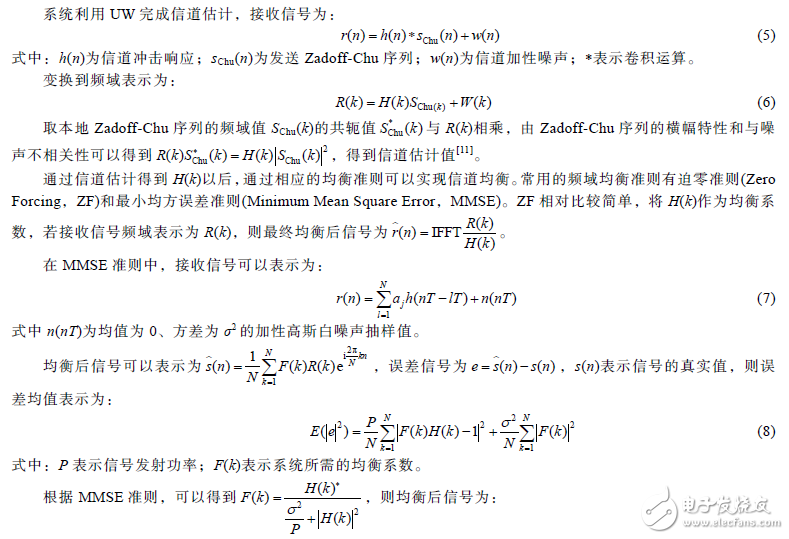

2.2 信道估计和均衡

3 FPGA 实现与测试

3.1 FPGA 实现

系统在XILINX 的xc4vlx160 上完成设计验证、调试和实际测试。系统实际测试见图5,一台电脑与安捷伦E4438C 相连接,通过matlab 设计发射机控制矢量信号发生器产生发射波形。发射机设计载波频率为137.5 MHz,符号速率为27.5 Mbps,系统采用QPSK 调制来增加传信率。信道编码模块使用码率为1/2 的卷积码与(239,223)RS码级联的方式。E4438C 的RF 端口连接到硬件平台的ADC 接口,通过示波器和另一台电脑上安装的chipscope观测接收机的各项信息,完成验证和测试。系统接收机主要由以下几部分构成:模拟前端、频偏估计、帧同步、频域信道估计和均衡、信道译码。

图5 系统实际测试

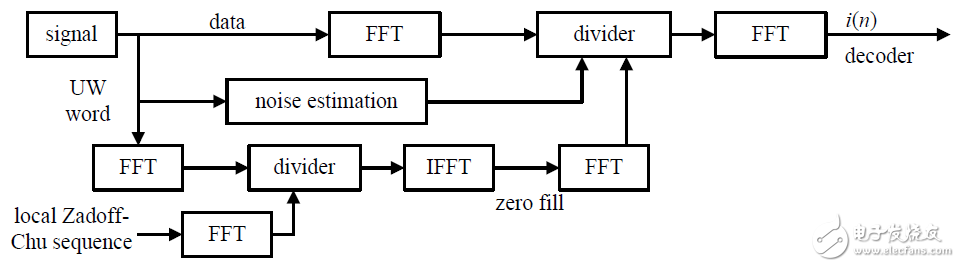

图6 频域信道估计和均衡

频域信道估计和均衡是系统中较复杂的部分,涉及到FFT、IFFT、除法器、乘法器、RAM、ROM 等XILINX IP 核。硬件实现结构见图6。均衡时,需要对接收帧做2 048 点的FFT 和IFFT,这导致系统硬件开销和时间开销很大,难以满足实时处理的要求,因此采用乒乓操作的结构,配置FFT 核为基4 突发模式。此举虽然增加了硬件开销,但能够满足处理的时间需求。此外,鉴于除法器的硬件开销很大,在设计上使用查找表的方法将除法器转化为ROM+乘法器的结构来节省资源。

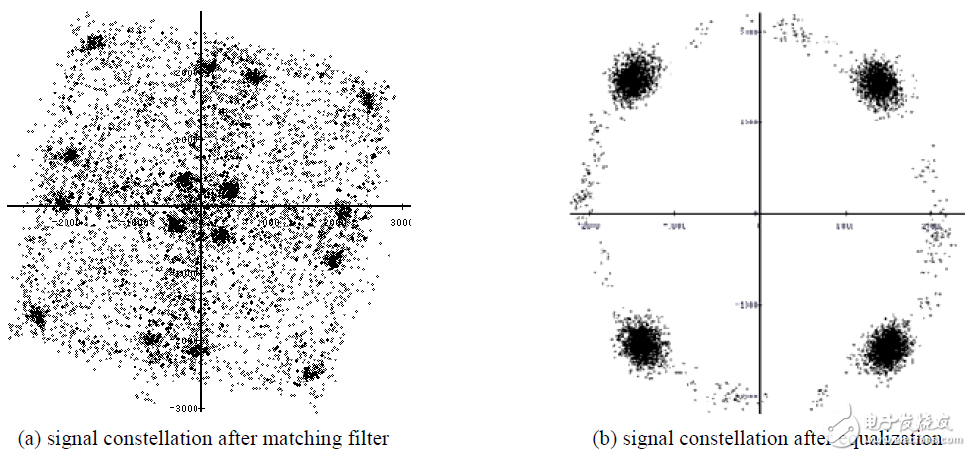

在多径能量–3 dB、延时30 个符号的信道条件下均衡前后实际系统星座图对比如图7(a)和图7(b)。图中能明显看出均衡后信号的星座点汇聚成4 个点。

图7 均衡前后星座图对比

经过信道均衡后的数据已经可以作为接收数据,但为了获得更高的系统性能,均衡后的数据还要经过信道译码模块。系统设计实现了Viterbi 译码器和GF(28)域中任意长度下纠正8 或4 个错误的RS 译码器,本文不再详细介绍。

3.2 测试结果

系统在硬件平台上完成实测验证,使用Agilent E4438C 信号源获得发射信号,发射波形由matlab 编写配置文件来完成,接收端设计误码率统计模块统计系统性能。系统共占用FPGA 资源40 344 个Slice,占总量的29%。

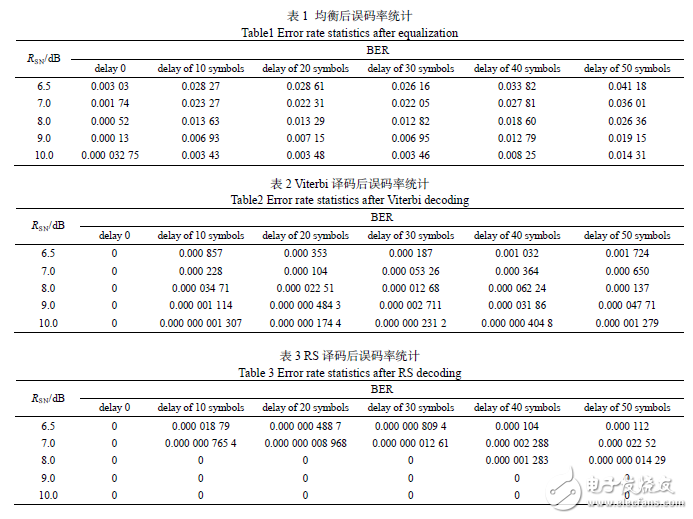

测试环境下信道包含1 条主径和1 条多径,多径能量为–3 dB,分别测试信噪比为10 dB,9 dB,8 dB,7 dB,6.5 dB,没有多径及多径时延为10,20,30,40,50 个符号时的误码率情况,每种条件测试2.048×107 个数据,获得均衡后、Viterbi 译码后、RS 译码后的误码率统计见表1、表2、表3。

表中第1 列表示RSN,第1 行表示时延(Time Delay,TD),以延时符号个数为单位。

由表1 可以看出,随着信噪比的下降,均衡后误码率会有较大变化,当信噪比下降到6.5 dB 时,误码率达到10-2 量级;随着多径时延的增大,误码率略有提高。对比表1 和表2 可以看出,在总体趋势保持基本一致的情况下Viterbi 译码后,除6.5 dB 下时延40 个和50 个符号的情况之外,误码率下降到10-4 量级,这说明Viterbi译码有效地纠正了均衡后系统的错误。对比表3,RS 译码后在信噪比为7 dB 以上时,除去时延50 个符号的情况下,误码率下降到10-6 量级,即使在6.5 dB 的情况下,也能达到10-4 量级,显然性能又有显著的提升。

4 结论

本文设计了宽带单载波频域均衡系统并完成FPGA 实现。实现了137.5 MHz 载波下27.5 Mbps 的码元传输速率,并在MMSE 准则下完成频域均衡,此外添加了卷积码和RS 码级联编译码。最终在Virtix-4 芯片上实现整个系统,并分别对均衡后、Viterbi 译码、RS 译码后的误码率性能做了统计和对比,测试结果表明本系统可以很好地实现宽带单载波通信。

电子发烧友App

电子发烧友App

评论