而射频 (RF) 半导体和计算加速技术的不断发展极大的降低了SDR 硬件成本,简化了相应的软件实施,以更低的价格开辟了新应用。机遇来自当前的下一个大事件 — 物联网 (IoT),以及发展中国家的低成本重新配置无线电,还有发烧友的开放平台等。

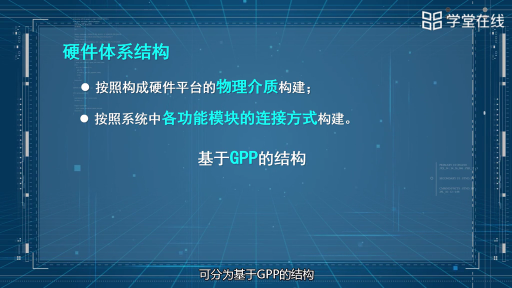

发展的焦点是 SDR 体系结构的关键成本点。进行讨论的一种方法是了解大部分 SDR 实现有哪些相同的部分,技术变革是怎样影响它们的。

深入基带

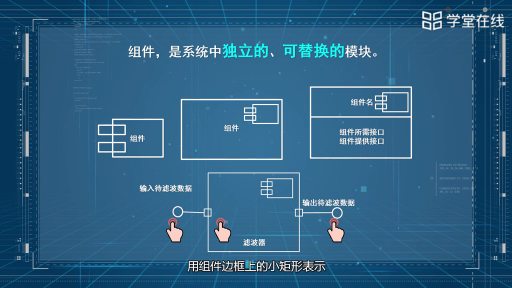

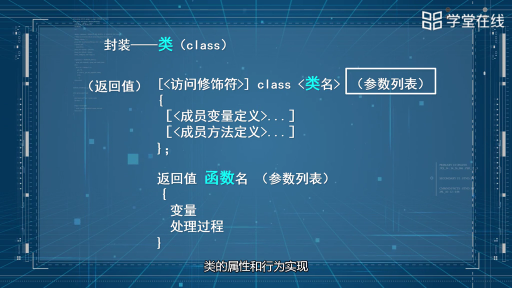

从最终用户的角度看,SDR 系统的主要模块是可编程基带处理器。要理解整个概念实际上是从这一模块开始的。在其中,计算电路完成的功能包括,把输出数据变换成基带频率范围内的调制波形,把输入的数字化基带波形变换为接收数据。

SDR 概念很简单:如果您只是处理数字数据,那么在数字信号处理器 (DSP) 等可编程处理器而不是固定硬件上完成这一工作。然后,您可以通过修改在处理器上执行的软件,来修改滤波器、调制方法、纠错算法,以及数据包或者数据流协议。

这是一个很强大的概念,但确实有些乐观了。能够满足复杂的算法、数据速率和基带频率要求的可编程引擎必须非常强大:例如,最快的 DSP 芯片,或者高端 FPGA。这实际上限制了基带处理器的成本,无法发挥其可移植性和易于编程的优势。

深入 RF

基带处理器并不是 SDR 概念中唯一的难题。信号链的下一环节是数据转换:发送器的数模转换,以及接收器的模数转换,还有相应的模拟滤波器。那么,必须要有上下转换器实现信号在基带和 RF 之间的转换,还要有滤波器和放大器:发送侧的预驱动电路,当然还有接收侧的低噪声放大器 (LNA)。最后是采用不同工艺技术的独立组件:功率放大器 (PA)、天线放大器,以及天线开关等。

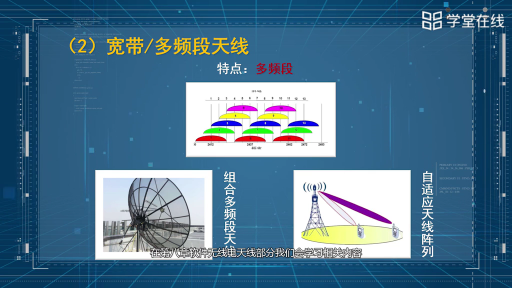

这些 RF 模拟和混合信号组件的问题在于它们本质上不是可编程的 — 传统上是采用固定功能 RF 模拟组件实现的。虽然您可以通过修改软件来改变 SDR 的基带功能,但是改变载波频率或者射频带宽意味着完全改变或者复制硬件组件。

聪明的设计人员想出了解决方法 — 可调振荡器、可调滤波器和增益可调放大器,通过负载寄存器来调整它们,从而管理模拟通路。但是这些方法起到的作用有限 — 要满足大范围可调模拟组件的带宽和线性度要求,必须付出很大的成本和功耗。因此,多频段、连续可调SDR会需要多组RF信号通路,包括从本地振荡器直至天线的所有通路。 在很多潜在的大批量应用中,这种限制带来了成本、体积和功耗问题。对于认知无线电等某些特殊应用,信号会出现在宽带频谱的任意位置,无法满足多个 RF 链的需求。

虽然面临很大的基带计算负载和多个 RF 收发器难题,但 SDR 显然能很好的工作。它用在发达国家的高端军事和应急响应应用中,否则就要采用填满了各种单一功能无线电设备的机箱或者机架。它还用在商业应用中,这类应用的协议、调制和频带的组合是有限的,而且是事先知道的。而其他领域的应用机会还有待挖掘。

达到成本点

很显然,低成本 SDR 平台会有很大的市场潜力。重新认识到这一点,业界在成本问题上双管齐下。一方面是寻找以高性价比实现可编程基带处理器的方法。另一方面是使用统一的宽带可配置 RF 收发器。

基带问题是两个问题中最难解决的。PicoChip 等风投公司早期的工作表明 — 该公司后来被 Mindspeed 技术公司收购,相继被 Intel 收购,对于蜂窝小区基站,中等规模的简单 DSP 引擎阵列能够非常高效的支持基带处理。

最近,另外两种体系结构方法展示了很好的结果,这两种方法都是基于通用 CPU 内核辅以计算加速器这一概念。当 SDR 要突破调制方法和协议相对有限的应用范围时,具有通信加速器的高端微控制器展示了优异的能力。例如,可以使用 Freescale QorIQ MCU 来实现 LTE 基带。

没有以前的基带限制要求,设计团队可以使用相同的底层体系结构,但是加速器功能在 FPGA 中实现。好消息是工艺和集成技术的发展使得这些设计能够在价格合理的小系统 FPGA 中实现,有没有集成 CPU 内核都可以。 Lime 微系统公司 CEO Ebrahim Bushehri 解释说:“例如,如果您要支持 OFDM LTE,那么,基带处理器需要加速功能才能实现快速傅里叶变换和 turbo 编码,还有协议堆栈卸载等。取决于您要处理的功能范围,您可以在通用 DSP 芯片、FPGA,或者在 ASIC SoC 中实现这些功能。利用 FPGA 替代方案,您可以灵活的试验并研究不同的空中接口。它保证了您的数据转换器有正确的硬件接口。”

处理收发器

电子发烧友App

电子发烧友App

评论