无线通讯市场的趋势一直朝向低成本、低消耗功率、小体积等目标。短距离装置产品(Short-Range Devices )更在无线传感器网络(sensor network) 概念的推波助澜下,带动了射频芯片(RF IC)的需求量大增,射频收发器 (TRX)要达到低功耗设计,低电压工作是必要条件,然而,电路的效能与工作电压有关,在兼顾到效能与低功耗之间,是一个很大的挑战。近年来,RF IC之制作技术日新月异。高速、低功率组件更是众所瞩目之焦点,目前0.13um RF CMOS工艺的晶体管,fT 值可达到60 GHz,这表示CMOS晶体管有足够的能力来处理高频信号,所以产业界的主流几乎以RF CMOS 技术,致力于低功率RF IC的优化与研究。

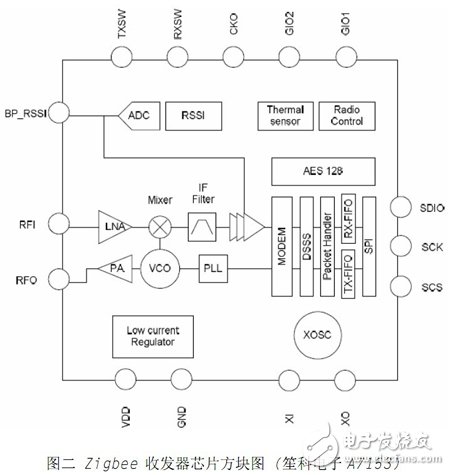

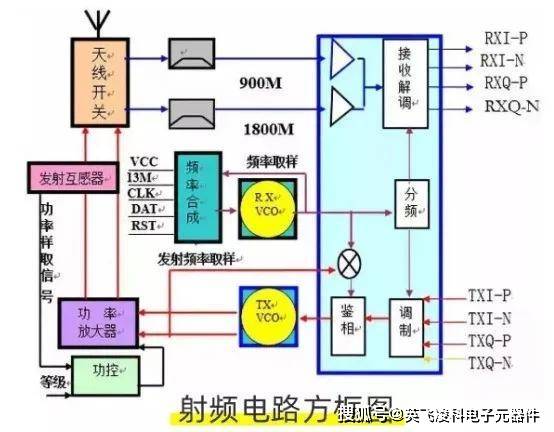

本文将以笙科电子的2.4GHz IEEE 802.15.4 射频收发器 (适用于 Zigbee 标准,RF4CE则是基于Zigbee的遥控器应用规范) 为例,介绍超低功率CMOS无线射频芯片的设计概要,从电路设计到系统观点,向读者说明芯片设计和应用需要考虑的地方。该芯片设计考虑必须涵盖,通讯标准规格、电路的行为模式。在接收部分,介绍了2.4GHz 射频信号从天线接收后,进入LNA放大信号,经由Mixer,Filter,Limiter,RSSI,最后到达数字解调器,最后把接收数据存入RX-FIFO。另一方面,TX-FIFO内的数字信息经过VCO与双点差异积分调变器(two-point delta-sigma modulation) 调变,把调变后的射频信号透过PA放大,最后经由天线辐射出去,本文亦会从系统观点,提出天线与PCB硬件设计重点,加上软件控制,协助读者理解如何透过A7153实现低功耗的Zigbee 或 RF4CE射频网络。

Zigbee 调变方式与PA设计的考虑

2.4GHz Zigbee 标准定义250kbps展频(DSSS)数据传输速率,并采用偏移四相移键调变加半正弦脉波整型调变方式(Offset-QPSK with half-sine pulse shaping),其等效于最小频移键调变(MSK)。MSK相较于相移键调变(PSK)或正交分频多任务(OFDM),是一种恒包络(constant envelope)的调变方式,因此可以选用线性度不高但效率较高的功率放大器,以降低TX功耗。

TX发射器设计考虑

数字调变系统中,IQ调变是一种常见的架构。该架构将调变的Data分成IQ成分,经由半正弦脉波整型及数字模拟转换器(DAC)转成模拟IQ讯号。再透过四相混频器(quadrature mixer)升频至RF讯号。由于IQ讯号使用数字电路实现,因此有较准确的调变指数(modulation index),缺点是需要较多的电路。

另一方面,由于2.4GHz Zigbee调变等效于MSK,而MSK可视为频移键调变(FSK)的一种,因此可以利用压控振荡器(VCO)来实现频移。由于不需要混频器等电路,因此得以降低电路复杂度及功耗。VCO调变设计有两种,其一为开回路(open loop),其二为闭回路(close loop)。开回路调变直接利用数据控制VCO频率,而未使用锁相回路(PLL)或将PLL断开。这样虽可拥有较低功耗,但因频率未被锁住,会有恼人的频漂(frequency drift)问题。

相对而言,闭回路系统通常采用delta-sigma modulation,它的方法是改变PLL除频器的除数,进而改变锁相频率,其结果的VCO频率是牢牢被锁住的,因此可以解决频漂的问题。但是受到回路频宽(loop band-width)的限制,通常适用于低数据率的系统。想要利用闭回路架构达到高数据率,则可采用双点差异积分调变器(two-point delta-sigma modulation),即在差异积分调变上加入VCO调变。数据经由差异积分调变的路径上有低通(low pass)的效果,即高频数据会被滤掉。相对地,在VCO调变的路径上有高通(high pass)的效果。两者互补的结果,即可完整地调变数据。

值得注意的是,VCO的电压对频率转换曲线,会因半导体工艺而有变异,因此需要额外的校正电路来校正频移量。若设计的VCO有较线性的电压对频率转换曲线,则可大大降低校正电路的复杂度。

RX接收器设计考虑

零中频(Zero-IF)及低中频(Low-IF)是易于实现整合型接收器的两种架构。零中频接收器是将RF讯号降频至基频(base-band),然后用模拟数字转换器(ADC)转成数字讯号,再用数字讯号处理器(DSP)将数据解调出来。由于中频频率为零,因此通道选择(channel selection)只需要用低Q值的低通滤波器,低Q值通道选择滤波器的消耗电流也相对较小。但零中频接收器也具有一些缺点,例如直流偏移(DC offset)及闪烁噪声(flicker noise)。为了解决这些问题,必须增加额外电路及功耗。

低中频接收器则是将RF讯号降至适当的中频,以舒缓上述直流偏移及闪烁噪声等问题。但是低中频接收器则有映像干扰(image interference)的问题,因此低中频接收器需要映像抑制(image rejection)滤波器,同时,通道选择滤波器必须采用带通滤波器(BPF)。这使得滤波器所需的Q值较高,也比较耗电。

FSK(或MSK)系统相较于ODFM或PSK,最大的优势就是简单的解调器,简单的解调器也代表了较低功耗设计。FSK调变可用非同调(non-coherent)解调。非同调解调器不需解调载波(carrier)、不用模拟数字转换器(ADC),也不需ADC之前的线性放大器或自动增益放大器(AGC),可大幅降低电路复杂度及功耗。但非同调解调的灵敏度较同调解调略差3dB,所以解调器的选择需依芯片接收灵敏度设计目标来取舍。

2.4GHz IEEE 802.15.4 无线收发器实例

从上述综合考虑,以笙科电子的A7153为例。A7153提供了 250kbps 的展频数据传输速率以及范围为- 20 至 5dBm 的可编程 RF 输出功率, 超高接收灵敏度 (-95dBm @ PER<1%)。硬件 MAC 提供 128 位 AES 加密和认证,及SPI 接口。这些接口使得对连接各种MCU变得非常方便。

A7153整合了RF IC所需的模拟电路,如VCO (良好的VCO曲线线性度,提供双点差异积分调变器在高低温工作条件下的稳定性)、闭回路系统PLL、PA (及其匹配电路)、RF switch、LNA(及其匹配电路)、Gilbert-cell 混频器(Mixer)、映像抑制滤波器,以及限制器(limiter)。A7153的Mixer与LNA设计成增益可调,用来提升整体接收器线性度表现,*断混频器设计好坏的指标为IIP3,IIP3数值越大,代表着第三阶交互调变讯号会干扰到欲接收讯号的程度越低,也就是线性度较好,不幸的是,在射频电路设计中,增益与线性度经常要互做取舍。天线接口部分,A7153内建的PA及LNA的脚位型态(pin configuration)上,采用单端(single-ended)输出入合并设计,因此可省去外部昂贵的平衡非平衡适配器(balun)。为达更长的传输距离,笙科电子也提供CMOS工艺的整合型高功率PA(A7700,含LNA)。A7153整体电路均采用低电压设计,低电流驱动架构,达成低消耗功率的目标。

另外,A7153整合了晶体振荡器(crystal oscillator)的负载电容及PLL滤波组件,大幅减少了外部被动组件。基频部分整合了许多功能,包含TX-FIFO与RX-FIFO,自动序码(preamble)添加、同步码及CRC检查码,展频码。此外,A7153内建的AES-128 硬件加速器,提供软件工程师很容易实现符合Zigbee (IEEE 802.15.4)安全标准之CCM*模块。支持载波感测多重存取 / 碰撞避免机制(CSMA/CA,Carrier Sense Multiple Acces/Collision Avoidance)沟通方式,含自动应答(Auto ACK)功能,信道能量侦测(ED)及连结质量指示(LQI) ,大幅降低MCU的负担及功耗。

Zigbee硬件应用层次

设计Zigbee射频模块,需要用到许多微波电路知识,比如说将PCB Trace等效为天线、传输线、阻抗匹配、讯号反射、绝缘层材料选择、驻波处理,地面(Ground Plane)完整性等,这些因子均会影响RF模块性能表现及EMC问题。

RF PCB设计最基本的是把电源处理、地面完整性,RF走线、敏感电路和数字信号一一分区处理。因此,零组件布局是RF设计的关键,一般来说,最先处理的是RF路径及Xtal路径上的零组件布局,比如说两个电感布局不要平行靠在一起,因为这将形成互感,造成信号干扰,因此最好将两个电感放成直角排列,让互感减到最小。其次是提供RF IC最需要的干净电源,电源一定要滤波,电源去耦组件要尽可能靠近IC引脚并接地,同时考虑PA启动瞬间,瞬时大电流需求的电源问题,另外,电源走线要越短越好,并远离RF信号线或Xtal等干扰源,(电源问题常常造成异常的RF效能与EMC问题)。

一般使用双层的FR4 PCB时,会将主接地面安排于PCB下层,RF讯号走在表层上。在所有PCB设计中,尽可能将数字电路远离仿真电路是不变的原则,它同样也适用于RF PCB设计。当一些高速信号线要穿过了破碎的地面,这绝对不是一件好事,必须尽可能避免,所以要保持PCB下层地面的完整性。针对PCB上层的走线,亦应避免形成过多的游离地,因为它们会像一个小天线,提供干扰源侵入的路径。在大多数情况下,可以把这些游离地去掉。

笙科电子A7153的参考模块,其PCB天线采用F型天线拓扑结构,支持全向辐射场形。要把天线的性能发挥到极致,从应用的角度来讲,RF模块的天线最好伸出母版的边缘,RF模块下面的母版最好不要走线。RF模块和产品外壳的整个设计也会影响天线的性能。粗劣的设计会影响天线场形,使发送信号出现反射、折射、散射,结果造成传输距离的大幅缩短。以下的一些设计指南有助于确保天线的性能,比如,不要直接在模块的天线下面设置接地面或布铜线,天线要尽可能远离金属物体,PA路径下方,尽可能保有一块完整的地面。

Zigbee软件应用层次

Zigbee 设备最常采用的省电方法是使传感器进入周期性的睡眠状态,以便获得长久的电池寿命。也就是说,A7153为了进一步降低平均功耗,内建了无线唤醒机制,MCU先启动A7153的无线唤醒机制,然后进入睡眠模式。此时,除了低功耗无线唤醒定时器仍在运作外,其余电路均自动进入睡眠模式。待定时器数到预定时间时,A7153会自动进入接收状态,去侦测有无射频封包。若有,则收下封包并唤醒MCU,待微控器下达进一步指令。若在某预定时间内未侦测到封包,则A7153又会自动进入睡眠模式并重新开始计时,形成周而复始的工作周期(Duty Cycle),直到收到封包。

由上述可知,工作周期(Duty Cycle)的长短直接影响数据传输效率以及能源的消耗,长工作周期可以增进数据传输效率但是功耗较多,短工作周期可以节省能源消耗但传输效率下降。A7153提供Zigbee定义的16个射频通道 ( RF4CE 则是从16个信道取出三个信道,分别为2425M / 2450M / 2475MHz),MCU只需改变A7153一个缓存器,即可达到换频。MCU亦可利用A7153接收端讯号强度指示(RSSI),得知当下网络上讯号强度,计算出贴近网络质量状况的真正表现。另外,透过CSMA/CA沟通方式,可获得更理想的传输效能,同时大幅地降低了封包碰撞的能量消耗。

Zigbee也定义了一个带有时间同步标志的可选超帧(superframe)结构,高优先级通信的 GTS (Guaranteed-Time-Slot)机制,保障无延时或竞争的通信,支持高达 65,000 个节点,不同型态的网络拓扑 (星形、丛集或网状)。极低的工作周期(duty cycle)可以让使用钮扣电池的节点持续运行数年。

当软件工程师启动AES128加密功能时,A7153仅在发射或接收数据封包时才执行。因此,平均功率仍然很低。

RF4CE 射频遥控器--全球新标准

ZigBee 联盟主席 Bob Heile 表示:"RF4CE 为电子产品制造商提供了一种全球性标准,从而简化对各种消费电子设备的操控,并改善用户体验。今后,消费者将享有更大的便利,更加灵活地使用消费电子设备。"笙科电子一直很关注RF4CE的市场需求,基于A7153高性价比(Cost / Performance)的竞争优势,除了满足RF4CE遥控器常见的五大优点外,协入客户使用低成本的MCU,在正成形的RF4CE新趋势,取得成本优势。

1.发射瞬间电流为IrDA的十分之一,因此遥控器可以有更长的电池寿命

2.利用双向通讯,能够定位找不到的遥控装置

3.通用指令集实现真正的互操作性,封包加密,无需使用多个遥控装置

4.能够对摆放在几乎任何位置的设备进行操控,特别是隐密的地方

5.新的交互式功能,增强的用户接口和先进的显示功能

结论

笙科电子的A7153,定位上就是锁定RF4CE相对单纯的点对点架构,该芯片内建简单好用的硬件功能,低功耗的芯片架构,提供软件工程师设计出长电池寿命的RF4CE遥控器。RF4CE标准的背后有国际一线消费性电子大厂力挺,因此,RF4CE被预估为Zigbee 杀手级的应用,成为IEEE 802.15.4最重要的市场,使用者只需选择通用型的8051 (或其它8位单芯片),搭配笙科电子A7153的开发平台,即可设计出成本最佳化的RF4CE遥控器,RF4CE除了逐步取代既有红外线遥控器市场外,势必还有"异"想不到的应用躲在暗处,等着有创意的读者来寻宝。

电子发烧友App

电子发烧友App

评论