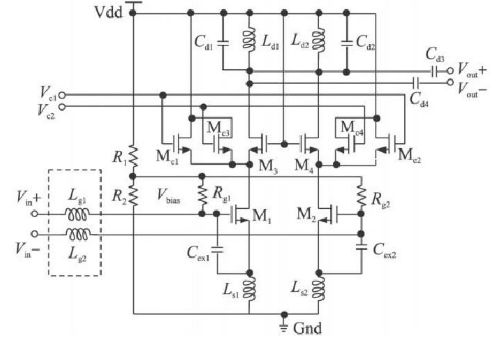

由于该电路结构具有较高的隔离度,输出端阻抗的调整对输入端影响不大,可以在输出端单独进行匹配。具体设计过程中,可以首先在输出端只连接漏极电感Ld ,通过仿真其S22参数,仿真其对应频率2. 43GHz下的输出阻抗。然后对照Smith圆图,先并联电容将输出阻抗实部调整到50Ω,再通过串联电容,将输出阻抗虚部调整到0。这样,最后可以将输出阻抗匹配到50Ω,实现输出端功率匹配。

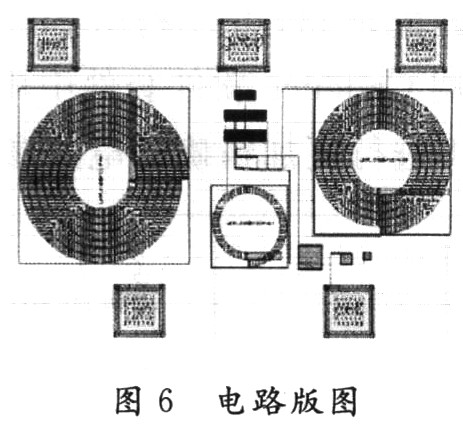

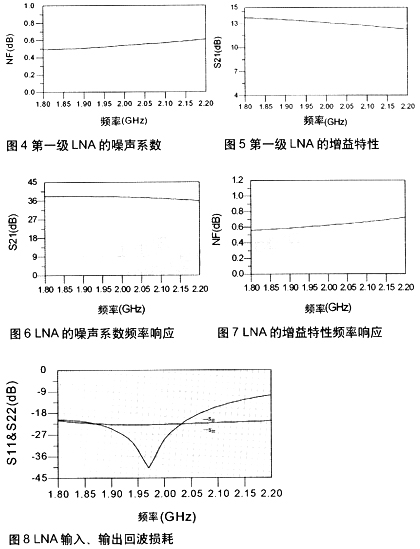

2 低噪声放大器的版图及后仿真结果

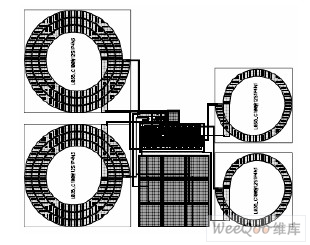

本次设计的低噪声放大器版图如图3所示,芯片面积约为: 735μm ×780μm。因为电路为对称结构,所以在版图的绘制上也需注意对称性,这样有利于提高电路性能。芯片左侧为SGS焊盘,用来接入差分输入信号。芯片右侧为SGS焊盘,用来接差分输出信号。芯片上下端各为三针直流焊盘,用来提供增益控制信号Vc1、Vc2 ,对称的电源Vdd以及对称的地Gnd。在焊盘组间空隙处,增加了电源Vdd到地Gnd的滤波电容组滤除电源Vdd上的纹波,旁路外界干扰,这种结构可以在最大利用版图面积的同时进一步提高了电路性能。

图3 低噪声放大器版图

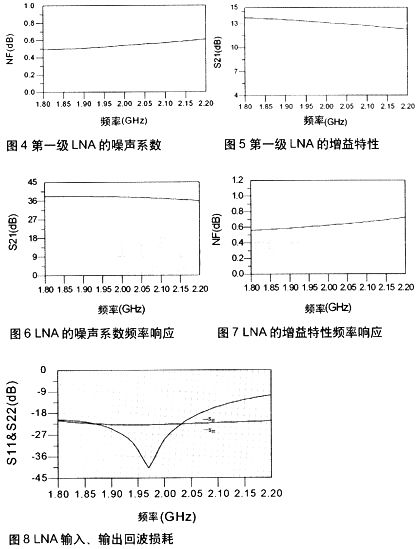

在Cadence Spectre仿真环境下对电路的S 参数,噪声系数NF以及稳定性系数KF进行了后仿真,后仿真在TT工艺角,温度为27 ℃情况下进行。

电路在1. 2 V电源电压下工作电流约为6. 0 mA。

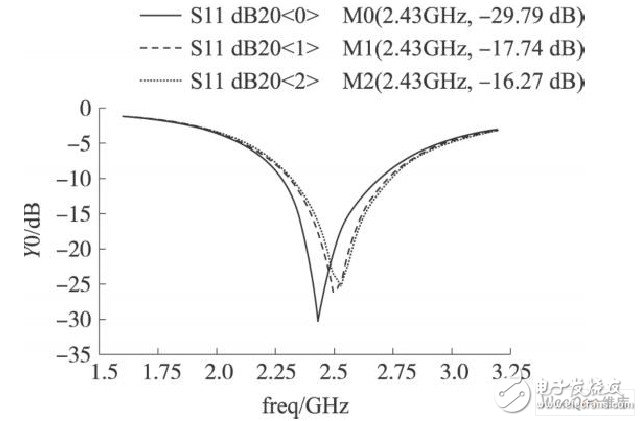

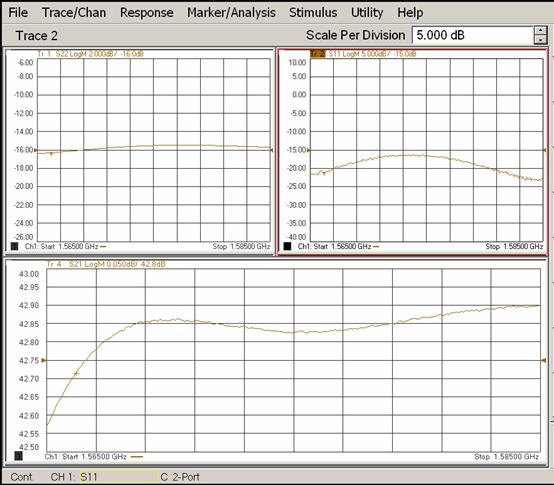

S11后仿真结果如图4 所示,高增益时S11约为- 29. 8 dB,中增益时S11约为- 17. 7 dB,低增益时S11约为- 16. 3 dB。三种情况下S11均满足小于- 10 dB,输入匹配良好。

图4 S11仿真结果

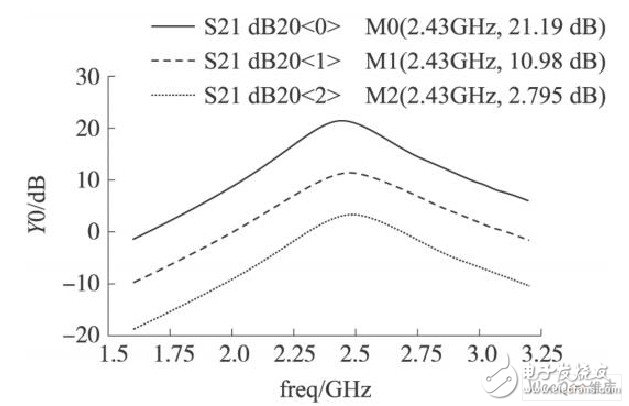

S21后仿真结果如图5 所示,高增益时S21约为21. 2 dB,中增益时S21约为11. 0 dB,低增益时S11约为2. 8 dB。基本满足设计指标中的高增益20 dB,中增益10 dB,低增益0 dB要求。

图5 S21仿真结果

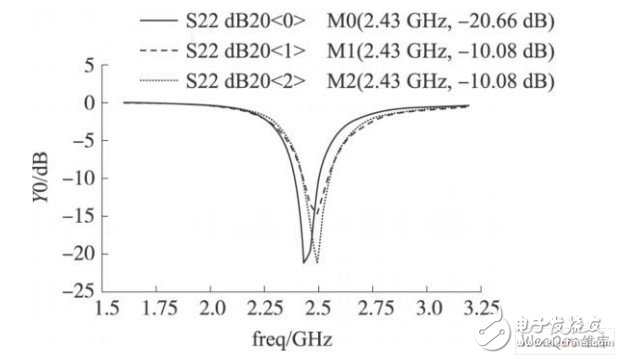

S22后仿真结果如图6 所示,高增益时S22约为- 20. 7 dB,中增益时S22约为- 10 dB,低增益时S22约为- 10 dB。三种情况下S22均满足小于- 10 dB,输出匹配良好。

图6 S22仿真结果

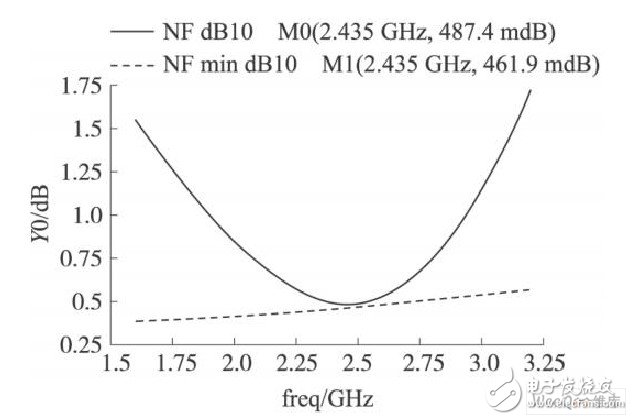

噪声系数如图7所示。在2. 43 GHz上,后仿真噪声系数NF约为0. 49 dB,与最小噪声系数NFmin后仿真结果0. 46 dB比较接近,噪声匹配良好。

图7 噪声系数NF仿真结果

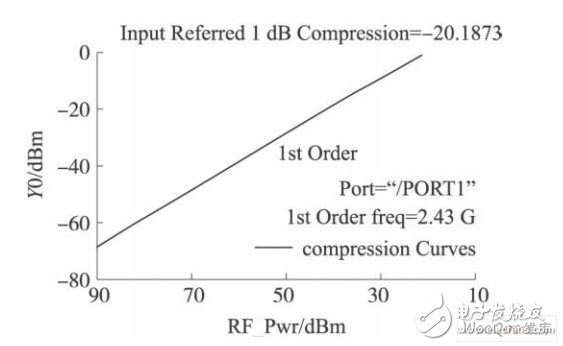

输入1 dB压缩点如图8所示,在高增益下约为- 20. 2 dBm,根据1 dB压缩点与IIP3的关系,可以推出,该放大器IIP3约为- 10. 6 dBm。

图8 低噪声放大器输出1 dB压缩点仿真结果

其它后仿真结果:反向隔离度S12在三种增益状态下均小于- 45 dB;稳定度KF约为6. 2,其值远大于1,放大器绝对稳定。

3 总结

本次设计的低噪声放大器芯片在限定功耗的基础上,保证了较高的增益,同时进行了输入匹配的优化,实现了给定功耗条件下的功率和噪声同时匹配。

该低噪声放大器在最高增益为21 dB时噪声系数约为0. 5 dB,并且通过放大器S11、S22参数反应出其输入输出阻抗功率匹配性能良好。放大器增益控制电路满足设计要求。综上所述,该低噪声放大器性能优良,实现后有望应用于无线传感网射频收发芯片中。

电子发烧友App

电子发烧友App

评论