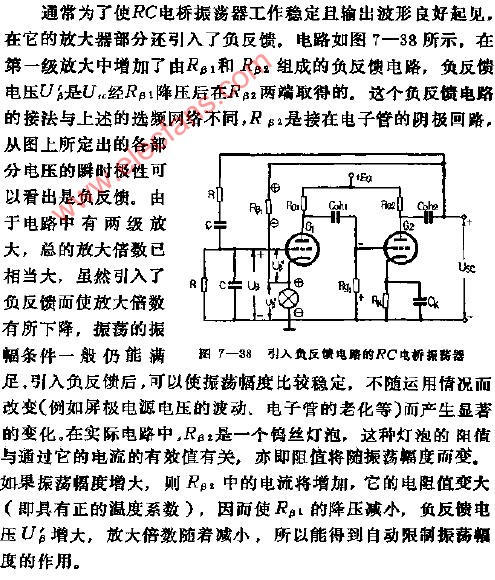

文氏(Wien)网络自1891年由物理学家Max Wien推导出以来,已被用于许多振荡器设计中,其中最著名的是惠普200振荡器。让这个正弦波振荡器的设计与当时的大部分设计不同的关键,是在负反馈分压器中使用白炽灯来稳定恒定振幅电平所需的增益,以及在宽频率范围内稳定的振荡器运行。这是Fred Terman教授给Bill Hewlett(惠普的两个创始人之一)的斯坦福大学硕士论文的建议。Bill Hewlett的音频振荡器变得相当有名,是日后与Dave Packard创立的惠普公司的第一批产品。在Bill Hewlett推出其文氏电桥振荡器之前,大多数音频源都是基于LC振荡器的。

通用无线电公司(GR)自1920年代后期就开始生产音频振荡器,最初是403型,后来发展到1304型。GR音频振荡器由两个LC调谐振荡器组成,一个振荡器是固定频率,另一个是可调的。两个振荡器的输出混合在一起。不在振荡器指定范围内的频率被滤除,所选的频带被放大,且振幅被调平并被控制馈送到振荡器的输出端。这种制造音频信号源的方法昂贵且复杂。由于LC调谐振荡器会漂移,因此难以保证频率稳定性。较低音频频率下的频率稳定性成为LC调谐音频振荡器永无止境的问题。谐波失真是另一个重要问题。

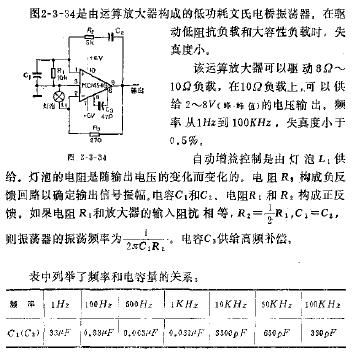

固定或单频文氏电桥振荡器不难设计和建构,因为在文氏电桥网络中可以选配RC组件以实现所需的振荡频率。

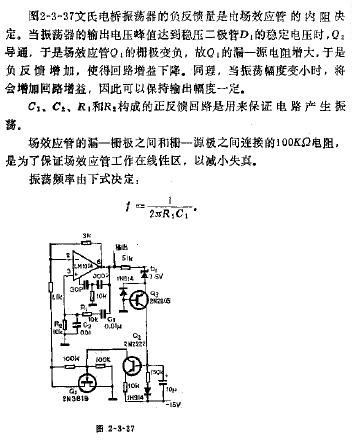

使用Bill Hewlett引入的灯泡发热方案可以实现幅值控制稳定。这种文氏电桥振荡器可以实现非常低的失真,具有良好的振幅和频率稳定性。

由于文氏电桥网络的电阻臂或电容臂中需要一对匹配元件,所以变频文氏电桥振荡器的设计和建构更加困难。这可通过一个双可变跟踪电容器或开关电容值、双可变跟踪电阻器、开关电阻器以及逻辑选择电阻器(数字电位器)以改变频率的方法来实现。

电压调谐的文氏电桥振荡器并不常见,它们可能对设计和建构带来挑战。基于变容二极管(压变电容器)的文氏电桥压控振荡器设计和建构一直存在。另一种调整文氏网络的方法是使用一对匹配的JFET。

Linear Systems推出的双匹配P沟道JFET激发了在文氏网络中使用该匹配器件作为跟踪压控电阻的设想。1967年,Oliver A. Fick和原子能委员会(Atomic Energy Commission)为此申请了专利。专利中有这一概念和设想的描述与图示,但与大多数专利一样,如何使这一设想实际发挥效能的更具体的细节模糊不清,其详尽程度不足以在现实中实现足够好的设计。虽然多年鼓捣测试仪器,从其服务手册中搜集了大量信息,并在网上查找JFET调谐的文氏电桥振荡器的例子,仍没有发现可行的设计。这一设想激发了设计和构建满足功能要求的JFET电压调谐文氏电桥振荡器的好奇心。

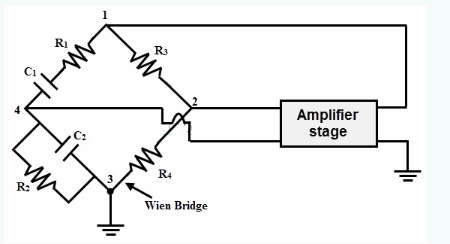

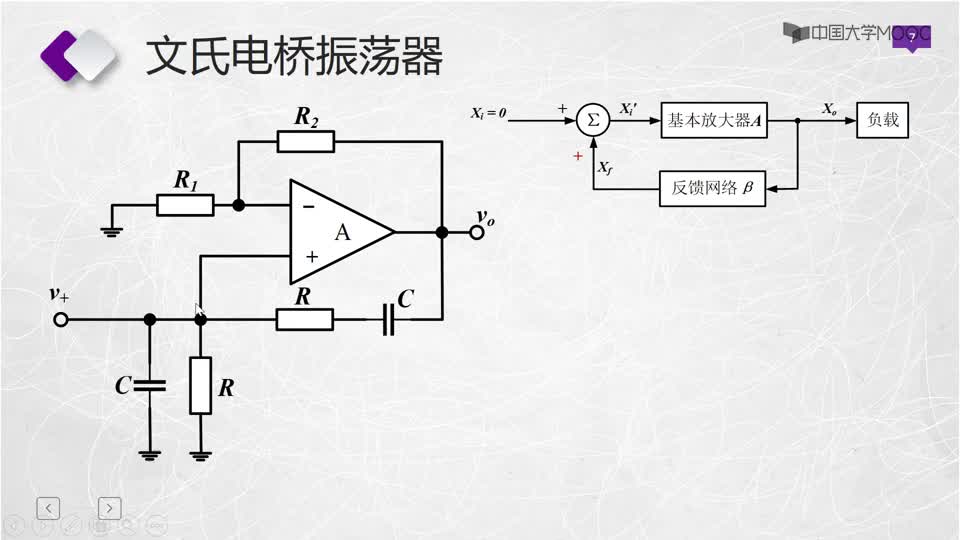

文氏电桥本质上是一个串并联RC网络,当串联和并联RC网络达到平衡时,相移为零。在零相移时,该网络本质上变成一个电阻分压器,可用于将正反馈送入放大器,以产生特定频率的振荡。

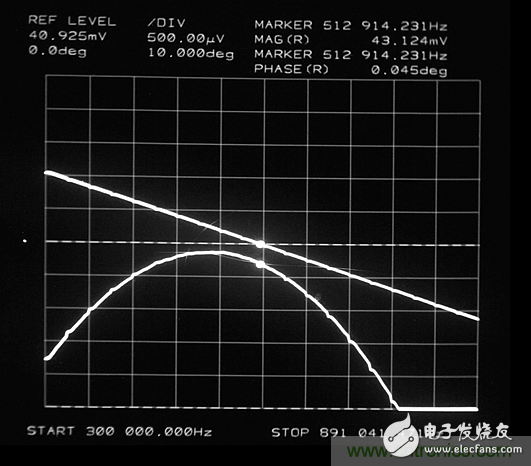

图1:使用惠普3577B网络分析仪的文氏网络分析仪绘图示例。

该文氏网络的电容值为1000pF、电阻为301Ω。由计算得出发生零相位的频率为512kHz,网络分析仪显示接近513kHz。文氏网络损耗约9.5dB或3倍衰减。这是当文氏网络作为正反馈插入到振荡器中时,为了产生振荡,放大器或类似增益器件需要补偿的能量损耗量。增益器件会增加振荡幅度,直到饱和为止。增加一个由参考电压控制的可变增益负反馈环路,通过文氏网络来平整和平衡正反馈的量值,可以得到稳定的振荡器输出振幅和振荡频率。

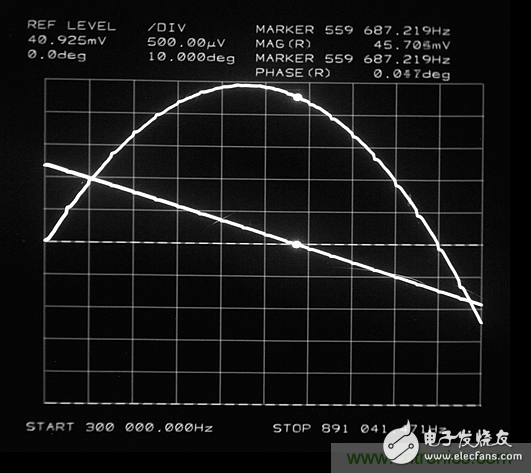

图2:降低文氏网络串联臂的电阻或R值,会导致网络分析仪显示器在平衡状态下幅度略微增加,频率略微上移。

当文氏网络用作振荡器时,稍微增加了其正反馈量。为保持振荡器的恒定电平输出,负反馈环路需要调整并补偿这些动态文氏网络调谐组件的变化。

这是在文氏电桥振荡器中使用JFET作为压控运行元件时需要考虑的一个参数示例。

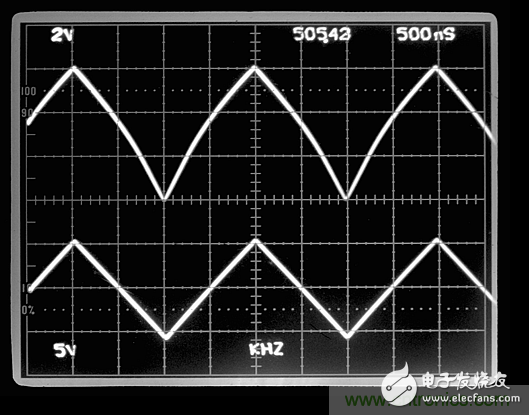

用作压控电阻时,JFET具有与三极真空管类似的基本平方定律非线性传输特性。因为JFET的漏极和源极会增加信号偏移水平,从而导致通道长度调制(通道电阻调制),JFET的这一“个性”就更得以彰显。图3中贯通被测JFET的三角波两边的曲率显示了漏-源阻抗的这些小变化。

双LSJ689的一半配置为双电阻分压器中的一个电阻,由底部的10V峰-峰、500kHz三角波曲线驱动;栅-源极偏置电压约为JFET漏-源极接近最大源 - 漏极电阻时偏置电压的30%。

图3:顶部三角波曲线(曾为直线)边缘呈现了JFET的平方律特性。

大多数JFET的漏极至源极通常是对称的。通过在栅极与漏极之间增加分压器,将栅极连接到分压器中心,该分压器就能有效地向JFET的栅极施加校正反馈。

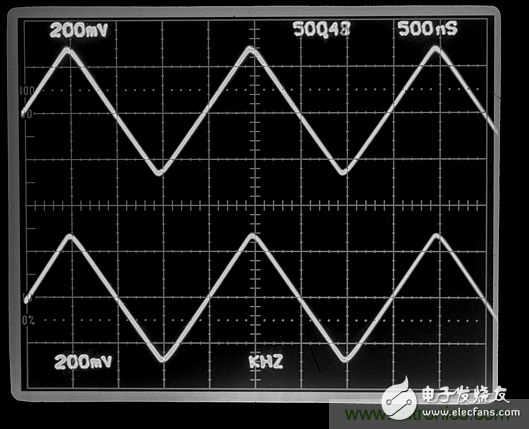

图4:由信道长度调制引起的一些非线性可以得到校正。

将来自JFET的漏极到源极之间的电阻分压器的反馈添加到栅极有助于FET线性化。

将分压器驱动增加到15V峰-峰值电压,以说明被测JFET上漏-源极电阻线性度的改善。

通过降低漏-源极间的信号电平,可进一步降低由漏-源极间压降引起的栅极调制导致的JFET失真。这有效减小了沟道长度调制效应,使JFET的漏-源极之间的阻抗更线性。

图5:顶部迹线,被测JFET的输出三角波;底部迹线,输入到JFET测试分压器的三角波。

JFET不是理想电阻器

JFET不是理想电阻器,尽管有局限,LSJ689中的两个匹配JFET仍足以用作文氏电桥调谐元件。作为P沟道JFET的LSJ689具有正向电压增加JFET漏-源电阻的优点。与需要负向电压增加JFET漏-源极电阻的N沟道JFET相比,前者电压控制更加容易。

栅-源极电压为零时,LSJ689的典型“导通”电阻约为120Ω。数据手册规定栅-源极“OFF”(漏-源极电阻达到该JFET能够获得的最大值)电压在1.5至5V之间。该规范会影响给定栅-源极电压下漏-源电阻的量值,从而直接影响文氏网络的调谐频率和调谐范围。 JFET对漏-源电阻之间的差异将影响文氏电桥的调谐频率和幅度,如网络分析仪图所示。在1MHz、漏-源极电压为15V时,LSJ689具有8pF的低漏-源极电容。鉴于LSJ689的这些固有特征,我们来尝试制作一款250kHz至1MHz、电压调谐的文氏电桥振荡器。

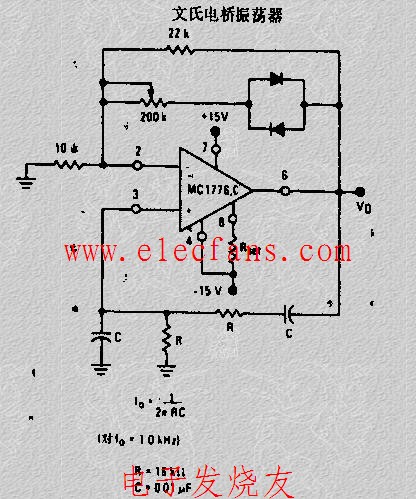

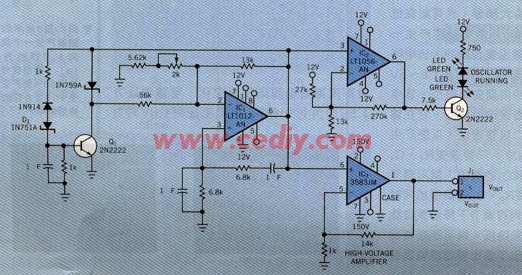

文氏电桥振荡器中用作增益元件的放大器是非常基本的三极管差分放大器,带有互补的发射极跟随器输出部分。设计并不复杂,在1MHz振荡器中具有足够的带宽来工作,具有低阻抗的正和负反馈回路,并且仍具有一定的负载驱动能力。开环增益在14左右,便于反馈回路闭合(振荡所需的增益约为9.5dB或x3),具有合理的失真性能和可接受的DC稳定性。

K489A-K489B是在输入端使用的LSK489匹配的N通道对。该差分对的尾电流由J511电流源二极管设定为约4.5mA,并在差分对的两个JFET间分流。同相输入JFET K489A具有一个1kΩ的负载电阻R9和一个二极管D1。1kΩ电阻将增益设置为约等于2。二极管在R9两端增加了一个二极管压降,帮助补偿和抵消连接到它的共发射极放大器导致的温度影响。反相输入JFET(K489B)作为源极跟随器,增加了该放大器输入负反馈路径的阻抗。

Q2是共发射极放大器(CE),其直流偏置是通过漏极电阻R9和D1两端的压降实现的,增益由直流偏移调整器R11、R12、Re‘’、集电极电阻R13和发射极跟随器输出部分所需的能量设置。可变电阻R11用于调整放大器的直流偏移,通过调整进入R13的集电极电流实现。R13上产生的压降被设定为在放大器的输出端达到接近零伏时的电压。该CE放大器的工作电流为11mA,支持所需放大器的带宽以及发射极跟随器输出部分的驱动需要足够的电流。由于使用本地反馈将该放大器CE部分的增益设置为约等于7,利用Q2的固有集电极-基极电容保证了放大器稳定性。

三个二极管D3、D4、D5产生约1.8V压降,以偏置用作输出级的NPN和PNP发射极跟随器。发射极跟随器上的基极电阻R14、R15是保证良好的振荡稳定性必需的;发射极电阻R16、R17需要在温度范围内保持偏置稳定性。输出部分偏置设置为12mA,允许在驱动低阻抗文氏网络正反馈环路和光敏电阻调制的负反馈环路的同时,仍有一些电流可用于驱动负载。

电压调谐文氏电桥网络包括用作压控电阻器对的LSJ689双P沟道JFET。漏-栅极反馈电阻R3、R6有助于JFET的有效电阻曲线线性化;R2、R5则构成J689A和J689B的栅极分压器。JFET上并联的R4、R7在栅极电压变化时将其可变电阻范围限制在约120Ω到650Ω的范围,同时也有助于JFET的电阻曲线线性化。 C3对JFET调谐电压进行隔离,以远离放大器的同相输入端。 6.8V齐纳二极管限制了可施加到JFET栅极的电压,从而有效限制了这种电压调谐的文氏电桥振荡器的可变电阻范围和调谐频率范围。

R1限制了齐纳二极管D2的电流,C7和R1对进出振荡器的一些高频控制电压进行滤波,C1和C2构成了文氏网络的剩余部分,振荡器频率随调谐电压的增加而降低。

在本文末尾的示意图中,当电压控制(VC)输入为0V时,文氏网络振荡频率约为1MHz,当VC输入为7V时,振荡频率下降到约250kHz,也即每伏下降110kHz。由于JFET固有的非线性,每伏对应的调谐频率并非线性。

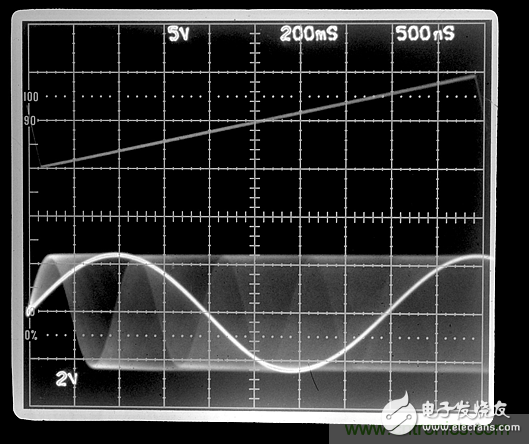

图6:顶部迹线是0V到10V,一个2s的斜坡驱动VC输入;底部迹线是振荡器的输出,从1MHz开始,停止在250kHz;迹线包络说明在其调谐频率范围内具有均匀的振荡器电平输出。

为了控制和稳定振荡器的输出电平,D6、D7、R21构成Q4的1.2V基准电压,从而在发射极电阻R22上产生约0.6V电压,生成2mA的电流源。

这个2mA的电流被施加到D11,D11中注入1.8mA将使R19的电阻降低到约100Ω。在R19为100Ω、固定负反馈电阻R18为619Ω的条件下,放大器的闭环增益增加到约等于7。这一量值的放大器增益加之相关部件的固有噪声就可以启动振荡器。一旦振荡器的输出电平足够高以驱动峰值检测器网络R23、D8、C4,分压器R24、R26就设置基极驱动量值来正向偏置Q5的基极-发射极结。分压器R24、R26还设置了振荡器的输出电平。一旦Q5有足够的基极驱动来克服其基极-发射极电压,那么它还可以用作振荡器电平控制的参考电压。Q5开始导通,电流开始从集电极流向发射极,从而减小驱动D11的电流。减小对D11的驱动会增加R19的阻值,改变R18的分压比,降低放大器增益,稳定并平衡振荡器的输出。振荡器电平控制环路的稳定性由C4、R24、R26和固有的LED光输出到光敏电阻的阻值变化-反应时间(转化为光敏电阻模块D11-R19)所决定。

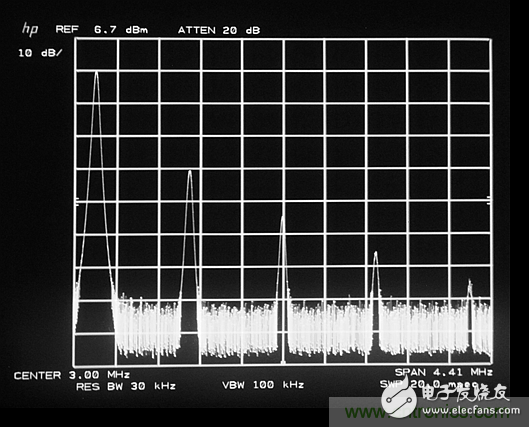

图7:振荡器输出的谐波分量在1MHz时驱动500Ω负载。

电源去耦网络

L1、L2、R28、R29、C5、C6组成电源去耦网络。电感的阻抗随频率的增加而增加,限制了可以进入或离开振荡器的较高频能量的量值。R28、R29消除了网络的潜在自谐振。旁路电容需要一些阻抗来抑制,否则将成为不想要的循环电流发生器,从而导致意外的问题。

振荡器+/-15V电源直接连接到22μF旁路电容。

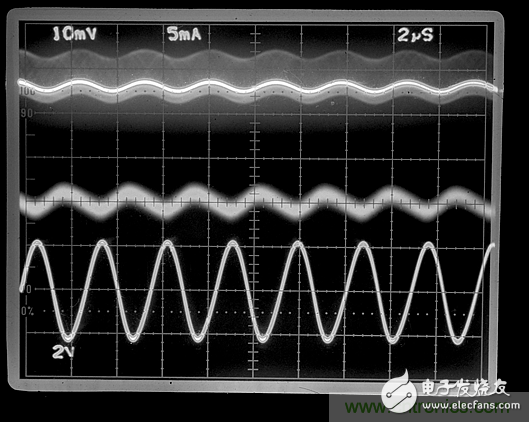

*图8:顶部迹线:+15V电源、Tek P6021电流探头和Tek 7A14(@ 5mA /格),使电源产生脉冲电流,驱动振荡器和500Ω负载,可见。中间迹线:+ 15V电源、Tek P6046差分探头(@10mV/格),显示+15V电源的电压纹波;用电压探头实际看不到电流脉冲。底部迹线:振荡器输出至500Ω负载。振荡器+/- 15V电源连接到150μH电感、10Ω电阻和22μF旁路电容。

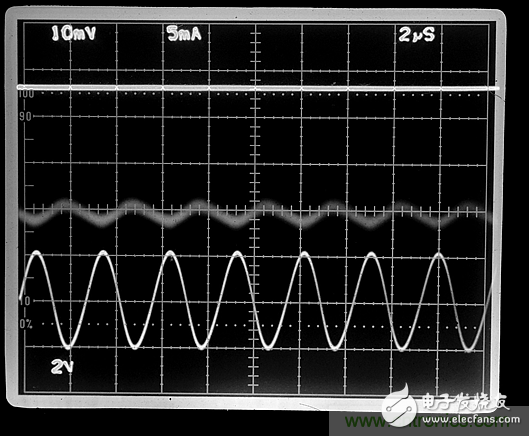

图9:顶部迹线:+15V电源、Tek P6021电流探头和Tek 7A14(@ 5mA /格);驱动振荡器和500Ω负载的脉冲电流由150μH电感、10Ω电阻和22uF旁路电容控制。中间迹线:+15V电源、Tek P6046差分探头(@10mV/格)、在+15V电源上显示电压纹波;有或没有150μH电感和10Ω电阻,看起来差不多。底部迹线:振荡器输出到500Ω负载。

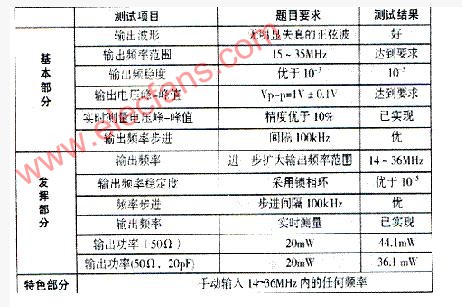

JFET电压调谐文氏电桥振荡器的测量规范:

频率范围:250kHz至1MHz。

调谐灵敏度:110kHz/V

谐波:最大-30dBc。

输出电平:1VRMS、+/- 0.3dB馈送至150Ω负载。

该JFET电压调谐文氏电桥振荡器说明如何进行设计权衡来实现可工作的振荡器。调谐频率范围受限于匹配的P沟道JFET对的线性调谐范围。将频率调谐范围扩大到本范例之外会导致文氏网络的有效电阻值过度失配,使文氏网络失衡。考虑到JFET 文氏网络的这些限制,调谐灵敏度最终会达到110kHz/V左右。对于1MHz中心频率、30kHz步进来说,该VCO的阶跃响应或调谐速率被幅度控制环路限制为1ms。在1MHz、振荡器输出负载为500Ω的情况下,谐波比最差情况下的基本调谐频率(-dBc)低-30dB。这是由文氏电桥失配、放大器性能、振荡器输出电平驱动500Ω负载等情况决定的。这种FET调谐的VCO的电性能与使用变容二极管的LC电压调谐振荡器类似。

文氏网络是桥网络的实例,它是模拟电子学的基本构建模块之一。桥网络演变而来的还包括由四个电阻组成的惠斯登电桥,然后是进一步的差分放大器。最基本的差分放大器是由两个负载电阻和两个有源器件(FET、MOSFET、双极型晶体管、真空管、微型抗震电子管等)组成。利用四元网络在两边实现平衡和对称,这是一个非常有效的设计理念。这种平衡和对称的概念体现在模拟电路设计的许多方面,类似于自然系统之于人类行为。

幅度控制系统环路是平衡的另一种演变。它包括一个参考,该参考与幅度值进行比较。比较结果产生一个差值或误差信号,使用增益控制元件改变放大器增益就可以控制文氏电桥振荡器的输出电平。实施放大器增益校正(校正事件时间)和决定需要施加多少幅度校正,增加了幅度控制环的复杂性。如果不以适当的时序和量值进行校正,控制系统会变得不稳定。

JFET文氏电桥振荡器的设计和构建也使旁路电容一些“隐藏”的影响显露出来。旁路电容可以是有效的瞬时储能器件,也可以成为电压-电流转换器。电流探头有助于说明旁路电容对电流转换的影响。由于旁路电容会产生有效低阻抗电压源,因此使用电压探头不易揭示此现象。

图10:电流探头有助于说明旁路电容对电流转换的影响。

增加电感作为附加的瞬时能量存储元件(阻抗随频率的增加而增加),降低了通过电源“逃离”该电路的高频。与电感串联的电阻防止该网络变成谐振回路。

电子发烧友App

电子发烧友App

评论