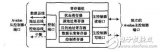

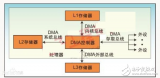

主控制板的硬件系统结构

图3-3硬件结构框图

大型LED显示系统的主控制板应该能够完成以下功能:

(1)接收PC端发送来要求显示的点阵码以及显示模式并且存储。

(2)根据显示模式对原始点阵码进行排序,以符合DMA的传输数据要求。

(3)将排序好的点阵码映射到LED显示屏相应显示位置的列数据锁存器并且控制行驱动循环扫描显示。

根据系统要求,以及未来扩展需求,系统结构框图如图3.3所示。本系统设计采用核心板和接口板分开设计的方式,增强了系统应用的灵活性和可扩展性。其中图中虚线框内为核心板,虚线框外为到LED显示屏的接口板。核心板完成任务(1)、(2)、(3)。接口板完成逻辑电平转换、译码、锁存等逻辑功能以配合核心板完成任务(3)并且驱动输出信号。

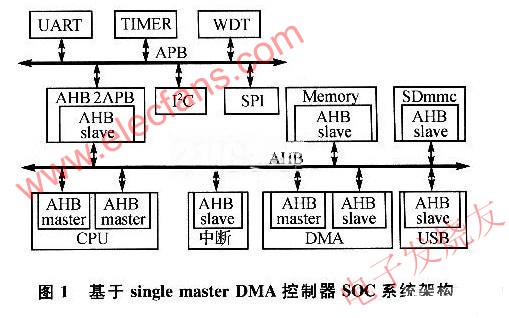

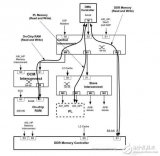

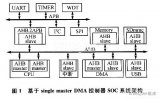

采用并行DMA数据传输可选择MCU加DMA芯片和具有内部DMA控制器的CPU两种方案,从系统结构和成本以及开发复杂度方面考虑,后者更加合理。由于使用硬件DMA并行传输列数据,将LED显示屏上的一系列同行列数据锁存器视为一段连续的存储单元,由于并行数据传输LED显示模块电路结构并不能完全满足16bit并行DMA数据传输的要求,而又为了能使上代的LED显示驱动模板产品仍能使用,列显示数据需要根据显示模块电路结构及并行DMA数据传输方式重新排序,并以重序排列格式存放在指定的显存地址中.当在静态显示模式时,重新排序的数据量并不大,但当动态模式显示时(如上滚显示时),重新排序的列数据以页面的方式存储在显存内,这样将占用大量的存储空间,甚至达到几十M字节.若使用SRAM作显存成本太高,体积太大,使用廉价大容量的SDRAM可以很好的解决该问题,但由于SDRAM的电路特点【2I】,必须在系统中有SDRAM数据刷新控制器。为减小系统成本和系统复杂度,期望找到自带外部存储控制器的微处器。出于上述考虑于是本系统设计选择使用三星公司ARM7TDM【田】内核具有内部DMA控制器和SDRAM存储控制器的S3C44BOX作系统的主控制器;廉价大容量的SDRAM选择使用4Mxl6Bit×4Bank的K4S561632D,它对于512x256(8平方米)的单色屏来说完全满足要求了。

由于S3c44BOx自身不具有非易失性存储器,所以必须外接非易失性存储

器来存放代码及需要保存的点阵码和显示的控制信息。考虑到点阵码和显示控制信息会经常更新,所以非易失性存储器需要能够电重复擦写,由于原始点阵码的数据量可能很大(几百kByte),并考虑到系统的升级选择使用IMxl6Bit的SST39VFl601作系统的代码数据存储器,在本系统应用中SST39VFl601的IM×16Bit存储空间分为代码部分与原始点阵码部分。

3.2.2存储空间配置

图3--4系统存储空间分配图

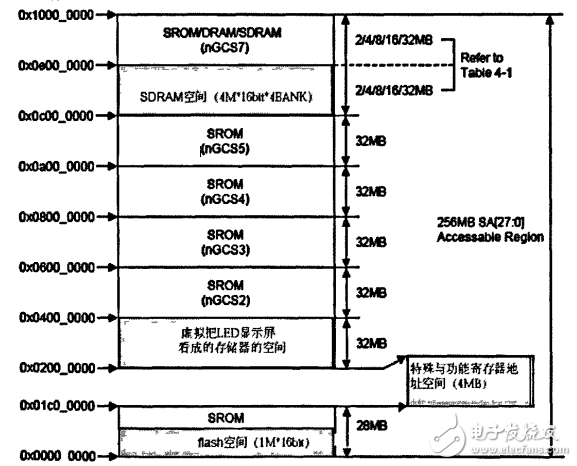

ARM微处理器的理论寻址空间是4GB,采用统一编址的方式,将系统的各类存贮器(如FLASH、SRAM、SDRA~D、外设、特殊功能寄存器都映射到该地址空间[231.为了便于管理,又将地址空间划分为若干小块,每一个小块称为一个存贮器组(MEMORYBANK),通常由硬件电路提供每一个存储器组的选择信

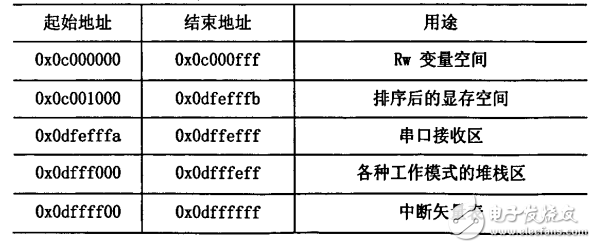

号.S3C44BOX提供一共256MB的地址空间,分为8个组,每组地址空间为32MB,S3CA4BOX的[nG-CSo~nGCS7l弓l脚就g分别选通这八组地址空间的选通信号引脚田】。本系统设计存储空间分配图如图3.4所示.

主控板的存储空间映射如表3.1所示:

表3-l存储空间分配表

LED显示屏所占的存储空间由LED的横向级联屏数决定,如对于512“256的屏体,横向级联数是8,存储空间为:16*8*16bit共256Byte,可以看出为LED屏留出的地址空间是绰绰有余了.

主控板的FLASH地址范围从0x00000000到0x00200000,共2Mbytes。其空间范围被分为两个区域用途见表3-2.

表3-2FLASH功能空间分配表

主控板的SDRAM地址范围从0xoc000000到0xodffi珊空间分配与用途如表3.3所示。

表3-3SDRAM功能空间分配表

3.3硬件电路的详细设计

3.3.1S3C44BOX简介

32位RISC处理器S3C44BOX采用ARM7TDMI内核,提供全面的、通用的片上外设,大大减小了系统电路中除处理器以外的元器件配置,从而最小化系统成本,本系统关注的特性如下:

(1)2.5VRISC体系结构和ARM7TDMI内核处理器强大指令系统,支持Thumb代码,提高代码密度;支持JTAG片上集成ICE解决方案。

(2)支持大/小端方式;支持8个存储器BANK。其中7个具有固定的BANK起始地址和可编程大小,1个具有可编程BANK起始地址和BANK大小;

其中6个支持ROM/SRAM访问BANK,2个RohⅣS融呦RAM访问

BANK;所有的存储器BANK具有可编程的访问操作周期。

(3)内部集成可编程选择使用的8KB高速缓存cache,未用的cache可用作0/4/8kByte的SRAM空间。采用保持主存储器与cache内容一致性的“写穿式”策略。

(4)片内的锁相环使MCU工作时钟最大达75MHz

(5)30个中断源,采用向量化的IRQ中断模式以减少中断的延迟,并支持

FIQ为紧急的中断请求进行服务。

(6)2通道通用DMA控制器,2通道接口DMA控制器,不需要CPU干预,支持存储器到存储器,存储器到10,Io到存储器,Io到IO的DMA数据传输。并支持ontheny模式。

S3C44BOX还有很多其他的应用资源,在此不赘述。在本系统设计中仅使用了l通道通用DMA控制器,1通道的串口UART。内部的看门狗定时器及内部的8KSRAM,以及PC,PG口,在总线选择上使用16bit总线,并使系统工作在小端工作模式。

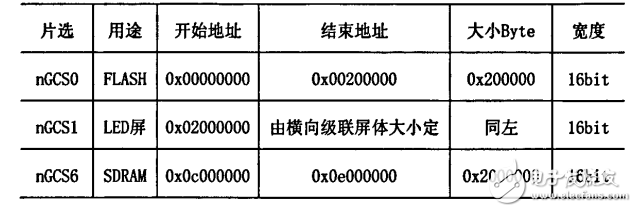

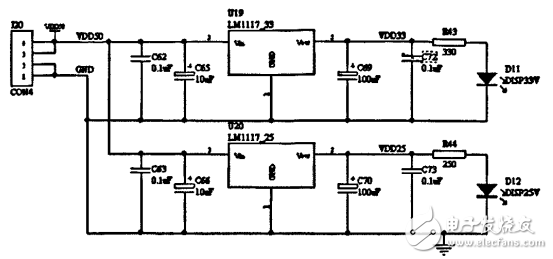

3.3.2电源电路

电源电路设计主要的考虑因素有:电源的种类、上电次序、数字,模拟混合电源处理方法、空间、输入电压、输出电压、输出电流等,在本系统主控板中需要使用5V、3.3V、2.5V稳压数字直流电源。其中CPU分别需要3.3V和2.5V分别给片上Io口和CPU内核供电,而LED显示屏接口电路部分需要5V电源

供电。需要注意的是:CPU内核和Io口应按照内核先于IO口上电,后于Io口掉电的规则,但尽可能同时供电,二者的时差不能太长,否则可能毁坏芯片刚。为简化电源电路设计,使用5V直流开关电源输入,通过3.3V和2.5V的线性稳压电源芯片[251得到3.3v和2.5V的直流稳压电源。电路如图3.5所示.

图3-5电源电路原理图

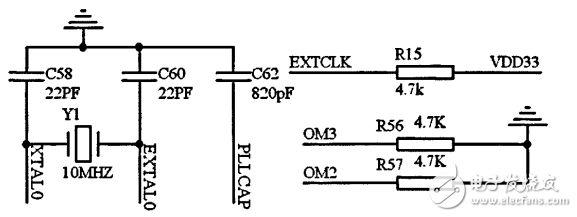

3.3.3晶振复位电路

由于本系统中串口使用9600波特率,使用的系统时钟最好是9600的整数倍,故选用3.6864MHz的晶振并配置S3C44BOX内部的PLL六倍频后得到22.1184MHz的系统时钟,S3C44BOX内部的PLL电路兼有倍频和信号放大功能.为节省控制板成本,使用无源晶振,需要注意的是:

(1)上电后时钟源的选用取决OM[3:21弓1脚的逻辑电平状态,如表3-4所示。

(2)3C44BOX的PLLCAP引脚需要接一个680pF的补偿电容。

(3)S3C44BOX的EXTCLK引脚需要通过4.7ko的限流电阻接3.3v的高电平,表明不使用EXTCLK引脚提供时钟[20-1,电路如图3-6所示.

图3-6晶振电路原理图

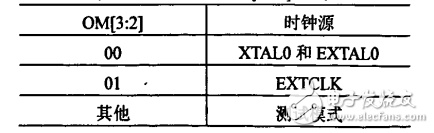

表3-4时钟源选择OM[3:2]配置表

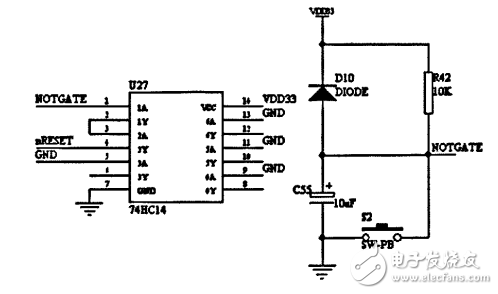

图3.7所示的是一个简单实用的上电复位电路。在系统中,复位电路主要完成系统的上电复位和系统在运行时用户强制按键复位功能。复位电路由简单的Rc电路构成,经使用证明,其复位逻辑是可靠的。

图3-7复位电路原理图

该复位电路的工作原理如下:在系统上电时,通过电阻R42向电容C55充电,当C55两端的电压未达到高电平的门限电压时,NOTGATE端输出为低电平,系统处于复位状态;当C55两端的电压达到高电平的门限电压时,NOTGATE端输出为高电平,系统进入正常工作状态。当用户按下按钮S2时,C55两端的电荷通过D10和R42被泄放掉,NOTGATE端输出为低电平,系统进入复位状态,再重复以上的充电过程,系统进入正常工作状态。NOTGATE通过两级非门电路用于按钮去抖动和波形整形;通过调整R42和C55的参数,可调整复位状态的时间,值得注意的是要使上电后S3C44BOX的nRESET要持续4个时钟的低电平,即当系统时钟为22.1184MHz时为200ns。但是,在上电后,系统的晶振往往需要100ms~200ms的时间稳定脚l所以上电后C55正极应保持足够长的低电平的时间。复位时间主要由R和C确定,C55正极电压矿=3.30一e-t/7),f=RC。设0.8V为低电平的上限,选R42为100kQ,C55为10uF,可得t*277ms,从而满足复位要求。

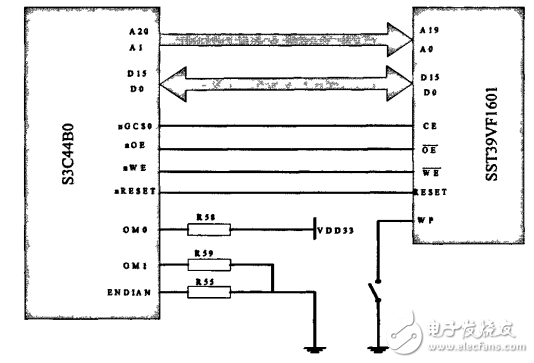

3.3.4FLASH接口电路

系统的代码与从上位机接受到的原始点阵码以及显示控制信息数据存放在CPU外的FLASH芯片中,当S3C44BOX上电复位后,它立即从0x00000000地址处取指并开始执行,并把定位在地址0x00000000处的存储器称为BOOTROM。因此系统的启动代码应放置在0x00000000处,ARM系统中通常使用能够快速读取、因此方便写入的FLASH作为代码和常量存储器。刚上电时CPU对FLASH的接口不需要任何软件上的配置,因为S3CA4BOX内部的存储器访问控制寄存器默认的控制时序足够慢,可以读出任何速度的ROM芯片数据,但为了充分发挥FLASH芯片的性能,应在初始化中配置相应存储器的访问时序四l。值得注意的是要使CPU能正常地对FLASH进行操作,需要注意两个硬件设置:3cY4,端和BANK0的总线宽度冈.ARM体系结构可以用两种方式来存储字(这里的字是32bit即4Byte),称为大端格式和小端格式.S3C44BOX的ENDIAN引脚的输入电平的逻辑来确定数据类型是大端还是小端【3ll。0为小端,l为大端。在本系统中使用小端方式,所以ENDLAN应该接一下拉电阻后接地,连接示意图如图3.7所示.

图3-8S3C44BOX与FLASH连接示意图

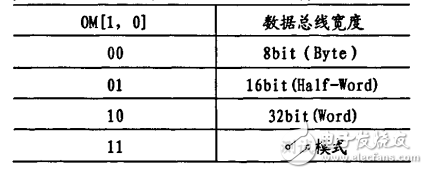

BOOTROM在地址上位于ARM处理器的BANK0区,它可能具有具有多种数据总线宽度,这个宽度是可以通过硬件设定的,即通过S3C44BOX上OM[1,O】引脚上的逻辑电平设定,如表3-5所示.

表3.5BOOTROM在BANK0的数据总线宽度设定

本系统采用一片SST39VFl601(1Mxl6bit)作为代码和数据存储器就能够满足系统要求了,所以本系统使用16bit外部总线。因此OM[1,o]-脚应该设为Ol,并且初始化程序中将BWSCON寄存器中的DWO设为01。本系统采用TSOP封装的SST39VFl601。应注意的是SST39VFl601的WP引脚,当WP接稳定的低电平时扇区O是不能被擦除的1321,只有WP脚接稳定的高电平或浮空时(当该脚浮空时内部电路将其拉高)才能擦除,所以应在该脚处设置一根跳线,下载程序时将其浮空,而在产品运行时使其接低电平。由于S3C44BOX是按照字节编址的,又由于SST39VFl601是16bit为一个存储单元,因此处理器的地址向左偏离一位田l,采用ADDRI与SST39VFl601的A0相连,即:S3C44BOX的ADDR[20:l】对应着FLASH的A[19:o】。由于FLASH的映射在BANK0区域内,SSl”39VFl601的片选与S3C44BOX的NGCS0。

3.3.5SDRAM接口电路

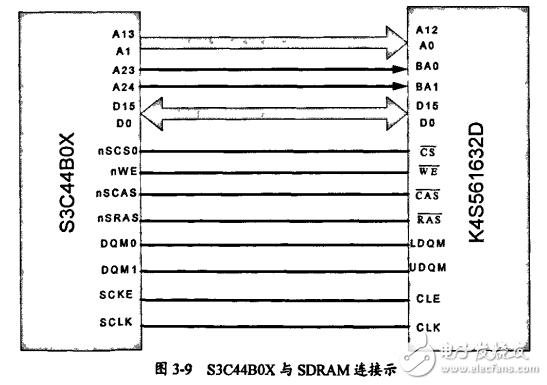

SDRAM是易失性存储器,在调电后数据立即消失,但是其具有存储速度快,容量大成本低的特点,广泛应用于各种嵌入式系统,本系统采用4Mxl6bhx4b£mk,即32MByte的SDR■uM芯片K4S561632D作为系统的R/W段、显存、上位机通信段,中断向量表,堆栈数据的存储器,存储空间的详细配置见第3.2.2节。由于SDRAM的存储单元电路的特点,存储单元可以理解为一个电容,总是倾向于放电,为了避免数据丢失,必须定时充电刷新。S3C4480X芯片本身提供了与DRAM和SDRAM进行直接接口的方案,因为不需要编程外围的逻辑电路来实现SDRAM的刷新时序,只需对S3C44BOX内容相应若干个存储器接口控制寄存器进行适当的配置即可。S3C44BOX与K4S561632D的连接示意图如图3-9所示。

K4S561632D是一款容量为32MB的SDRAM(同步动态随机存储器),所有的输入与输出信号与CPU的前端总线的系统时钟相同,所以S3C4480X为其提供同步时钟脚SCLK,该脚与K4S561632D的CLK脚相连。

K4S561632D的存储空间组织方式是:4M×16bit×4bank,是多bank结构口‘1.前面提到过DRAM的存储单元电路特点相一个电容,在读取数据前需要进行预充电,采用多bank结构可以在一个bank进行预先充电时间对另外一个bank进行读写操作,这样当进行一行读取后,对已预充电的bank又可以马上读取了,这样就省去了预先充电的时间,大大提高了存储器的访问速度。K4s561632D分为4个bank,它内部对4个bank进行管理。控制各个bank进行预先充电,它上面的BA0,BAI引脚就是用来实现4个bank间的选择。由于K4S561632D的容量为32MB,其BAl与BA2接地址线A24、A23。由于高速数字布线的需要,在PCB布线时,几根重要的信号线端应接20欧阻抗匹配电阻,以保证高速数字信号的畸变不超过要求的范围。

再读取操作时候首先使CKE引脚有效,激活K4S561632D,随后是一个读或者写有效,在激活后的地址用来选择需要的操作的bank和行(BA0、BAI用来选择bank,A0道All用来选择行)。在行地址被读取并延迟一到几个时钟后(潜伏期)地址总线上A0到A8用来选择操作开始的列地址,这样,数据就被读取出来了。

3.3.6主控电路与LED屏的接口电路设计

本显示系统选用基于ARM7TDMI内核并带有内部DMA控制器的S3C44BOX作主控制器,使其工作在ARM状态,为了加快传输数据的速度,提高传输数据的效率,本系统的设计思想是:

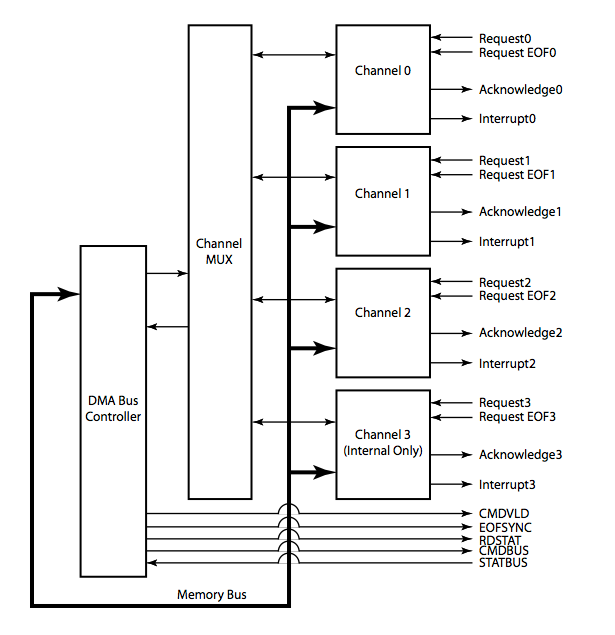

(1)将LED显示屏虚拟的视为一段连续的存储空问【3习.C2)使用S3C44BOX内部的DMA控制器实现数据的准确传输,在传输过程中CPU不参与,实现在连续的读写操作时就完成一段数据的传输。

(3)使用并行技术,主控板到LED屏的数据总线宽为16bit,同时对纵向级联的两个显示模式传输数据。

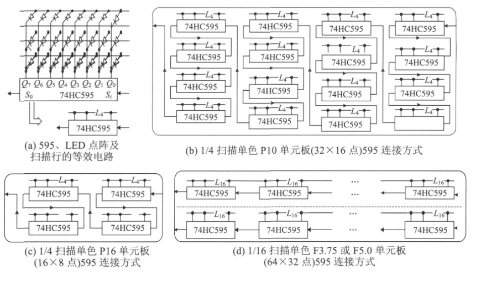

在第2.2.4节中已说明了将LED显示屏视为一段连续的存储空间是可能的,它是使用DMA控制器在连续的读写操作完成一段数据传输的基础。由第2.2.4节可知,并行数据传输显示模板上的译码电路与错位级联思想可使每个显示模板及显示模板上的各个列数据锁存器准确选通,如图2-6所示,横向级联的显示模板可看成一段连续的存储单元,所以对显示驱动板传输列数据实际上就是对存储单元的写操作.这样就可以利用CPU写存储器的控制线、数据总线、地址总线上出现的信号作传输列数据到显示驱动板第一级列数据锁存器锁存的控制信号。第一级列数据锁存器的选通译码器的译码信号可以利用微控制器的地址线,由于LED显示屏一个显示驱动模块上共有16对锁存器,所以需要4根低位地址线作第一级列数据锁存的译码信号,而横向级联可最多级联8块显示驱动模块,所以需要三根地址高位地址线,但为了以后扩展需要预留一根高位地址线共8根地址线。列数据由数据总线传送。

由第2.2.4节可知,并行数据传输的LED显示模板上的数据总线宽度是8bit的,而主控板到LED显示屏的数据总线宽度是16bit,所以主控板对LED显示屏的一次写操作实际上是同时对纵向级联的两个显示模板的同名行同名列传输了数据,这样提高了数据传输的速度和效率。但是这样使用16bit宽度的并行DMA传输技术需要软件先将原始的点阵码按要求进行排序,排序算法仅需在接收到新的显示内容后或重新上电后运行一次,这样对于异步显示系统是可以接受的。算法将在第3.4.4节详细讨论,在此我们假设显存中的数据都是按要求完成排序的,可以直接进行DMA传输。

图3-10主控板与LED屏接口电路原理图

所以主控电路与LED显示屏接口电路应能实现一下功能:

(1)选通任意位置的显示模块及该模块上的第一级列数据锁存器。将该位置要显示的点阵码准确锁存,并能控制在第一级列数据锁存器数据刷新后将刷新数据锁存到第二级列数据锁存器并输出。

(2)能控制选通驱动16行同名行中一行进行逐行扫描显示.

(3)实现主控芯片3.3v到LED屏5V的逻辑电平转换136】。主控板与LED屏接口电路原理图示意图如图3·10所示。对于一个大型LED屏其结构可分为纵向级联和横向级联,这种结构类似于一个三维数组.们假设一个三维数组LED[i][j]啕,其中;

i=0,l‘2…,m表示LED屏纵向级联级的序号。

j=O,1’2…,n表示LED屏横向级联级的序号。

k=0,l,2…,15表示显示模块上16个第一级列数据锁存器的序号.

由于系统使用16bit并行总线数据传输方式,并将LED屏视为一段连续的存储单元,故使用A【4:l】显示模块上选通第一级列数据锁存器译码器(图2.5U2)的译码输入,即为三位数组的k变量;使用A【8:5】作选通横向级联显示模块的译码器(图3-9U7-U15)译码输入,即为三位数组的j变量;由于LED屏要求具有良好的灵活性,又由于采用DMA传输数据要求点阵码存放顺序的技术要求,纵向级联级选通不满足使用地址总线译码选通的条件,所以使用S3C44BOX的PG[2:0]作纵向级联级选通译码器的译码输入,即三位数组的i变量。

由于地址和数据总线上的状态不断变化,所以在对LED屏进行写操作时地

址和数据信号应进行锁存,主控板上分别使用图3-9中U2、U3和U4锁存对LED写操作时的地址、数据总线上的状态.LED屏分配首址0x2000000,当对其进行写操作时,S3C44BOX的nGCSl和nWE脚会出现可编程控制时延的有效低电平。使nGCSl经一个非门作U2、U3和U4的锁存使能控制信号,保证仅在对LED屏访问时地址、数据总线上的信号才被锁存;使nWE经一个非门作屏端第一级列数据锁存器(图2.5U3-U19)的锁存使能控制信号,保证只有当刷新数据稳定出现在列数据锁存其输入端时才被锁存;使S3C44BOX的PCI0作所有屏端第二级锁存器(图2-5U20.U35)的锁存使能控制信号线;使用S3C44BOX

的PCI3:0]作16行驱动译码器(图2.5U1)的译码输入。由于数据传输时只需要主控板对LED屏输出控制,不需要信号反馈,所以接口电路采用廉价的5V供电的HCT电路芯片鲫口8l[391]方案,就可满足主控芯片3.3v到LED屏5v的逻辑电平转换。

在DMA传输数据时,我们更关心的是DMA的写操作,时序如图3.1l所示.tl时刻DMA写操作开始,地址和数据总线上出现了咖屏相应位置的地址和刷新数据;t2时刻nGCSl引脚出现有效低电平,地址和数据总线上的数据被锁存到图3-10中U2-U4并输出;t3时刻nwE引脚出现有效低电平,图3.10中U2-U4的输出数据被锁存到屏端第一级列数据锁存器并输出。这样主控制器就完成了一次列数据的刷新。

图3.11DMA的写操作时序图

3.3.7串口电路设计

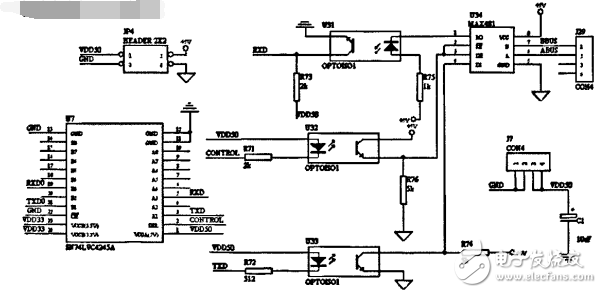

为消弱电气噪声对信号传输的影响,主控板子上位机通信采用完全电器隔离的半双工RS485电路㈣。电源使用变压器隔离,信号线和控制线使用光耦离,电路如图3-12所示。

图3-12485串口电路原理图

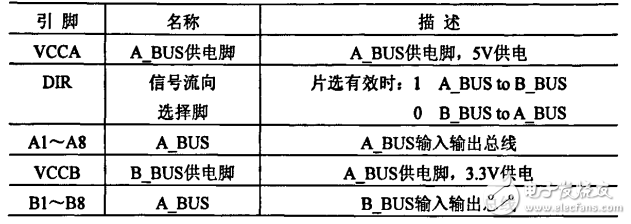

RS485装换芯片采用半双工485转换芯片MAX481t411。由于使用485转换电路使用5v供电,而主控芯片S3C44BOX使用3.3V供电,因此存在逻辑电平转换问题.本系统在串口电路中使用能够实现3.3V到5v和5v到3.3V逻辑电平转换芯片SN74LVC4245A,它的引脚说明如表3-6所示。

表3-6SN74LVCA245A的引脚描述

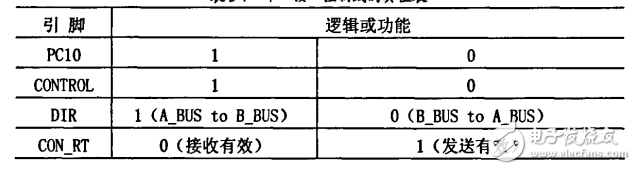

本设计使用S3C44BOX的10口PCIO作串口收发控制的控制线,但存在逻辑电平转换的问题,PCI0首先通过74HCT244输出得到5V逻辑电平信号线CONTROL,由它做串口收发控制的控制线和SN74LVC4245A的数据流向控制线。CONTROL控制线经光耦隔离成为CONRT控制线控制信号真值表如表3.7所示.

表3-7串口接口控制线的真值表

由真值表可知,S3C44BOX端3.3V逻辑电平的串口引脚RXD0应TXD0应连接在SN74LVCA245A的B总线上;485串口电路5V逻辑电平的引脚RXD和TXD应连接在SN74IⅣC4245A的A总线上。

电子发烧友App

电子发烧友App

评论