您的位置:电子发烧友网 > 电子技术应用 > 嵌入式技术 > FPGA/ASIC技术 >

龙芯处理器IP核的FPGA验证平台设计(2)

2012年04月21日 15:22 来源:本站整理 作者:秩名 我要评论(0)

图4布局布线的输入输出与调用关系

2.2验证平台的系统设计

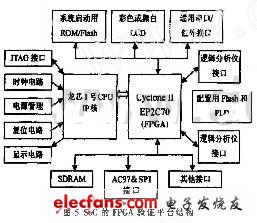

本验证平台FPGA采用Altera公司的Cyclone ⅡEP2C70,该器件采用了TSMC领先的90 nm低电介工艺技术生产⒊支持4个可编程锁相环(PLL),提供灵活的时钟管理和频率合成能力;包含了150个18×18 bit乘法器,可以完成基本的DSP处理;高速外接存储器接口支持SRAM、DRAM\DDR、DDR2以及QDRII SItAM;支持差分和单端I/0标准,包括接收速率805 Mbis和发送速率640 Mb/s的LVDS、mlnl LVDS、LVPECL、 差分HSTL和差分SSTL及处理器、ASSP和ASIC接口的64位66 MHzPCI和PCI-X;高达260 MHz工作频率,真正的双端口工作(1个读和1个写,2个读或2个写);与133 MHz Pal_X1.0标准兼容;用户最多可用引脚622个;高达402.5 MHz性能的分层时钟网络,多达16个全局时钟线,快速串行配置时间小于100 ms;支持3.3 V、2,5 V或1.8 V多种电压,可用于视频、图像处理(如MPEG4编码和译码、视频滤波)和无线基础设各中。基于龙芯I号CPU IP核的SoC的验证平台结构如图5所示。

图5 SoC的FPGA验证平台结构

图5中,外围电路的主要功能是验证SoC中各个接口IP模块能否与龙芯I号IP核、外部接口单元、硬件驱动软件和实时操作系统协调高效地工作。由于接口(如USB接口、UART/IrDA接口、SPI和LCD接口等)电路结构比较简单,且很多资料都有介绍,在设计时,除了注意通用的设计规则和印匍电路板(PCB)布局布线外,没有特别的要求。同时,为了便于分析各个被验证的IP模块在任意时刻的状态,将Cyclone Ⅱ EP2C70的大多数I/0引脚都引出到PCB上,以方便SoC开发人员使用逻辑分析仪进行信号实时采集和分析,也可让信号发生器产生一些特定信号以供系统调试使用。该开发系统在设计PCB时还特别注意了电磁干扰的屏蔽问题。

2.3 SoC到FPGA的系统移植

使用Altera公司的FPGA开发工具Quartusll,将SoC向Cyclone Π EP2C70(FPGA)移植的步骤如下

(1)对SoC进行修改,以适合FPGA的开发环境。修改子模块配置、RAM、FIFO等,添加PLL对所需要的时钟进行适当的分/倍频,或提高时钟信号的质量。

(2)使用Quartusll内置综合工具或专用综合工具(如常见的Synplify._pro)单独建Project,对RTL进行综合,生成网表。时钟工作频率较高的,要写综合约束条件。

(3)指定每一个输人输出信号对应的FPGA管脚和输人输出逻辑类型。

(4)编译生成的网表以生成sof文件,包括优化、适配、sof文件生成等分步骤。

(5)进行静态时序分析,检查是否满足预定的时钟频率要求,若不能满足,则重新进行第(2)步。如果多次进行步骤(2)仍不能满足时序要求,则需要根据关键路径对RTL代码进行修改。

关键路径是指延迟最大的路径,该路径的延迟限制了时钟的最大工作频率。该SoC芯片的最大工作频率在266 MHz以上,与选用的FPGA Cyclone Ⅱ EP2C70的总线时钟速度相当。

3、 VxWorks实时操作系统

本文所设计的SoC硬件平台上,最终将运行Vx-Works操作系统,作为此次嵌入式SoC硬件平台设计的软件需求和最终的验证目标。VxWorks是一个具有可伸缩、可裁减、高可靠性,同时适用于所有流行CPU平台的实时操作系统㈣。可伸缩性指VxWorks提供了超过1 800个应用编程接口(API)供用户自行选择使用;可裁减性指用户可以根据自己的应用需要对VxWorks进行配置,产生具有不同功能集的操作系统映像;可靠性指VxWorks可以提供非常安全的操作系统平台。VxWorks的基本构成组件包括BSP(Board Support Package)、微内核Wind、网络系统、文件系统及I/0系统。本文测试更关注于BSP、Wind以及I/O组件。BSP中包括硬件环境中CPU的初始化及系统各项硬件资源的安装和配置,如RAM、Clock、网络接口、中断控制器等。微内核Wind是Win ̄dRiver公司自行开发的一种嵌人式操作系统内核,该内核具有标准的嵌人式实时操作系统的基本特征。

本文导航

- 第 1 页:龙芯处理器IP核的FPGA验证平台设计(1)

- 第 2 页: FPGA的典型开发流程

- 第 3 页:验证平台的检验

标签: