您的位置:电子发烧友网 > 电子技术应用 > 嵌入式技术 > FPGA/ASIC技术 >

龙芯处理器IP核的FPGA验证平台设计(3)

2012年04月21日 15:22 来源:本站整理 作者:秩名 我要评论(0)

将已经成熟的AMBA总线IP核的Verilog代码通过Synplify综合,利用Altera公司的QUARTUS Ⅱ软件作布局布线,烧人Cyclone Ⅱ EP2C70,再用同样的方式将新开发的EMI IP核的Verilog代码烧入该FPGA,将其中的SDRAM控制器作为验证示例,选取其中最简单的访问方式来验证该平台能否使用。上电后,首先要对所有内存区(bank)预充电,经8个自刷新周期后需要设置访问模式,即编程模式寄存器。以上三个过程要求如下:

(1)预充电命令的发出要求:在时钟周期的上升沿处,CS、RAS、WE为低,CAS为高。

(2)自刷新命令的发出要求:在时钟周期的上升沿处,CS、RAS、CAS 禾口CKE保持低,WE为高。

(3)模式寄存器的激活:在时钟的上升沿处,RAS、CAS、CS和WE为低。

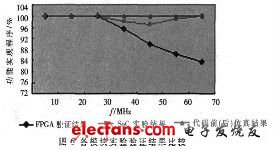

当要验证各个IP模块(包括[NT中断控制器、DMA控制器、LCD控制器和AC97控制器等)之间的协同工作时,烧入的代码较多,占用的FPGA资源也较多,再加上需要实时运行,例如播放PM3实时解码过程中,时钟至少要求60 MHz,需要工作的IP核有总线、DMA控制器、INT中断控制器、AC97控制器等,因此在这种情况下,最好使用Multi PointSynthesis的综合流程和Timing driv-en的综合与优化策略,并使用Logic一lock约束技术和人工干预布局布线,以达到预期目的。使用该平台对所开发的SoC的各个模块进行了验证,并在lO MHz~70 MHz条件下与代码前(后)仿真结果和SoC实测结果进行了比较,发现该FPGA验证平台在多模块、高速情况下,性能有所下降,如图6所示,需进一步提高综合和布局布线技术。

图6各模块实验验证结果比较

本文设计了基于国产龙芯I号处理器IP核的SoC的FPGA验证平台,介绍了怎样利用该平台进行软硬件协同设计、SoC系统移植、IP核验证和运行实时操作系统。在电压设计、模块选用甚至处理器核的选用方面都考虑了升级扩展技术,可为其他SoC的验证所借鉴。验证结果表明,基于龙芯I号CPU IP核的SoC可成功运行Linux嵌入式程序及VxWorks。

本文导航

- 第 1 页:龙芯处理器IP核的FPGA验证平台设计(1)

- 第 2 页: FPGA的典型开发流程

- 第 3 页:验证平台的检验

标签: