数字滤波部分 - 多软件平台FIR数字滤波器的协同设计

2012年11月13日 14:53 来源:本站整理 作者:灰色天空 我要评论(0)

2.2.1 FIR数字滤波器的设计原理分析

FIR数字滤波器的构成形式主要有直接型、级联型、线性相位型FIR滤波器和频率采样型等。本文采用直接型结构,故N阶FIR数字滤波器的传递函数为:

H(z)是z-1的N-1次多项式,它在z平面上有个N-1零点,在原点z=0处有一个N-1重极点,因此系统函数H(z)永远稳定。系统差分方程表达式为:

上式就是输入序列x(n)与单位冲击响应h(n)的线性卷积,由上式可知n时刻的输入y(n)仅于n时刻的输入以及过去N-1个输入值有关,实际上FIR数字滤波器是由一个"抽头延迟线"加法器和乘法器的集合构成的。赋给每个乘法器的操作数就是一个FIR系数。

线性相位型FIR数字滤波器相位响应是频率的线性函数,即:

该因果系统具有严格的线性相位,当M为偶数时,有:

其中M为FIR滤波器的抽头数;h(k)为第k级抽头系数(单位冲击响应);x(n-k)为延时k个抽头的输入信号。

2.2.2 滤波器系数的计算

数字滤波器实际上是一个采用有限精度算法实现的线性非时变系统,它的步骤为先根据需要确定滤波器的性能指标,然后利用Matlah提供的滤波器设计工具--FDAtool仿真设计滤波器进行系数的设计。本系统的设计指标:设计一个8阶低通滤波器,模拟信号的采样频率为50 kHz,信号的截止频率为2000Hz,输入序列带宽为8位。因为在FIR数字滤波器之后的ispPAC20中的D/A转换器为8位,所以在设置滤波器系数的时候要限制输出位数。

FDATool计算出的值是一个有符号小数,而在DSPBuilder下建立的FIR滤波器模型需要一个整数作为滤波器系数。所以必须进行量化,并对得到的系数进行归一化处理。

2.2.3 FIR数字滤波器模型的搭建

DSP Builder是一个系统级(或算法级)设计工具,它构架在多个软件工具之上,并把系统级和RTL级两个设计领域的设计工具连接起来,最大程度地发挥了两种工具的优势。

根据FIR数字滤波器的原理,在Matlab/simulink中进行设计的输入,利用Altera DSP Builder中的模块进行滤波器模型的搭建,然后将计算好的FIR数字滤波器系数输入到搭建的模型中,图4所示为搭建好的FIR数字滤波器模型。

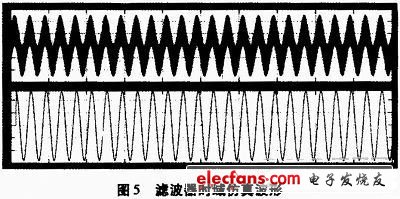

在搭建好的模型中加入两个正弦波合成的输入信号,运行仿真,通过Scope窗口观察滤波器时域仿真波形如图5所示。

从仿真的结果看,FIR滤波器输入信号上面叠加的带外信号得到有效滤除,效果为理想。

但是由于EDA工具软件(诸如QuartusⅡ和ModelSim)不能直接处理MATLab的。mdl文件,这就需要一个转换过。mdl)转化成通用的硬件描述语言--VHDL文件。转化后获得的HDL文件是基于RTL级的,即可综合的VHDL描述。然后对VHDL的RTL代码和仿真文件进行综合、编译适配及仿真。

2.3 后端模拟部分

信号经过FIR数字滤波以后,生成的数字信号经过ispPAC20内部D/A转换器,将数字信号转换成模拟信号,然后通过ispPAC20内部器件进行最后的模拟滤波,滤除信号中的叠加的某些高频分量,经过实际验证,得到的信号能够满足设计要求。

2.4 系统整体功能的实现

将原始信号经过ispPAC20的IN1口输入,经过内部程序的缓冲以及预滤波作用之后,将信号输入到比较器ep1的比较端口,然后与8位逐次逼近寄存器(SAR)输出的数字量经过内部D/A转换器输出的信号进行比较,从而完成从模拟信号到数字信号的转换过程。经过FPGA对转换后的数字信号的滤波处理之后,从FPGA的管脚输出,再通过后端ispPAC20的D/A转换器以及内部的运放以及输出滤波等程序,将信号从ispPAC 20输出,从而完成系统的整个功能。

3 结束语

本系统改变了传统的只用硬件电路设计的方法,系统中前端模拟部分和后端模拟部分均采用可编程模拟器件(ispPAC)实现,使用高度集成化芯片,系统的可靠性与稳定性有所提高,而且利用FPGA可以根据自己的要求重复配置各种精度和特性的FIR滤波器,使设计更为灵活,但由于利用ispPAC20和FPGA构建的A/D转换器在转换精度和速率上有一定的限制,所以此系统在实际工程应用中还存在一定的局限性。

本文导航

- 第 1 页:多软件平台FIR数字滤波器的协同设计

- 第 2 页: 数字滤波部分

上周热点文章排行榜

上周资料下载排行榜

创新实用技术专题

大家谈:华为能否撬开美国市场?

热评

- LM3S9B96开发板手册及原理图

- NI推出Single-Board RIO嵌入式介面

- STM32F103ZET6红牛电路图

- 高通发布全新设计DragonBoard板

- 3.15投诉:揭开天翼3G手机的“欺骗”

- 小米手机2工程机月底将上市

- protel99se正式汉化版免费下载

- 新款 Apple TV 将在3月8日出货

- matlab 7.0软件下载(免费破解版)

- hi3515海思原版原理图

博文

- 新学习单片机,决心转型技术宅

- 白岩松:青春该怎么过?不计后果的过

- 关于学电子的女生那点事

- 当你累了,准备放弃时,看看这个吧!!!

- 元芳,你怎么看cheer番茄

- 晒一晒“我的电子工程师之路”博文大赛【金奖】

- 模电基础知识经典200问(上)

- 模电基础知识经典200问(下)

- 大学那点事儿第二波:文科女生PK理科女生

- 菜鸟STM32初次制版

用户评论

查看全部 条评论

查看全部 条评论>>