在这个半导体制程工艺即将面临更新换代之际,我们不妨从设计、制造和代工不同角度审视一下,迎接全新工艺的半导体企业的应对策略。

新工艺新优势

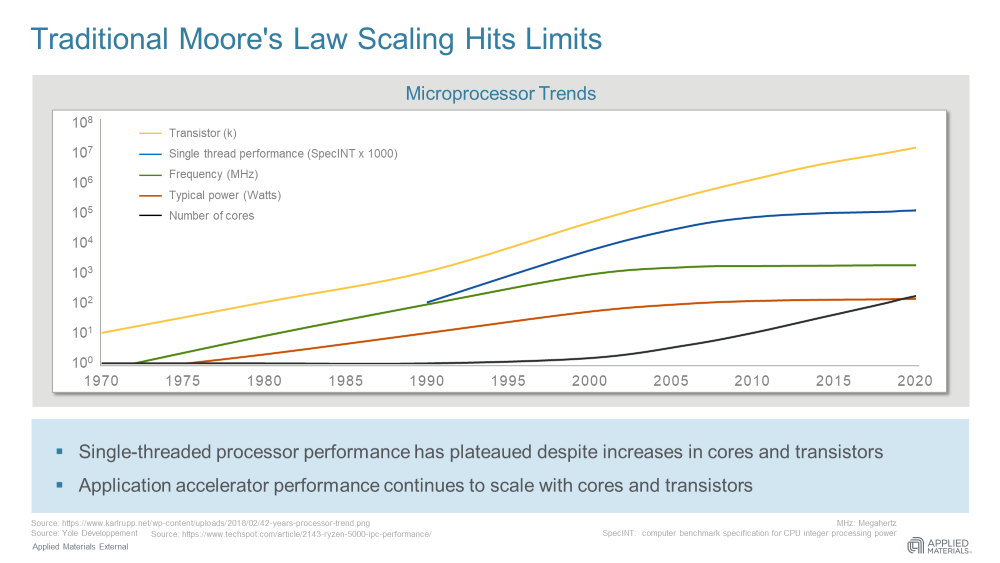

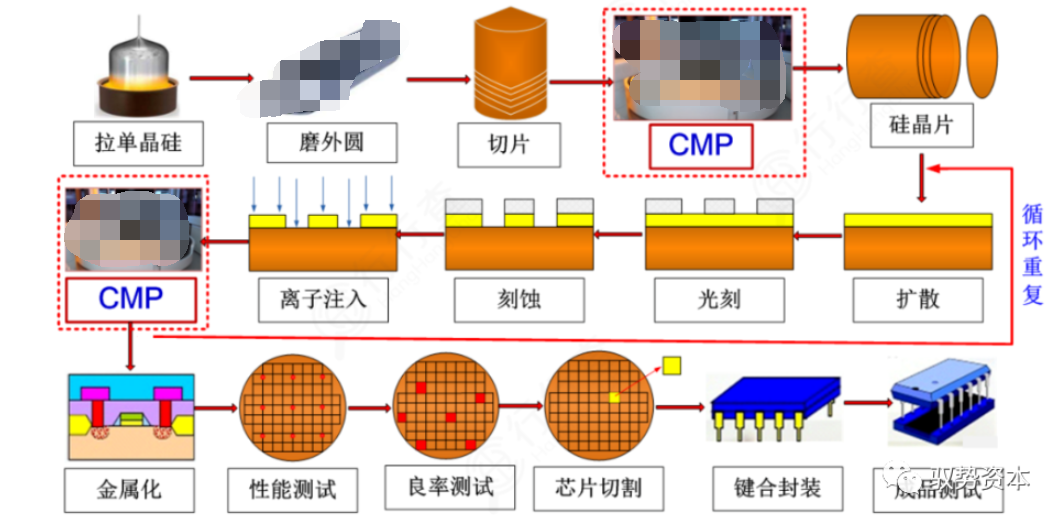

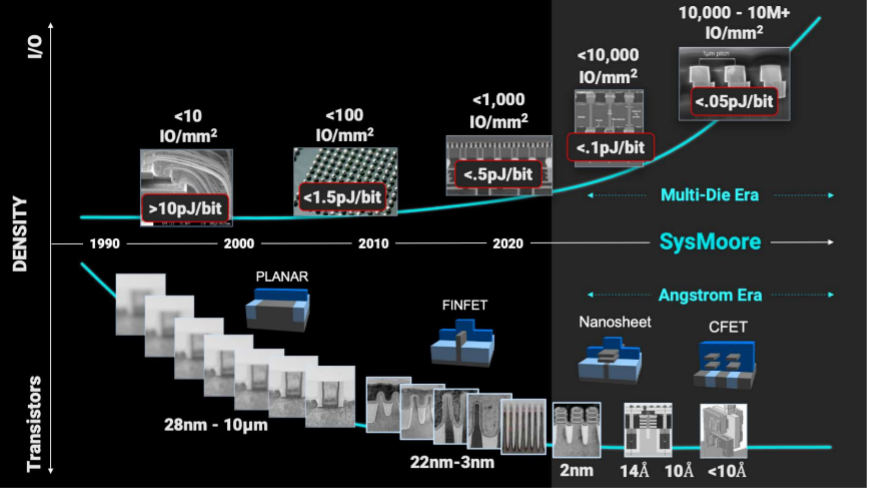

新制程一直是半导体工业发展的标尺,而为产品带来全新竞争力则是企业倾注心血钻研新技术最大的驱动力。每一代的工艺进步给半导体产品带来的性能和功耗提升是明显的。高效能、低耗电及更微小尺寸是半导体技术的三大发展趋势,随着便携电子产品成为市场主流,几乎所有集成电路的尺寸均朝更微小化发展。在同样尺寸的硅片上,新制程让制造商能够增加更多的功能,提高芯片的运行速度,或者降低功能成本。采用28nm先进技术所带来的主要好处是能满足客户对高效能、低耗电、微小化的市场需求。

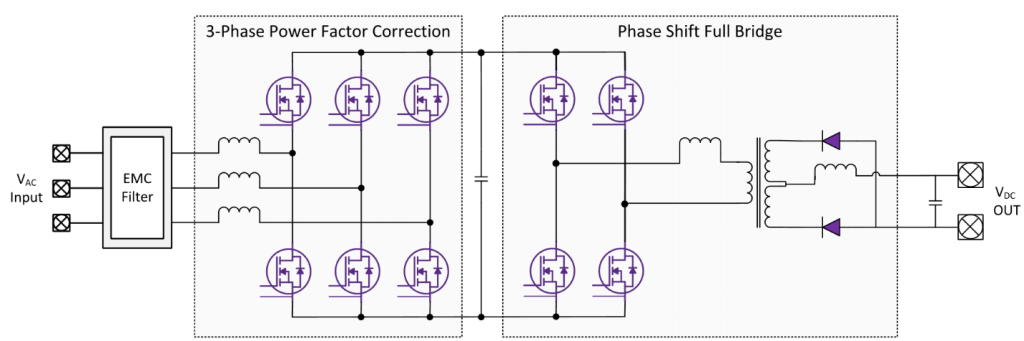

作为除了Intel之外唯一坚持工艺研发的通用芯片IDM,意法半导体高级执行副总裁兼首席技术官Jean-Marc Chery谈及制程进步表示,在消费电子市场上,机顶盒芯片(解码器)、网关和3D(HD)TV是制程从 40 nm技术节点向32/28 nm节点升级的受益者,这些新制程可把芯片的处理性能提高30%左右,而功耗没有任何增加。此外,更小的特征尺寸让制造商能够在每颗芯片上集成更多的处理单元,从而提高计算能力和处理性能,例如,给用户带来出色的高清3D TV体验。在网络系统芯片方面,消费者将获得数据速率达到14-25G bit/s的产品,数据传输速率比上一代技术节点的10-14G bit/s高出许多。

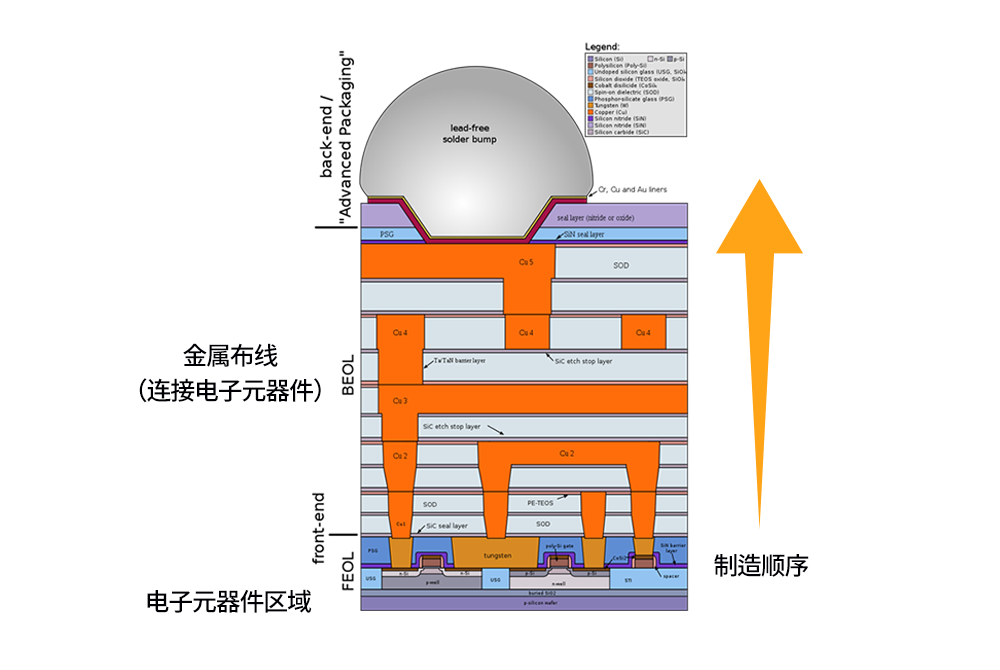

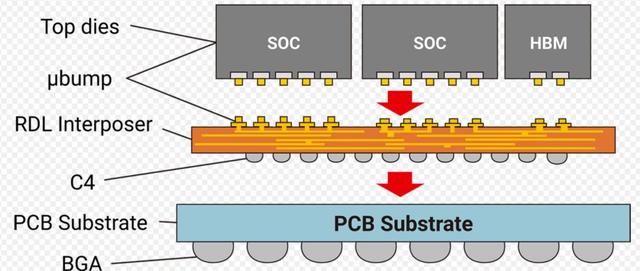

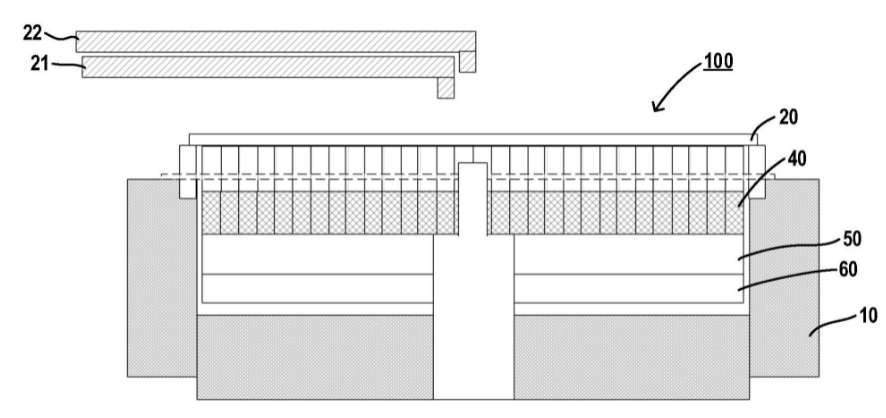

关于新工艺带来的优势,TSMC中国区总经理陈家湘介绍,28HP制程最先采用先进的高介电层/金属闸(HKMG)技术,相较于40nm制程,此项制程在相同漏电基础上速度增快约25%,而在相同速度基础上漏电亦可降低约50%。目前28nm制程区分为Gate-First(栅极最先)以及Gate-Last(栅极最后)二种方式。由于Gate-Last技术具有同时兼顾P-type及N-type晶体管临界电压(Vt)调整的最佳优势,TSMC已宣布在高效能及低耗电制程,为客户采用Gate-Last技术。另一方面,TSMC在业界的领导地位奠基于“先进技术、卓越制造、客户伙伴关系”三位一体的差异化竞争优势。2010年,TSMC已为客户的28nm可编程逻辑门阵列(FPGA)提供了先进的硅穿孔(Through Silicon Via)以及硅中介层(Silicon Interposer)的芯片验证(prototyping) 服务。藉由自身研发的硅穿孔通道(TSV)及与集成电路制造服务业者兼容的晶圆级封装技术,TSMC承诺与客户紧密合作开发符合成本效益的三维集成电路系统整合方案。

赛灵思的全新FPGA就是基于TSV技术的28nm新产品,该公司亚太区销售及市场总监张宇清坦言得益于28nm工艺技术,赛灵思推出了统一架构,将整体功耗降低一半且具有业界最高容量(200万逻辑单元)的7系列FPGA产品,不仅能实现出色的生产率,解决 ASIC 和 ASSP 等其他方法开发成本过高、过于复杂且不够灵活的问题,使 FPGA 平台能够满足日益多样化的设计群体的需求。在 28 nm工艺节点上,静态功耗是器件总功耗的重要组成部分,有时甚至是决定性的因素。由于提高可用系统性能和功能的关键在于控制功耗,因此为了实现最高功效,首先必须选用适合的工艺技术。赛灵思选择了HKMG高性能低功耗工艺技术,以使新一代 FPGA 能最大限度地降低静态功耗,确保发挥 28 nm技术所带来的最佳性能和功能优势。与标准的高性能工艺技术相比,高性能低功耗工艺技术使得 FPGA 的静态功耗降低了 50%,总功耗也减少 50%。同时,新一代开发工具通过创新时钟管理技术可将动态功耗降低 20%,此外,通过部分重配置技术的增强,帮助设计人员进一步降低功耗并减少系统成本33%。

Synopsys公司战略联盟总监Kevin Kranen认为企业纷纷向先进工艺迁移的主要原因有三点。

成本/晶片面积/集成度:目标实现智能电话、平板电脑和智能电视等终端产品的物料(BOM)成本最低化。GF预计,他们的28SLP工艺密度是传统40LP工艺的两倍。通过将应用处理器、图形、内存控制器、视频编码/解码、标准连线接口(USB、MIPI)和标准无线接口(WiFi、蓝牙和LTE)集成在单一的系统级芯片上,企业可以大幅降低终端产品成本,并且可以制造出更小更薄的产品。集成后降低成本/缩小体积带来好处的例证之一就是iPad 2使用的Apple A5。通过目前在45nm中的应用,集成使苹果公司产品与分立式芯片相比在成本、性能和外形方面具有显著优势。

功耗:集成的诸多好处和使用高阶节点有助于降低功耗和延长电池寿命。GF估计,与传统的40G工艺相比,在指定速度下,他们的28HPP工艺每个交换机使用的功耗减少了一半,待机功率也只有30%。

性能:设计人员还可以在相同有效功率下从设计部分提高性能。与40LP工艺相比,GF的28SLP速度提高了80%。

新工艺新挑战

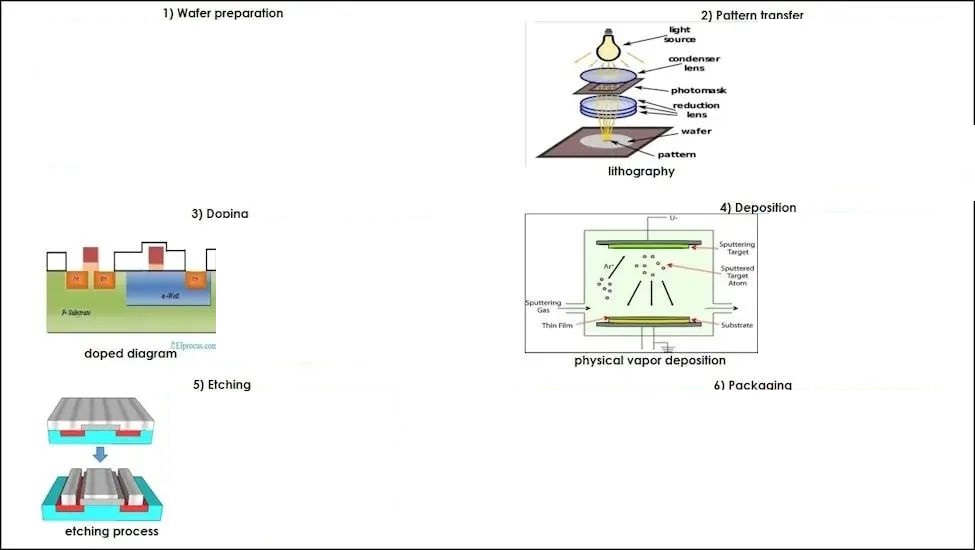

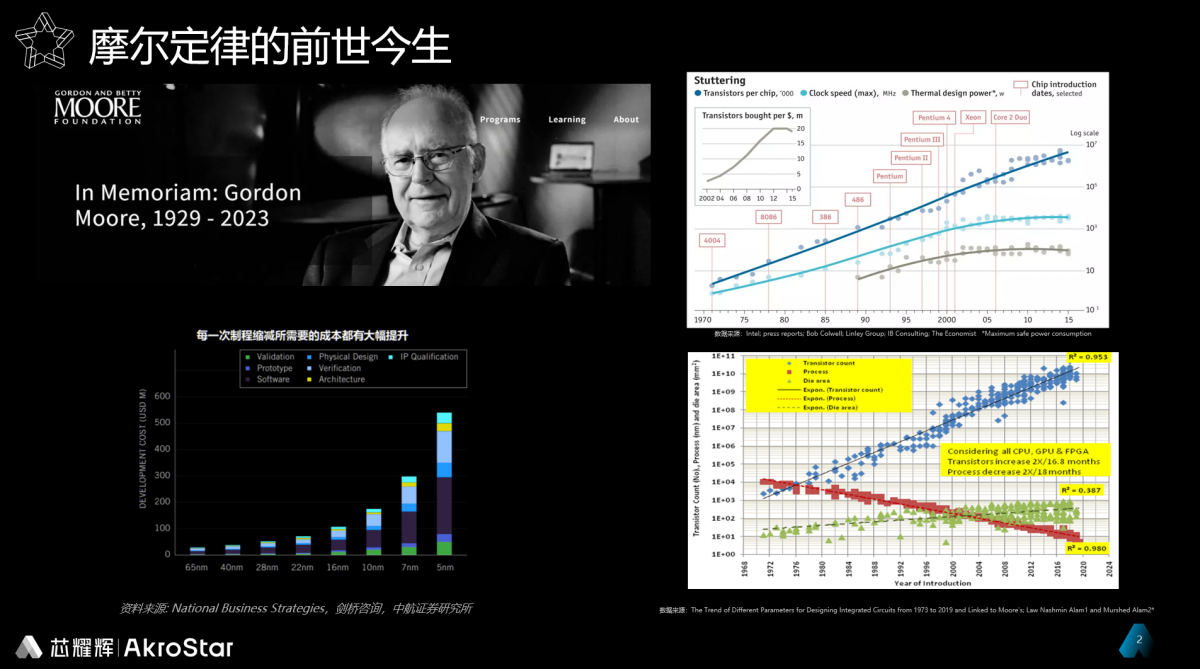

新工艺带来新竞争优势的同时,将许多设计和制造上的挑战也带给整个业界,为此,要求设计者与EDA(电子设计自动化)和晶圆厂之间保持良好的合作以应对全新的设计和制造挑战。随着半导体工业按照摩尔定律的规则,力争使芯片上集成的晶体管数量成倍增加,新的技术挑战在不断涌现。在不牺牲功耗甚至降低功耗的前提下,提高处理性能是半导体厂商亟待解决的另一项技术挑战,这就需要整个产业链的通力协作。

随着芯片特征尺寸缩小,因为20nm以下制程的分散性,寄生效应和器件可变性增强。理解这些新的效应并如何有效地给它们建模是芯片设计的一大挑战。Jean-Marc Chery介绍,意法半导体与所有的主要的EDA企业密切合作,为客户提供设计工具,帮助客户克服新技术节点带来的设计复杂性问题。事实上,处理好设计复杂性增加问题,能够为客户提供有效的设计工具,保证甚至缩短客户基于新技术节点的产品上市时间,是半导体公司要解决的最大挑战之一。事实上,对于30nm以下制程,能够克服这些挑战的主要芯片厂商的数量正在减少,当然,意法半导体是这些为数不多的主要厂商之一。

新的工艺离不开出色的EDA工具,工具开发商在高阶工艺阶段面临三项高层次的挑战,另外还有几个相关的具体问题和解决方案。这方面的挑战包括:管理日益复杂的系统级芯片(SoC)的几何体积越小,意味着系统级芯片内容越多,复杂程度越高;改善系统级架构验证和实施,更多地使用预验证、易于集成的商业IP(知识产权)以及采用更好更高效的验证方法;提高实施、签核与验证的准确性以及改善吞吐量/上市时间/风险。

谈及对SoC(系统级芯片)设计师在新的节点中将会遇到的工具和方法的转变, Kevin Kranen认为,新节点面临的挑战各不相同:32nm和28nm的EDA工具需求相同,其所面临的主要挑战包括以下几方面。

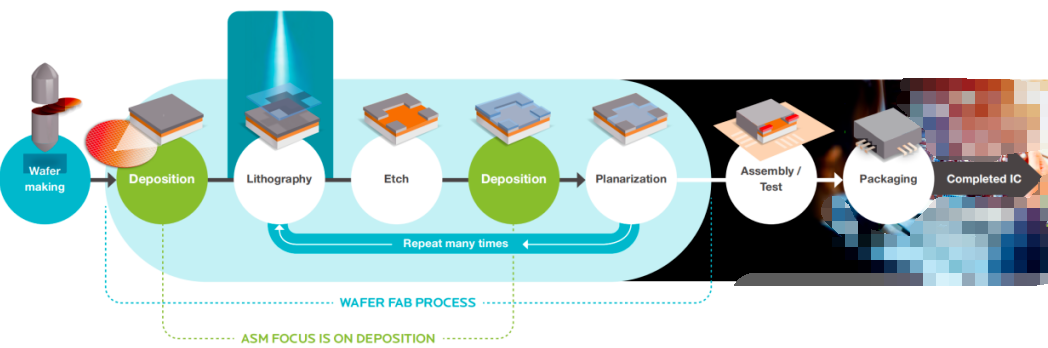

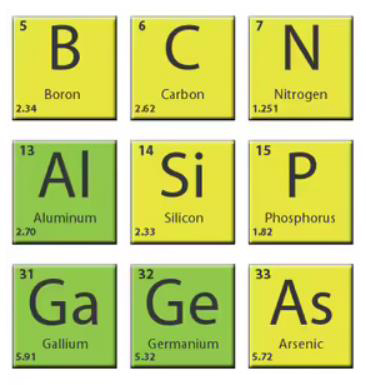

1. 由于氮氧化硅(SiON)栅极介质厚度过薄难以控制,在降低栅极漏电和阈值变异性方面遇到挑战。目前,各大芯片代工厂纷纷转向新的材质和高K金属栅极(HKMG)工艺技术(先栅极和后栅极工艺)。这一变化导致了必须在布线工具和设计规则检查(DRC)工具中纳入新的设计规则。

2. 在193nm光刻基本限值下作业的挑战。设计师必须加强对实施和签核的光刻检查。目前,各个领先的芯片代工厂均要求用户在提交设计前实施某种形式的光刻检查。比如,针对不同Foundry(代工厂)的特点,Synopsys提供不同的工具来协助识别和排除那些导致光刻问题和其它影响良率的设计。

3. 用于参数提取的新工艺拓扑结构建模方面的挑战。目前,各大领先芯片代工厂正创建新的“通孔接触”(via and contact)拓扑结构,来改善芯片的可制造性和维持其密度。STAR RC等提取工具已得到了更新,以更好地了解新的通孔蚀刻效应和凹刻接触技术。

4. 管理参数异变性,尤其是在签核期间异变性的挑战。参数异变性,对比此前工艺节点中的状况,其百分比相对基准数据已出现了显著增长,不过利用最坏情况分析法又过于悲观。目前,芯片代工厂和设计师开始要求采用高级片上变异(AOCV)设计和分析方法,来限定变异性和提供准时的签核。同时要求EDA工具必须具备AOCV分析能力。

与此对应,22/20nm则有不同的要求,EDA工具面临的主要挑战包括以下4点。

1. 新限制性设计规则的增加,以确保利用193nm可成功实现绝对分辨率限值的光刻。为适应这些新规则的要求,必须对布局和布线工具以及DRC检查进行升级。

2. 对于部分层级超越193nm光刻的限值方面的挑战。包括通孔和金属齿距在内的部分芯片层不能在单一光罩内进行投影成像,这是因为这些芯片层在20/22nm工艺下体积太小,密度太大,必须采取双图案模式,将一个单一芯片层的特性分离在两个光罩内。双图案模式提出了新的间距要求,可能增加设计的面积。不过,智能化的布局和布线可以在实际实施时,缓解双图案模式对面积产生的绝大部分影响。

3. 新的提取需求部分22/20nm工艺增加了凹刻接触等新的结构和拓扑,要求必须具备新的提取能力。

4. 向鳍式场效晶体管(FINFET)/TriGate结构的演进对整个半导体行业造成了重大影响的英特尔宣布,他们将转向利用TriGate晶体管制造22nm芯片。FINFET/TriGate结构对提取和SPICE模拟具有更高的要求,Synopsys已经开始在EDA工具中考虑这些问题。同时,工艺和设备工程师要在FINFET上开展工艺或设备模拟,也必须拥有从二维TCAD转向三维TCAD能力。

代工厂角度,陈家湘介绍,为了因应全新设计的挑战,TSMC与fabless(无晶圆半导体)客户应该更早、更深入及更紧密的合作,结合双方的优势共同因应未来在设计与技术上的挑战。首先,foundry与fabless 应更早一步定位产品的设计;其次,双方应该更深入地加强硅IP的合作,共同追求可制造性设计(DFM)与设计规范限制(RDR)等设计工具的一致性,进一步从设计到生产的过程中共同解决问题,提升产品质量。目前,TSMC 28nm设计生态环境已准备就绪,发表包括设计参考流程12.0版(Reference Flow 12.0)、模拟/混合讯号参考流程2.0版(Analog/Mixed Signal Reference Flow 2.0)等多项最新的定制化设计工具,强化既有的开放创新平台设计生态环境,帮助客户更快更好的开发28nm产品。另外,28nm产品已进入量产,客户采用TSMC开放创新平台(Open Innovation Platform)所规划的28nm新产品设计定案(tape out)数量已经超过80个。

电子发烧友App

电子发烧友App

评论