基于架构和基于流的DFT方法 ASIC设计平均门数的增加迫使设计团队花费20%到50%的ASIC开发....

无矢量测试:高速I/O的最佳选择 大批量制造商必须解决如何经济高效地测试多个多线高速I的难题/O接口....

开放式架构ATE解决测试困境 片上系统(SoC)测试提出了无与伦比的挑战,需要对IC制造商和测试人员....

在大多数键盘中,按一个键会关闭一个桥接xy矩阵中两条线的触点。如果使用微控制器检测键闭合,则检查(x....

迈向嵌入式系统的自诊断API 随着嵌入式系统需求的增长和开发周期的缩小,开发人员越来越多地集成商业应....

高密度数字CMOS工艺提供的低晶圆成本使其成为混合信号ASIC的首选,特别是对于片上系统设计。能够在....

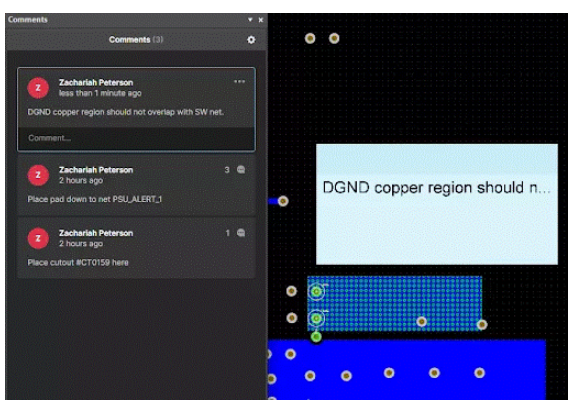

IC设计人员非常清楚“两周到出带模式”实际上可能持续数月,导致错过里程碑和失去市场窗口。尽管使用了先....

在减少EMI问题时,大多数同轴电缆表现相同。它们都是普通电流的良好天线,可以辐射并通过FCC认证类型....

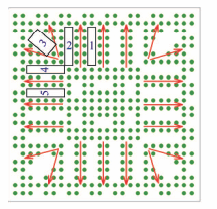

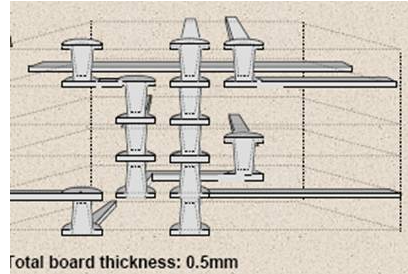

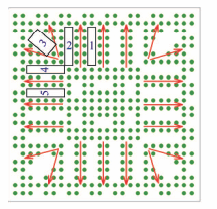

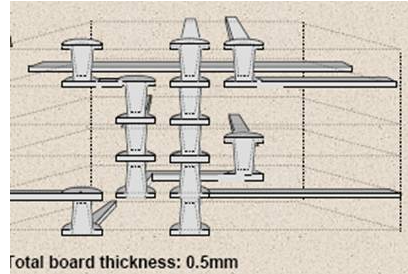

OMAP3530 CUS 封装采用称为 Via Channel™ 阵列的新技术设计。该技术允许使用标....

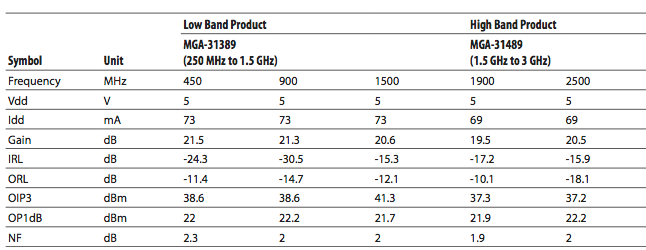

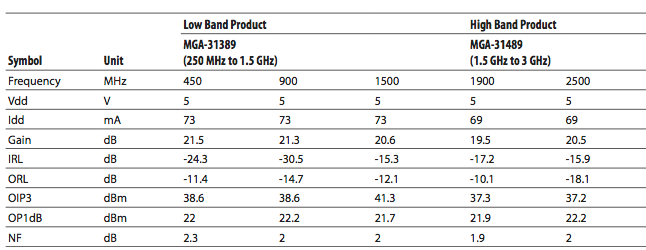

Avago Technologies 的 MGA-31389 和 MGA-31489 是 0.1 瓦....

作者:Maurizio Di Paolo Emilio 由于劳斯莱斯的要求,Trackwise 最初....

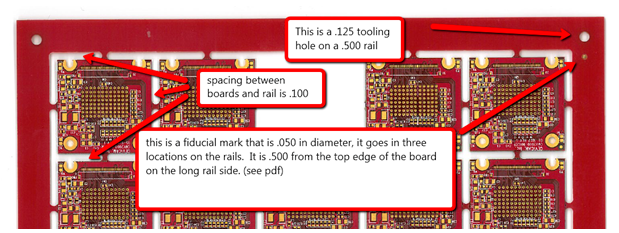

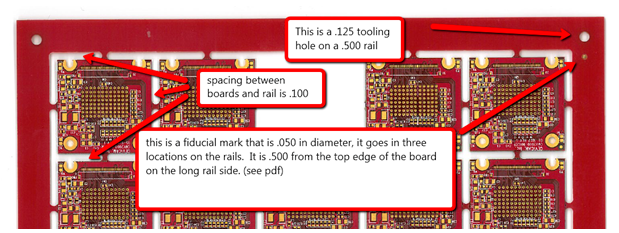

此过程称为“逐出”单个板。它通常被称为“逐步重复”。用于描述阵列的其他术语有:镶板、分步、托盘化和溃....

交流电通过桥式整流器BR1整流。电感器 L1、L2 和电容器 C1、C2 形成一个 pi (π) 滤....

ASMT-Mxxx / ASMT-Axxx / ASMTJxxx是Avago的高功率LED发射器,可....

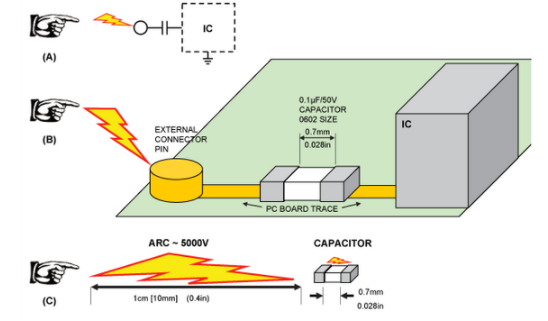

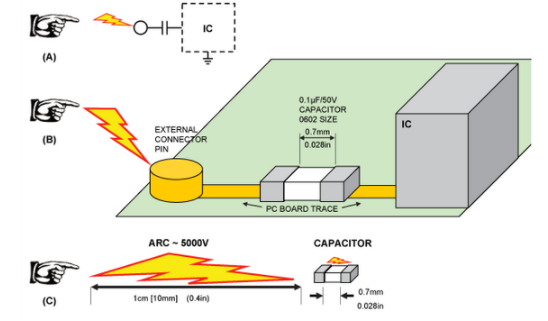

出于显而易见的原因,EOS和ESD可能会在制造,封装组装和测试过程中损坏零件。但更重要的是,这些负力....

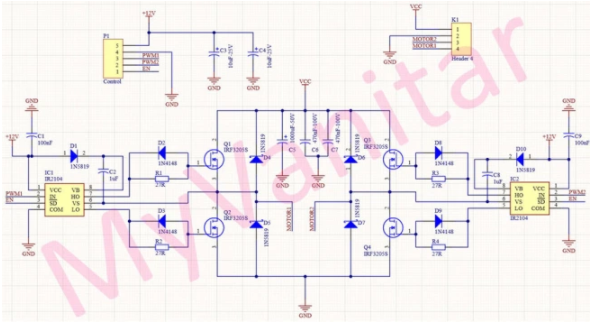

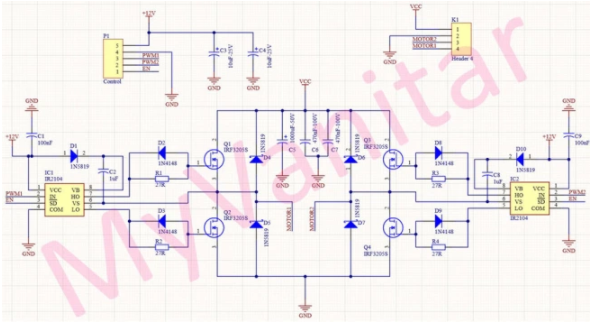

H桥(全桥)驱动器在驱动有刷直流电机等负载方面非常流行,并且已广泛用于机器人技术和工业中。使用H桥驱....

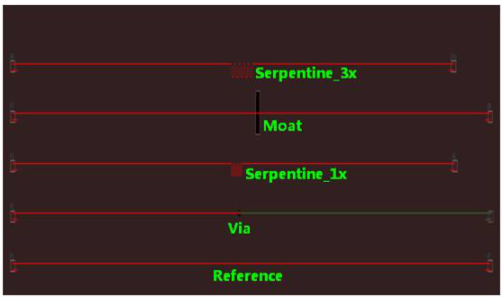

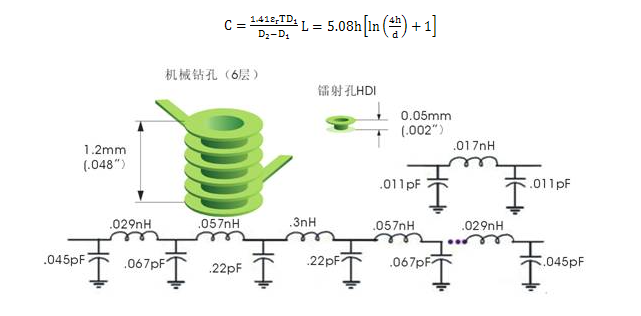

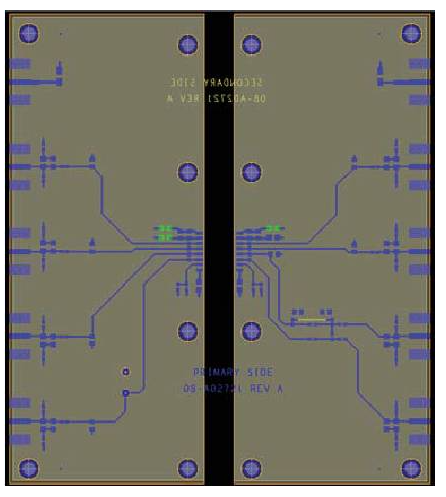

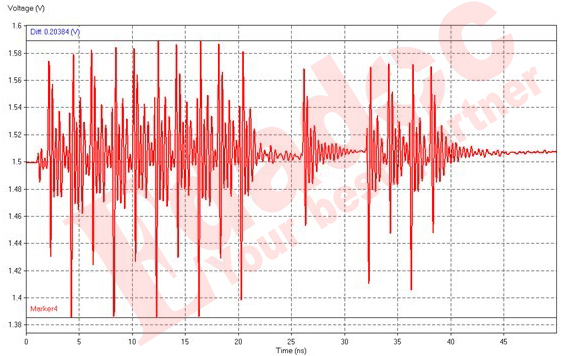

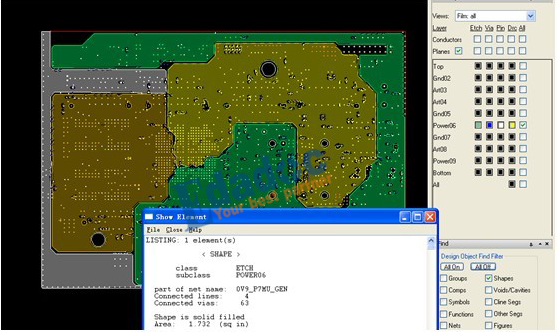

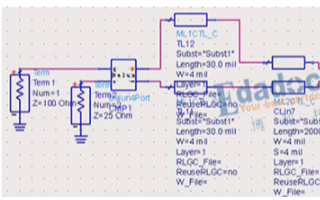

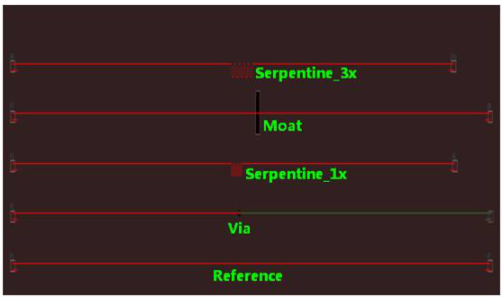

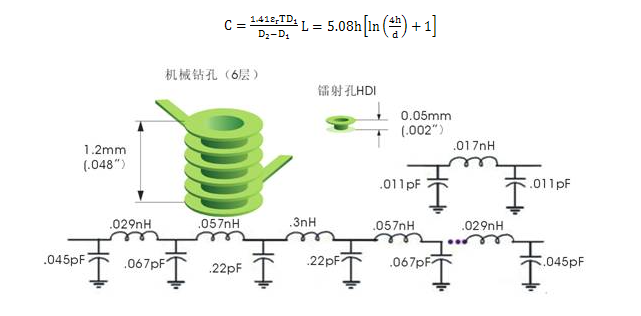

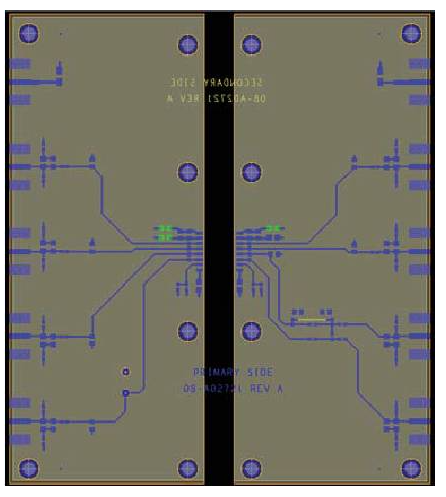

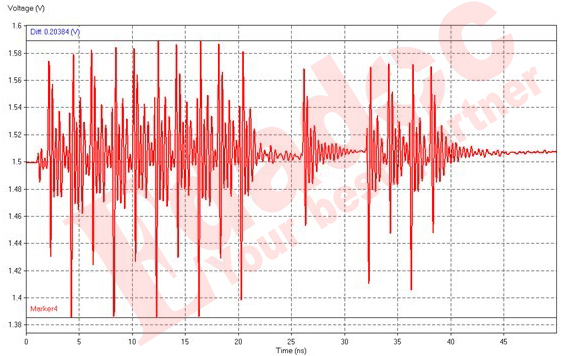

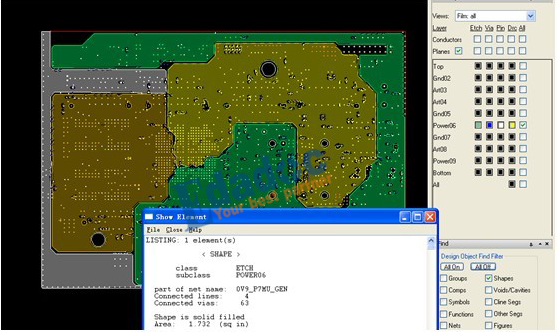

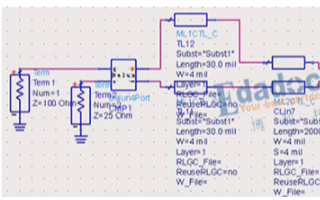

HDI设计在高速中的应用以及仿真方法 高速串行总线技术的发展,信号传输速率继续提升,过孔寄生参数带来....

如果还是需要设置不同层的过孔,会增加管理难度。需要设计工具具备智能化打孔的能力,同时能随意的进行组合....

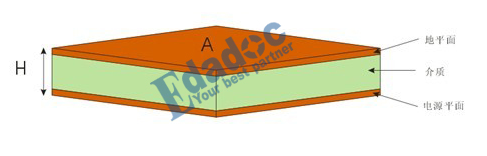

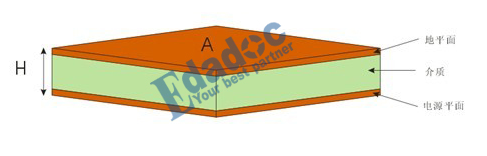

PCB设计尽量让电源平面和地平面紧耦合,让邻近的两个面之间形成耦合平面电容。

添加封装寄生电感和Die电容的参数,准确仿真整个PDN路径的阻抗。这个方法困难的地方在于很多时候拿不....

从仿真结果可以看到,随着电源地之间的间距减小,加入埋容材料,平面谐振点向低频偏移,同时低频的阻抗也大....

一个良好的层叠,正常情况下已经考虑了平板间电容,所谓埋容设计只是采用特殊的材料来加大这个平板间电容。

据说数学家很痛恨物理学家,因为数学家辛辛苦苦推导出来的结论居然和物理学家猜出来的结论是一样的。当然这....

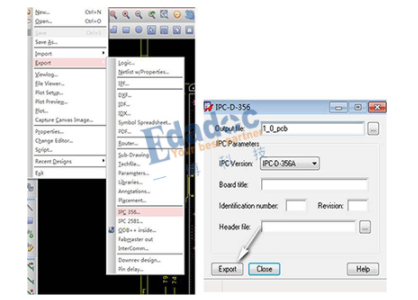

PCB电测是一种有效的印制板最终检验方法。 大家都知道我们成品PCB在交货之前都要100%进行电测,....

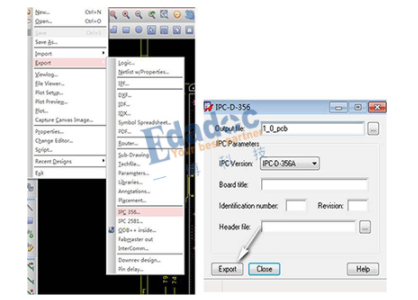

设计与制造是产品生命周期中最重要的两个环节,随着电子业及PCB制造业的蓬勃发展,行业内的竞争达到白炽....

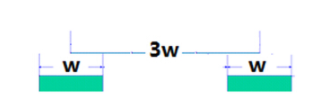

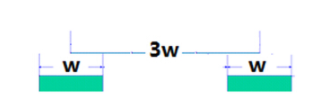

在PCB设计初期,确定差分信号线宽间距时,我们会面对这么个选择:相同的阻抗管控,对应着不同的线宽间距....

应在制造后自动或手动检查电路板。通过自动检查可以识别的一些缺陷包括走线尺寸和间距违规、缺失或短路的焊....

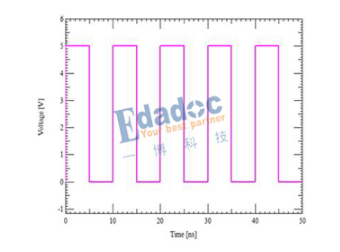

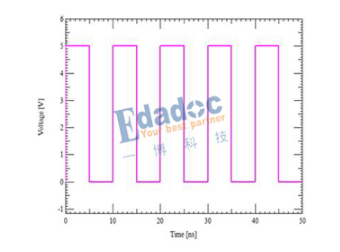

在数字电路中,芯片与芯片之间传输的是数字信号,数字信号是0、1这样的脉冲信号。完美的数字信号应该是图....

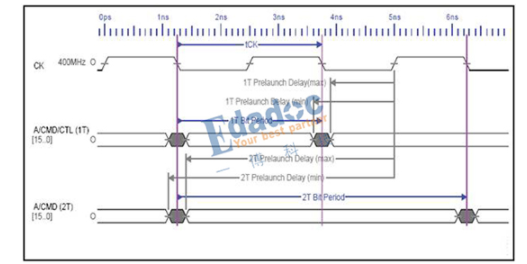

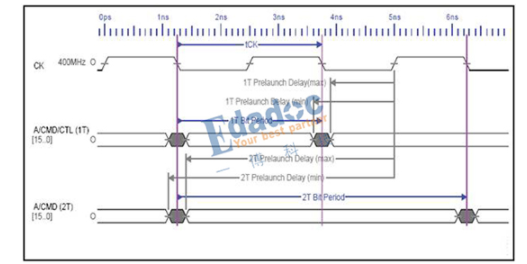

高速先生前几期的自媒体文章里多次提到了时序,并且也写了很多时序方面的文章,这些文章都从不同的角度对时....

1倍线宽的蛇形绕线带来的延时差异是-10ps,比参考线快了10ps,造成延时差异的主要原因是信号的自....