Codasip推出低功耗嵌入式处理器核和设计自动化工具集CodasipStudio

与同级内核相比,CodasipL110每瓦性能提高50%,代码规模缩小20% 德国慕尼黑,2024年....

Codasip高可靠性的定制计算解决方案满足不同领域的需求

又到一年尾牙时!11月的第二个星期对于Codasip来说是个繁忙且收获满满的一周,我们以RISC-V....

Codasip致力于提供卓越的定制计算解决方案

2023第29届中国集成电路设计业年会(ICCAD)是中国半导体和集成电路设计领域的一场盛会,来自世....

Codasip利用RISC-V向量扩展实现领域专用加速器

Codasip Labs 致力于创新并深耕于创新的商业化落地。随着人工智能(AI)和机器学习(ML)....

Codasip推出全新高度可配置的RISC-V基准处理器系列

RISC-V定制计算领域领导者 Codasip 今天宣布推出全新高度可配置的RISC-V基准处理器系....

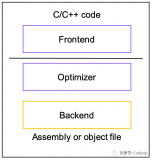

可定制RISC-V ISA的优势

多样性与兼容性的统一 处理器供应商一直试图在其产品周围创建一个庞大的软件生态系统,因为这可以产生黏性....

Codasip向客户提供Tessent Enhanced Trace Encoder增强型追踪编码器解决方案

德国慕尼黑,2023年9月5日——RISC-V定制计算领域的领导者Codasip宣布:公司现在可为其....

处理器设计技能的短缺有哪些

众所周知,使用 "现成 "处理器内核的传统设计方法存在局限性。传统上,软件工程师试图使代码适应所....

Codasip的系列RISC-V处理器助力RISC-V生态建设

德国慕尼黑,2023年6月—RISC-V定制计算领域的领导者Codasip日前宣布,其已选择 Sma....

Codasip致力于创建一个高效的数字耳朵

Codasip Labs之前与NimbleAI的项目合作旨在于推动神经形态视觉的边界扩展。而如此....

看看4种不同类型的CPU漏洞

在设计一个复杂的处理器内核时,可能会出现1000到2000个不等的bug,经验告诉我们这是事实,尽管....

Codasip协作引领RISC-V的广泛采用

在业界屡获奖项的Codasip L31是一个小型、高效的32位嵌入式RISC-V处理器核,针对低功耗....

为处理器验证创建一个“瑞士奶酪模型”,以保证高效的验证品质!

在应用于处理器验证的瑞士奶酪模型中,其原理类似于航空业:如果有一条直接穿过所有切片的路径,那么飞机就....

是什么定义了处理器漏洞的复杂性以及如何检测它?

为了衡量一个漏洞的复杂性,我们可以对漏洞进行分类,供整个处理器验证团队来使用。在之前的一篇博文中,我....

Codasip宣布新人事任命 满足客户对可定制RISC-V处理器的强劲需求

可定制RISC-V处理器知识产权(IP)的领导者Codasip日前宣布:已任命胡征宇(Julian ....