FPGA/ASIC技术

电子发烧友本栏目为FPGA/ASIC技术专栏,内容有fpga培圳资料、FPGA开发板、FPGA CPLD知识以及FPGA/ASIC技术的其它应用等;是您学习FPGA/ASIC技术的好栏目。FPGA中有限状态机的状态编码采用格雷码还是独热码?

有限状态机是由寄存器组和组合逻辑构成的硬件时序电路,其状态(即由寄存器组的1和0的组合状态所构成的有限个状态)只可能在同一时钟跳变沿的情况下才能从一个状态转向另一个状态,究...

2023-04-07 1981

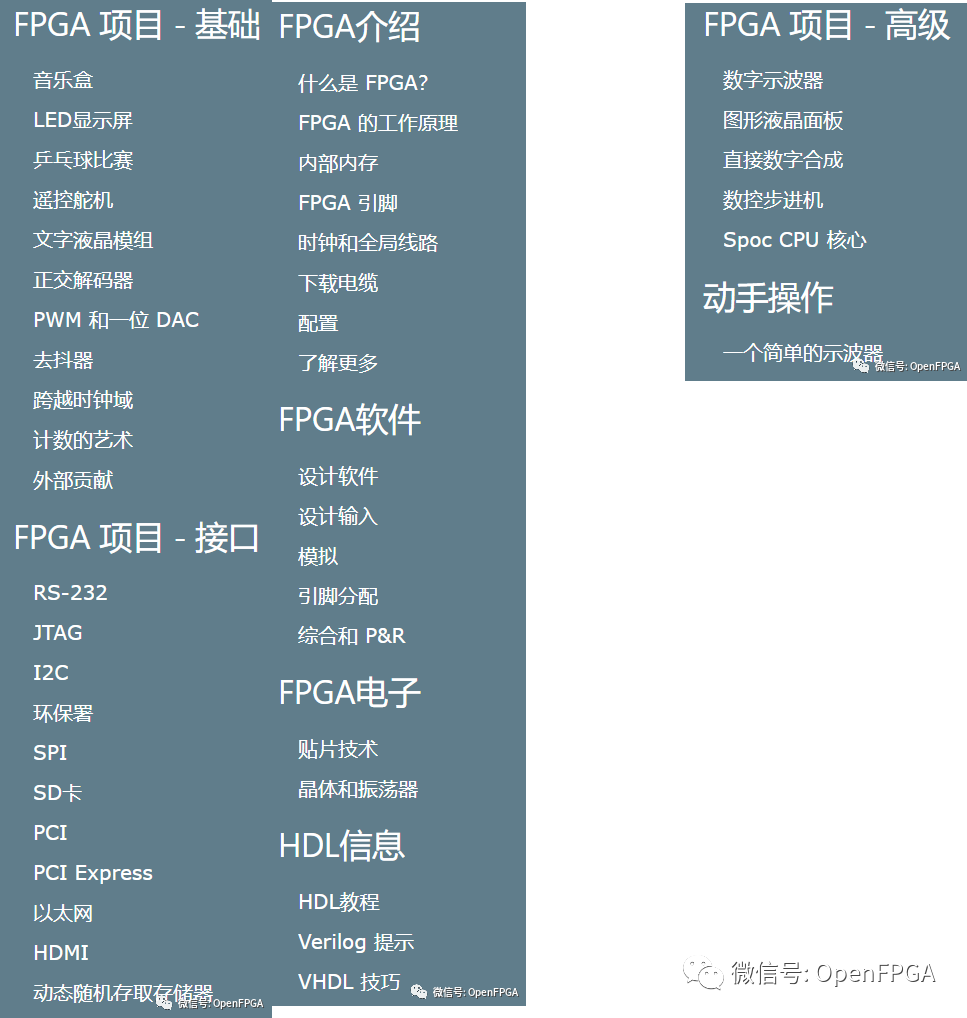

FPGA有哪些优质的带源码的IP开源网站?

FPGA 项目使用一种称为 Verilog 的语言,您需要学习它才能理解项目。但是通过此处显示的示例以及其他可用的在线资源,这并不太难。...

2023-04-06 1322

基于FPGA实现分离用软件的图像处理系统设计

灰度直方图统计直方图是图像的灰度分布统计的一种表示方法,统计目标图像中各个灰度点的像素个数,很多对于图像的调整算法都是基于此进行的;如何基于FPGA进行统计呢?1)由于是统计图...

2023-04-04 1563

PYNQ经典项目分享:可重配置IO

上图为工程项目示意图。通过软硬件划分,在PS端中负责Linux和通信,PL端例化了6个PR(Partitial Reconfiguration)块。每个块中有GPIO、uart和IIC等几种不同的RM(Reconfiguration Module)...

2023-04-03 1342

FPGA有哪些优质的带源码的IP开源网站?

Opencores是一个开源的数字电路设计社区,它提供了免费的开源IP(知识产权)核心,让工程师和爱好者们可以使用这些IP核心来构建自己的数字电路设计。Opencores的IP核心包括处理器、总线接口、...

2023-04-03 1943

几方面简单说明一下:EDA、IP、编译速速、生态

尤其是在使用逻辑分析仪时候,会重新生成新的二进制文件(新的文件名),而上图的文件位置并不会更新成新的文件,需要重新选择,这两点很容易让你下载到FPGA的目标文件和生成的文件并...

2023-04-03 1425

LVDS高速ADC接口, xilinx FPGA实现

使用的AD芯片是ADI的AD9653,125M16bit高精度高速ADC,用到的采样速率是80M。其SPI配置会单独开一篇来讲,SPI配置里面有个大坑,本来以为调好了的,后来又发现了问题,调了三天才定位到问题在哪...

2023-04-03 6551

ASIC芯片分类及特点分析

在集成电路界ASIC被认为是一种为专门目的而设计的集成电路,是指应特定用户要求和特定电子系统的需要而设计、制造的集成电路。ASIC的特点是面向特定用户的需求,ASIC在批量生产时与通用集...

2023-03-31 2531

在FPGA上实现一个模块,求32个输入中的最大值和次大值

从算法本身来看,找最大值和次大值的过程很简单;通过两次遍历:第一次求最大值,第二次求次大值; 算法复杂度是O(2n)。FPGA显然不可能在一个周期内完成如此复杂的操作,一般需要流水设计...

2023-03-31 1238

FPGA应用的电源模块的选择案例

现场可编程门阵列 (FPGA) 是许多原型和中小批量产品的核心。FPGA 的主要优势是开发过程中的灵活性、简单的升级路径、更快的上市时间和相对较低的成本。一个关键的缺点是复杂性,FPGA 通...

2023-03-30 2066

时序分析是FPGA设计中永恒的话题

时钟的时序特性主要分为抖动(Jitter)、偏移(Skew)、占空比失真(Duty Cycle Distortion)3点。对于低速设计,基本不用考虑这些特征;对于高速设计,由于时钟本身的原因造成的时序问题很普遍,因此必须...

2023-03-30 893

基于XILINX FPGA的硬件设计总结之PCIE硬件设计避坑

一个GT Quad由四个GT车道组成。为PCIe IP选择GT Quads时,Xilinx建议您在最靠近PCIe硬块的地方使用GT Quad。虽然这不是必要时,它将改善设计的位置,路线和时间。...

2023-03-30 4288

逻辑综合在整个IC设计流程RTL2GDS中的位置

根据摩尔定律的发展,晶体管的Poly的最小栅极长度已经到达了1nm甚至更小,集成电路的规模越 来越大,集成度越来越高。...

2023-03-27 2165

赛灵思的局部重配置技术(Partial Reconfiguration)

一般情况下,要重新配置一个FPGA需要使其处于复位状态,并通过外部控制器重新加载一个新设计到器件中。而局部重配置技术允许在FPGA内部或外部的控制器在加载一个局部设计到一个可重配置...

2023-03-17 2336

初识FPGA CLB之LUT实现逻辑函数

LUT中文名字叫查找表。以7系列的FPGA为例,每一个Slice里面有四个LUT。FPGA就是通过LUT实现大量的组合逻辑,以及SLICEM里面的LUT还可以构成RAM,Shift Register,以及Multiplexers。这篇文章我们一起来学习...

2023-03-13 3524

FPGA设计总结十五条

Verilog作为一种HDL语言,对系统行为的建模方式是分层次的。比较重要的层次有系统级(system)、算法级(Algorithm)、寄存器传输级(RTL)、逻辑级(Logic)、门级(Gate)、电路开关级(Switch)...

2023-03-06 1177

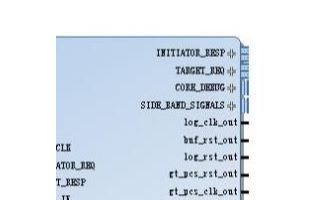

Xilinx RapidIO核例子工程源码分析

srio_quick_start模块在顶层srio_example_top.v中例化,它与IP核的维护端口相连用来产成维护事务,维护事务在maintenance_list.vh中进行定义,用户可以根据需要编辑maintenance_list.vh文件来添加,修改和移除...

2023-03-03 3051

SRIO IP核的三层协议的作用?

数据从远程设备(假设为DSP的SRIO端)传输过来,FPGA端(假设我们这端为FPGA的SRIO端口)通过RX接收到串行数据,先到达物理层进行时钟恢复,串并转换,之后进行8b/10b解码操作、CRC校验,这一系...

2023-03-03 1192

2023年全国大学生集成电路创新竞赛紫光同创赛道正式启动

竞赛背景 逐梦芯时代,青春正当燃。由工业和信息化部人才交流中心主办,紫光同创参与协办的“2023年第七届全国大学生集成电路创新创业大赛...

2023-02-28 3320

中科亿海微获“车规级计算类芯片优质供应商”荣誉

随着电动化、智能化的提速,汽车信息化水平空前提升,汽车功能的增多以及更多高科技配置的使用,使得芯片应用快速增加,从动力系统,到车机系统,再到安全系统,都能看到芯片的大量...

2023-02-23 2587

高端SerDes集成到FPGA中的挑战

在过去的几十年里,电子通信行业一直是 FPGA 市场增长背后的重要推动力,并将继续保持下去。这背后的一个主要原因是 FPGA 中内置了许多不同的高速接口,以支持各种通信标准/协议。实现这...

2023-02-22 1744

你必须知道的FPGA硬件属性

触发器可以被配置(编程)为寄存器或锁存器;复用器可以被配置为选择一个到逻辑块的输入或 LUT 的输出;LUT 可以被配置为代表任何所要求的逻辑功能。在实际应用中,即使最简单的 FPGA 都会使...

2023-02-17 1241

FPGA数字图像处理基础:色彩空间转换(Verilog)

色彩本质上是不同频率的光,人眼对于不同频率光线的不同感受产生主观感知,从而得以区分不同的颜色。尽管从客观上而言,色彩仅仅是不同频率的光,但从视觉角度而言,不同颜色的认知难...

2023-02-17 7439

基于FPGA的图像处理

图像处理的算法中,大部分需要采用浮点数运算,而浮点数运算再FPGA中是非常不划算的,因此需要转换成定点数计算,此时会设计到浮点运算转定点运算时精度下降的问题。...

2023-02-17 2354

FPGA常见的基本设计要点

单元仿真要求代码行覆盖率、条件分支覆盖率、表达式覆盖率必须达到100%,这三种覆盖率都可以通过modelsim来查看,不过需要在编译该模块时要在Compile option中设置好。...

2023-02-16 1211

FPGA编程技巧系列之输入输出偏移约束详解

Pad-to-Setup:也被称为OFFSET IN BEFORE约束,是用来保证外部输入时钟和外部输入数据的时序满足FPGA内部触发器的建立时间要求的。如下图TIN_BEFORE约束使得FPGA在进行DATA_IN和CLK_SYS布线时努力保证DA...

2023-02-15 2408

FPGA器件级的设计决策

选择FPGA器件厂商、器件系列、工具集等,很大程度上还是要考虑设计团队成员的设计经历和偏好。话说“就熟不就生”,因为这在很大程度上会决定了设计复杂性高低和项目进度周期的快慢。...

2023-02-13 806

编辑推荐厂商产品技术软件/工具OS/语言教程专题

| 电机控制 | DSP | 氮化镓 | 功率放大器 | ChatGPT | 自动驾驶 | TI | 瑞萨电子 |

| BLDC | PLC | 碳化硅 | 二极管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 无刷电机 | FOC | IGBT | 逆变器 | 文心一言 | 5G | 英飞凌 | 罗姆 |

| 直流电机 | PID | MOSFET | 传感器 | 人工智能 | 物联网 | NXP | 赛灵思 |

| 步进电机 | SPWM | 充电桩 | IPM | 机器视觉 | 无人机 | 三菱电机 | ST |

| 伺服电机 | SVPWM | 光伏发电 | UPS | AR | 智能电网 | 国民技术 | Microchip |

| 开关电源 | 步进电机 | 无线充电 | LabVIEW | EMC | PLC | OLED | 单片机 |

| 5G | m2m | DSP | MCU | ASIC | CPU | ROM | DRAM |

| NB-IoT | LoRa | Zigbee | NFC | 蓝牙 | RFID | Wi-Fi | SIGFOX |

| Type-C | USB | 以太网 | 仿真器 | RISC | RAM | 寄存器 | GPU |

| 语音识别 | 万用表 | CPLD | 耦合 | 电路仿真 | 电容滤波 | 保护电路 | 看门狗 |

| CAN | CSI | DSI | DVI | Ethernet | HDMI | I2C | RS-485 |

| SDI | nas | DMA | HomeKit | 阈值电压 | UART | 机器学习 | TensorFlow |

| Arduino | BeagleBone | 树莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 华秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS | harmonyos |

发布文章

发布文章