FPGA/ASIC技术

电子发烧友本栏目为FPGA/ASIC技术专栏,内容有fpga培圳资料、FPGA开发板、FPGA CPLD知识以及FPGA/ASIC技术的其它应用等;是您学习FPGA/ASIC技术的好栏目。FPGA所能应用的领域的六大类

在数字信号处理领域 FPGA 同样所向披靡,主要是因为它的高速并行处理能力。FPGA最大优势是其并行处理机制,即利用并行架构实现数字信号处理的功能。...

2022-08-31 806

中科亿海微:坚持全面自主研发道路

1984年,美国公司推出全球第一款FPGA产品。FPGA芯片的技术门槛非常高,一直处于美国公司的垄断之下。处于领跑地位的Xilinx在该领域深耕了30多年,积累了丰富的技术和经验,建立了完整的FPG...

2022-08-30 2611

verilog基础之规范化参数定义parameter

参数传递经常用于顶层的参数传递给子模块,这样我们只需要关注顶层实体的内容,把子模块的内容当做一个黑箱子即可,这也是非常实用的。...

2022-08-30 6647

Vitis HLS介绍及工作流程

这种方法还可以更好地与团队方法一起使用,并且可以创建可跨多个项目使用的加速内核库(IP)。另一个优点是应用于可编程逻辑实现的优化驻留在 .xo 文件中,无需在每次使用算法时重新进...

2022-08-30 4795

FPGA学习之CRC校验

其中有的CRC寄存器初始值设置为全1,如以太网的CRC32,目的就是为了能检测出数据前面的0的个数。1234算出来的CRC,跟01234算出来的,不一样,这就能应对前面带0的数据了。...

2022-08-26 2578

有关AXI IIC和PS IIC的自调试技巧

AXI IIC 和 PS IIC 控制器都符合 NXP IIC 总线规范。用户必须确保其选择使用的从设备的时序参数与UM10204 的第 48 页上的“表 10”中的参数相同。...

2022-08-25 2031

FPGA电路中的毛刺现象

和所有的数字电路一样,毛刺也是FPGA电路中的棘手问题,它的出现会影响电路工作的稳定性,可靠性,严重时会导致整个数字系统的误动作和逻辑紊乱。...

2022-08-25 2087

如何定义新一代FPGA芯片

2022年8月19日,以“图象视界,形智未来”为主题的中国图象图形大会(CCIG 2022)在成都正式拉开帷幕。6位院士领衔百余位国内顶尖学者及知名企业专家,共话图像图形学术研究与技术创新趋势...

2022-08-22 526

关于奇数分频器

第一步:分别使用原时钟上升沿和下降沿产生两个计数器(基于上升沿计数的cnt1和基于下降沿计数的cnt2),计数器在计数到2N时,计数器归零重新从零开始计数,依次循环...

2022-08-22 988

顶级FPGA和GPU的PK

首先,文章使用GPU最擅长处理的工作负载:通用矩阵乘(GEMM)来跑GPU的benchmark(什么是GEMM请移步https://spatial-lang.org/gemm),为了测量最佳的GPU性能,对每个器件使用最新的library,这些库不会出错,并...

2022-08-16 2728

FPGA管脚的调整技巧

完成上述步骤之后,就可以按照正常的BGA出线方式把所有的信号脚进行引出,并按照走线顺序对接排列,但非连接上,如图12-4所示,飞线是交叉的,但是不直接连上。最后保存好所有文档。...

2022-08-13 1059

SDRAM控制器设计

由时序图可知初始化大概的过程为:上电后等待电源VDD和时钟信号稳定100μs(期间命令为空命令),同时在100μs内设置CKE(时钟使能)信号为高。随后对所有Bank发送预充电(PRECH ARGE)命令,发送两次自...

2022-08-13 620

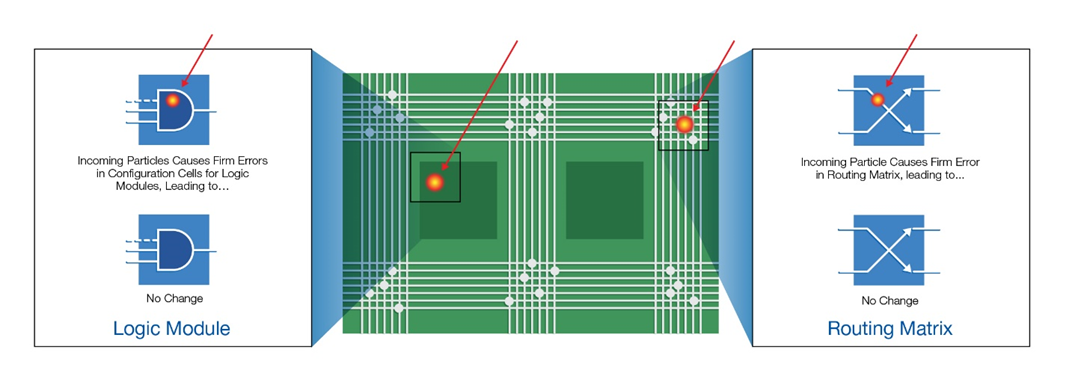

FPGA地盘占了不少,ASIC也依旧玩得愉快

FPGA采用了逻辑单元阵列LCA(Logic Cell Array)这样一个概念,内部包括可配置逻辑模块CLB、输出输入模块IOB和内部连线三个部分。现场可编程门阵列(FPGA)是可编程器件。...

2022-08-08 570

SpinalHDL中如何优雅地实现寄存器总线读写

通过bus slave factory,我们可以方便地实现寄存器读写,其提供了一系列寄存器读写方法。这里列举几个常用的方法(完整的方法列表可参照SpinalHDL-Doc):...

2022-08-05 1107

单片机到底是如何软硬件结合的

初学者,通常有一个困惑,就是为什么软件能控制硬件?就像当年的51,为什么只要写P1=0X55,就可以在IO口输出高低电平?要理清这个问题,先要认识一个概念:地址空间。...

2022-08-03 1545

Verilog在设计时候的不方便地方

从Verilog发布到今天,其已经经历了四十年的风雨,早期的“电路”设计Verilog的确很方便,尤其在那个年代,其也崔进了集成电路的发展。但是“老”不代表方便,尤其高速发展的今天,集成电...

2022-08-02 1029

利用欧拉角与旋转矩阵来对陀螺仪与加速度计的原始数据进行姿态求解

加速度计测量的是其感受到的加速度,在静止的时候,其本身是没有加速运动的,但因为重力加速度的作用,根据相对运动理论,其感受的加速度与重力加速度正好相反,即读到的数据是竖直向...

2022-08-02 7972

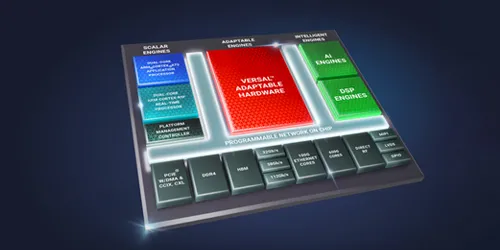

异构平台设计方法 探索赛灵思Versal ACAP设计方法论

身处智能时代,科技发展日新月异,伴随数据中心、有线网络、5G 无线和汽车等愈加丰富的场景,相应的技术与功能也正经历飞速迭代,因此,单一计算架构已难以应对海量数据处理需求,赛灵...

2022-08-02 1082

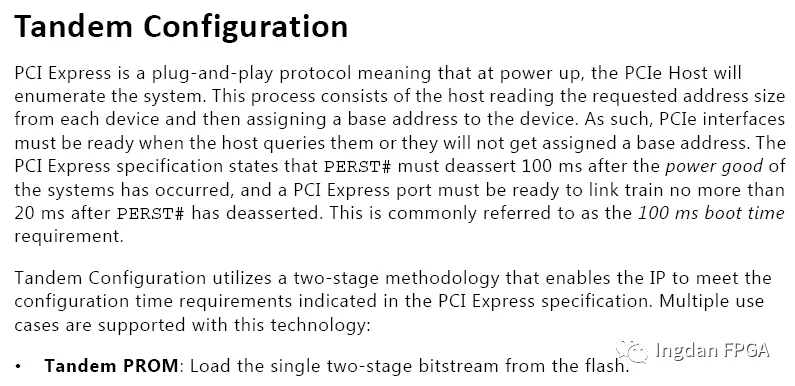

基于ZCU106实现PL PCIE Tandem PROM功能 从而满足100MS之内主板能识别PCIE接口

现在大规模FPGA的bitstream比较大导致板卡从上电到FPGA配置完成的时间远远超过100MS的要求,从而电脑端无法正常识别到PCIE设备。为此Xilinx的PCIE Tandem功能是专为满足PCIe设备在100ms之内枚举起来要...

2022-08-02 3647

FPGA的定义以及和GPU的类比

FPGA 是一堆晶体管,你可以把它们连接(wire up)起来做出任何你想要的电路。它就像一个纳米级面包板。使用 FPGA 就像芯片流片,但是你只需要买这一张芯片就可以搭建不一样的设计,作为交换...

2022-08-01 1106

基于蜂鸟E203 RISC-V处理器内核的SoC设计

SM4算法是一种分组密码算法。其分组长度为128bit,密钥长度也为128bit。加密算法与密钥扩展算法均采用32轮非线性迭代结构,以字(32位)为单位进行加密运算,每一次迭代运算均为一轮变换函...

2022-08-01 2469

基于IDEA导出个人IP库设计的jar包

使用SpinalHDL进行电路描述是基于Scala来实现的,在进行设计输出的时候,那么,我们可以同样基于jar包的形式导出个人IP库设计。本篇就基于IDEA导出个人IP库设计的jar包。...

2022-07-28 563

线程终止的4种方式

PTHREAD_CANCEL_DEFERRED,延迟方式,线程只会在特定的取消点(cancellation points,调用某个函数前)被杀死。...

2022-07-27 1014

RAM——单口、双口、简单双口、真双口的区别

在 WE = 0 时,两个口均为读出口,A 口的地址线 ADDR[3:0] 的地址为 0,在 SPO[7:0] 上读出数据 17,B 口的地址线 DPRA[3:0] 为 0,在 DPO[7:0] 上读出数据 17;...

2022-07-26 10374

ZYNQ7020的程序固化

阶段0,主要是运行芯片内部固化的BootROM程序,这个BootROM主要是识别启动模式(spi/sd/nand/nor/)是哪一种?...

2022-07-22 5980

FPGA帮助改进机器学习的模型训练过程

FPGA传统上被用作设计新数字芯片的早期验证原型已经很久了,但随着机器学习技术的出现,FPGA体现出了有别于传统应用更多的特质。...

2022-07-22 983

编辑推荐厂商产品技术软件/工具OS/语言教程专题

| 电机控制 | DSP | 氮化镓 | 功率放大器 | ChatGPT | 自动驾驶 | TI | 瑞萨电子 |

| BLDC | PLC | 碳化硅 | 二极管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 无刷电机 | FOC | IGBT | 逆变器 | 文心一言 | 5G | 英飞凌 | 罗姆 |

| 直流电机 | PID | MOSFET | 传感器 | 人工智能 | 物联网 | NXP | 赛灵思 |

| 步进电机 | SPWM | 充电桩 | IPM | 机器视觉 | 无人机 | 三菱电机 | ST |

| 伺服电机 | SVPWM | 光伏发电 | UPS | AR | 智能电网 | 国民技术 | Microchip |

| 开关电源 | 步进电机 | 无线充电 | LabVIEW | EMC | PLC | OLED | 单片机 |

| 5G | m2m | DSP | MCU | ASIC | CPU | ROM | DRAM |

| NB-IoT | LoRa | Zigbee | NFC | 蓝牙 | RFID | Wi-Fi | SIGFOX |

| Type-C | USB | 以太网 | 仿真器 | RISC | RAM | 寄存器 | GPU |

| 语音识别 | 万用表 | CPLD | 耦合 | 电路仿真 | 电容滤波 | 保护电路 | 看门狗 |

| CAN | CSI | DSI | DVI | Ethernet | HDMI | I2C | RS-485 |

| SDI | nas | DMA | HomeKit | 阈值电压 | UART | 机器学习 | TensorFlow |

| Arduino | BeagleBone | 树莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 华秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS | harmonyos |

发布文章

发布文章