FPGA/ASIC技术

电子发烧友本栏目为FPGA/ASIC技术专栏,内容有fpga培圳资料、FPGA开发板、FPGA CPLD知识以及FPGA/ASIC技术的其它应用等;是您学习FPGA/ASIC技术的好栏目。FPGA的六大应用领域,你了解吗?

接口和连接资源接口和连接功能主要包括无线基站对外的高速通信接口(PCI Express、以太网 MAC、高速 AD/DA 接口)以及内部相应的背板协议(OBSAI、CPRI、EMIF、LinkPort)的实现。...

2023-02-09 1612

傅立叶变换的实质-正交之美

对于信号,如果我们想用谐波来表示它的话,我们最好基于不同的频率将之进行分解,那么接下来的问题就是寻找一个正交基,它可以表示不同的频率的谐波。换句话说,我们希望用不同频率的...

2023-02-09 1514

基于FPGA的单目内窥镜定位系统设计

本设计对系统的性能和系统的功能分别进行了测试,性能测试是对FPGA的资源利用情况和运行速度情况进行测试,功能测试有腐蚀算法测试,帧差算法测试,定位功能调试等。...

2023-02-07 474

Xilinx FPGA的FMC接口

FMC标准定义了单宽度(69mm*76.5mm)和双宽度(139mm*76.5mm)两种尺寸。单宽度模块支持到载卡的单个连接器。双宽度模块主要面向需要更高带宽、更大前面板空间或较大PCB面积的应用,支持多达两个连接...

2023-02-06 2917

国产FPGA!哪些公司比较牛?

为了满足经济发展和国防需求,打破美国的垄断,中国政府多年来投入了数百亿科研经费,通过逆向工程方式仿制美国对我禁运的FPGA产品。但由于知识产权、生产工艺和软件技术等多方面的限...

2023-02-03 6711

什么是FPGA?它有什么特点?

随着消费电子和通信等终端设备需求总量的增长,人工智能、大数据、云计算、智能汽车以及物联网边缘计算的发展,对FPGA的需求也将大增。相比于CPU、GPU,FPGA并不广为大众所熟知。接下来我...

2023-02-03 3796

一文读懂FPGA

FPGA 的全称为 Field-Programmable Gate Array,即现场可编程门阵列。FPGA 是在 PAL、 GAL、 CPLD 等可编程器件的基础上进一步发展的产物, 是作为专用集成电路( ASIC)领域中的一种半定制电路而出现的,...

2023-01-15 3374

浅析FPGA的应用领域

FPGA 最初的应用领域也是传统的应用领域,通信领域,但随着信息产业以及微电子计数发展,FPGA的应用范围编辑航空航天、汽车、医疗、工业控制等领域。下面分4个方面介绍FPGA的用武之地:视...

2023-01-09 6676

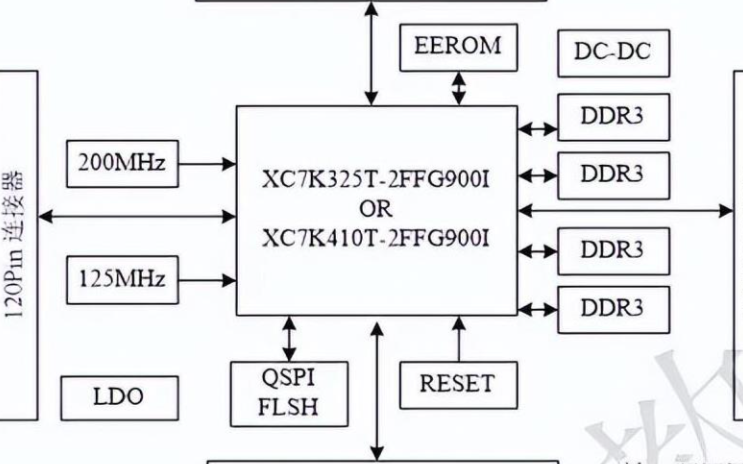

基于Kintex-7 FPGA的核心板电路设计

核心板结构尺寸为65(mm)× 85(mm)。整个开发系统的结构如图1所示,实物图如图2所示。该板很适合高速数据通信;视频采集、视频输出、消费电子;机器视觉、工业控制;项目研发前期验证;电子...

2023-01-09 3835

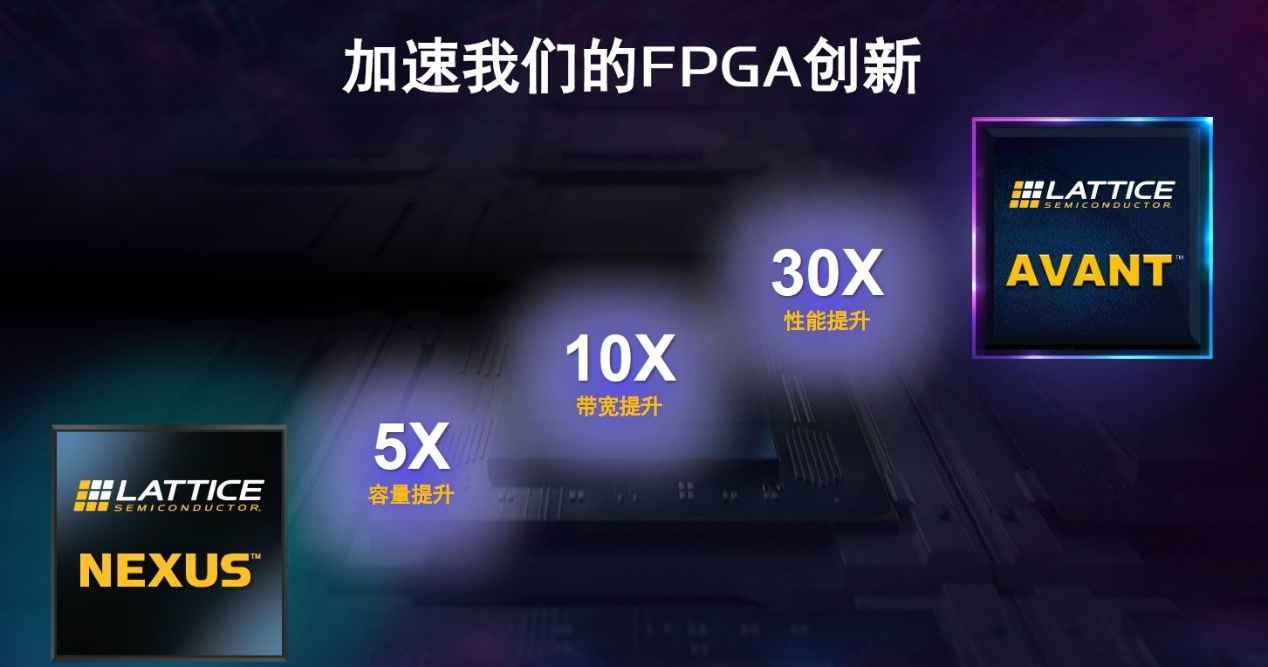

打开通往30亿美元增量市场的新大门

全新低功耗中端Avant FPGA平台的面世,不但意味着莱迪思迈入了中端FPGA供应商的行列,还打开了一扇通往30亿美元增量市场的新大门。 与此前的产品相比,主要面向通信、计算、工业和汽车等...

2023-01-06 3809

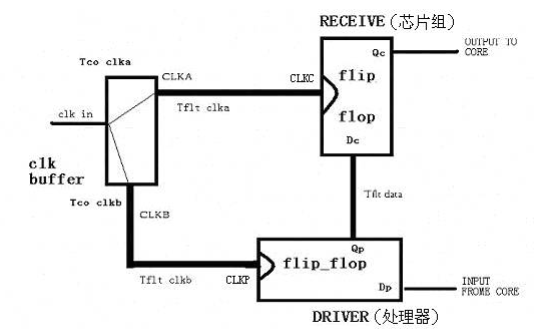

FPGA知识汇集-FPGA时序基础理论

对于系统设计工程师来说,时序问题在设计中是至关重要的,尤其是随着时钟频率的提高,留给数据传输的有效读写窗口越来越小,要想在很短的时间限制里,让数据信号从驱动端完整地传送到...

2022-12-13 2421

京微齐力荣获“硬核中国芯-2022年度最具潜力IC设计企业”奖

2022年11月15日,由半导体电子信息媒体「芯师爷」主办、「慕尼黑华南电子展」协办的“2022年度硬核中国芯领袖峰会暨评选颁奖盛典”在深圳圆满落下帷幕。凭借自主可控、创新型产品和卓越的...

2022-11-16 1160

FPGA拆解FPGA芯片,带你深入了解其原理

现场可编程门阵列(FPGA)可以实现任意数字逻辑,从微处理器到视频生成器或加密矿机,一应俱全。FPGA由许多逻辑模块组成,每个逻辑模块通常由触发器和逻辑功能以及连接逻辑模块的路由网...

2022-11-10 3327

FPGA系统调试与测试及结论

本设计的实现对医院培养的经验少的医生尽快掌握心脏手术操作流程很有价值,未来将可以培养更多从事心脏手术工作的医学专业毕业的学生或刚刚从事这个行业的社会医生。...

2022-10-28 740

FPGA设计的经验技巧

当然,任何编程语言的学习都不是一朝一夕的事,经验技巧的积累都是在点滴中完成,FPGA设计也无例外。下面就以我的切身体会,谈谈FPGA设计的经验技巧。...

2022-10-25 1061

为什么用FPGA来加速YOLOV2

1.GPU加速:GPU是一种多核处理器,GPU起初是用来进行图形处理任务的,经过长时间的发展,GPU的发展是日趋复杂的,而且针对不同的领域也有不同。...

2022-10-25 1758

FPGA有什么特点

最近几年,FPGA这个概念越来越多地出现。例如,比特币挖矿,就有使用基于FPGA的矿机。还有,之前微软表示,将在数据中心里,使用FPGA“代替”CPU,等等。 其...

2022-10-24 1179

如何利用FPGA硬件并行的优势设计高速高精度声源定位系统

我们决定利用麦克风阵列获取声音信号,使用 FPGA 技术计算声音的位置, 使用 OPENMV 实现图像的抓拍,最终实现对鸣笛车辆的准确定位。...

2022-10-17 1687

FPGA常见的IO接口标准设置

最近准备采用Xilinx FPGA进行多机通信,即主FPGA芯片将采集到的不同层的图像数据流分别输出给对应的4块从FPGA芯片中,主从FPGA之间的连接机制采用星形拓扑结构。经计算,图像数据流接口速率需...

2022-10-17 4749

FPGA内ARP和ICMP的关系

FPGA数据处理中常用的一些IP核有网口ETH核、DDR核、CORDIC核、DDS核、加法器、乘法器、滤波器IP、FFT等IP核,这些IP核熟练使用能减少很多工作量和提高代码的稳定性。...

2022-10-14 2208

基于ASIC单个模块的设计/优化思路

ASIC设计中详细设计方案的确定非常重要,同样的设计,别人可以用比你小30%的面积和少30%的处理时间来实现,这才是设计工程师的价值体现之处。...

2022-10-12 527

如何在应用程序中实现 IDELAY 功能

可以在下面看到整体仿真延迟比较小,无法看到该级别延迟的影响。然而,随着仿真执行不同的测试,我们将看到控制信号和抽头值发生变化。...

2022-10-09 2127

AnDAPT为FPGA供电带来领先的完全可编程定制化PMIC

十年前,当我第一次开始为一家 FPGA 公司工作时,我惊讶地发现这些部件需要纷繁复杂的电源轨。我从来没有遇到过需要五到十个甚至更多电源轨的芯片。即使在过去的 PMOS 时代,芯片也只需要...

2022-09-27 1109

编辑推荐厂商产品技术软件/工具OS/语言教程专题

| 电机控制 | DSP | 氮化镓 | 功率放大器 | ChatGPT | 自动驾驶 | TI | 瑞萨电子 |

| BLDC | PLC | 碳化硅 | 二极管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 无刷电机 | FOC | IGBT | 逆变器 | 文心一言 | 5G | 英飞凌 | 罗姆 |

| 直流电机 | PID | MOSFET | 传感器 | 人工智能 | 物联网 | NXP | 赛灵思 |

| 步进电机 | SPWM | 充电桩 | IPM | 机器视觉 | 无人机 | 三菱电机 | ST |

| 伺服电机 | SVPWM | 光伏发电 | UPS | AR | 智能电网 | 国民技术 | Microchip |

| 开关电源 | 步进电机 | 无线充电 | LabVIEW | EMC | PLC | OLED | 单片机 |

| 5G | m2m | DSP | MCU | ASIC | CPU | ROM | DRAM |

| NB-IoT | LoRa | Zigbee | NFC | 蓝牙 | RFID | Wi-Fi | SIGFOX |

| Type-C | USB | 以太网 | 仿真器 | RISC | RAM | 寄存器 | GPU |

| 语音识别 | 万用表 | CPLD | 耦合 | 电路仿真 | 电容滤波 | 保护电路 | 看门狗 |

| CAN | CSI | DSI | DVI | Ethernet | HDMI | I2C | RS-485 |

| SDI | nas | DMA | HomeKit | 阈值电压 | UART | 机器学习 | TensorFlow |

| Arduino | BeagleBone | 树莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 华秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS | harmonyos |

发布文章

发布文章