完善资料让更多小伙伴认识你,还能领取20积分哦,立即完善>

电子发烧友网技术文库为您提供最新技术文章,最实用的电子技术文章,是您了解电子技术动态的最佳平台。

在一些摄像头中,pwdn管脚和rst管脚有时会直接省略掉。pwdn管脚为电源掉电模式管脚,低电平表示为正常模式,高电平表示掉电模式。使用时,将pwdn管脚置为低电平即可。...

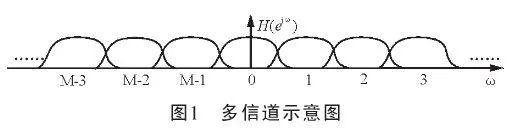

在数字接收机的各种参数中,频率是重要的参数之一,它能反映接收机的功能和用途、以及频谱宽度等重要指标。...

本文主要用来随意记录一下最近在为手头的FPGA项目做约束文件时候遇到的一点关于FPGA专用时钟管脚相关的内容,意在梳理思路、保存学习结果、以供自己日后以及他人参考。...

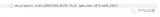

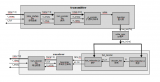

在远程更新的时候,有时候需要双镜像来保护设计的稳定性。在进行更新设计的时候,只更新一个镜像,另一个镜像在部署之前就测试过没问题并不再更新。当更新出错时,通过不被更新的镜像进行一些操作,可以将更新失败的数据重新写入Flash。这样即使更新出错,也能保证设计至少可以被远程恢复。...

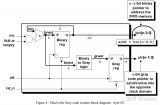

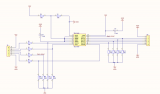

由Binary Pointer生成Gary Pointer,其实这里根据经典AFIFO论文[1]里应该是用新的wptr_bin_next生成wptr_gray_next,这样wptr_bin和wptr_gray可以同步更新。...

双沿时钟使得原本一个周期输出/输入一个数据的架构,改变为一个周期输出/输入两个数据,这样在不升高时钟频率的前提下,提升了信号的吞吐率,从而带来「性能的提升」。...

FPGA可重构技术就是通过上位机控制在FPGA运行过程中加载不同的Bitstream文件,FPGA芯片根据文件内的不同逻辑将内部的资源全部或部分进行重新配置以达到多种功能任务动态切换的目标,从而提高了使用FPGA进行开发的灵活度。...

在FPGA处理完数字信号之后,我们有些情况下是需要将数字信号转变为模拟信号再输出的。比如音频信号在滤波后,需要转换为声音信号进行输出。...

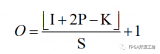

HLS需要bit-reverse命令数据块后端,所说的自然顺序和一个O (N)转换适用于FFT输出提取的频谱数据N-point真实数据集。注意,第一个输出两包第0个和512(纯粹的)分别输出频谱数据的实部和虚部。...

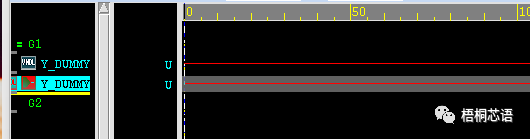

亚稳态这种现象是不可避免的,哪怕是在同步电路中也有概率出现,所以作为设计人员,我们能做的是减少亚稳态发生的概率。...

首先是对 SQL 的支持,比如是否支持 IC SQL,还是会违背 IC SQL 的语法,有很多自己的 SQL 语法。引申就是有没有一些 MySQL 协议或者是 PG 协议,直接可以去对接更好的 BI 工具,能够较少地去改动。...

一般来说,我们认为CMOS数字电路的输出的稳定状态只有2种,就是逻辑0和逻辑1,从模拟信号量来说,就是0V和VDD。...

FPGA 设计工程师需要对如何创建系统以及使用行业软件和工具有深入的了解。在软件方面,设计工程师必须知道如何建模自己的设计,并通过一系列测试保证正确的运行。业界有许多这种高级建模程序,包括Matlab,Simulink,Octave,Verdi等等。...

真实数据是保存在较长的一行。分析后可以看到较长行的长度都是一样的。具体内容是,前端若干位是控制符(包含地址),然后是具体数据,之后是校验码。找到规律后,就可以直接提取其中内容了。...

扩频系统最早可以追溯到20世纪20年代左右,扩频通信就有了初步的应用。但是一直到20世纪年代中期,扩频系统才真正应用和发展起来。...

今天有个小伙伴遇到一个问题,就是在vivado里面综合后看到的建立时间和保持时间裕量都是inf,我们来看看怎么解决这个问题。...