完善资料让更多小伙伴认识你,还能领取20积分哦,立即完善>

电子发烧友网技术文库为您提供最新技术文章,最实用的电子技术文章,是您了解电子技术动态的最佳平台。

双击桌面图标打开Vivado 2017.2,或者选择开始>所有程序>Xilinx Design Tools> Vivado 2017.2>Vivado 2017.2;...

AMD-XILINX FPGA密钥存储支持两种模式: 1)BBRAM电池供电存储 已有公开文献发表,可通过激光注入读取BBRAM中保存的明文密钥,且BBRAM需要电池供电,应用可靠性大大降低。...

首先,AD模块对模拟信号进行采样,触发电路根据采样信号判断触发条件(例如:上升沿触发)。满足触发条件后,连续采样一定数量的点(本系统中为640个点),存储到RAM中。...

对于一个软件开发人员,可能听说过 FPGA,甚至在大学课程设计中,可能拿FPGA做过计算机体系架构相关的验证,但是对于它的第一印象可能觉得这是硬件工程师干的事儿。...

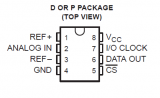

在生活中,数模转换的例子到处可见。但是在我们做FPGA设计时,需要对数字信号进行处理,但是,不是所有的信号都是以数字信号的形式体现的,比如光信号、声信号、电信号等等。...

智能服务器适配器或智能网卡(SmartNIC)通过从服务器的CPU上卸载网络处理工作负载和任务,提高云端和私有数据中心中的服务器性能。...

信号发生器能够产生频率波形可调的信号输出,目前仅限于1Hz~4999Hz频率范围,波形可选择三角波,方波,锯齿波,以及正弦波。本系统在Basys3上构建了一个简易信号发生器。...

I²C 协议提供了 3 种速度模式:正常速度模式 100kbit/s、快速模式 400kbit/s、高速模式3.5Mbit/s。SCL 输出的时钟信号频率和速度模式一致。程序内部使用 5 倍 SCL 信号作为时钟,而 FPGA 外部时钟需要经过分频得到程序内部使用的时钟。...

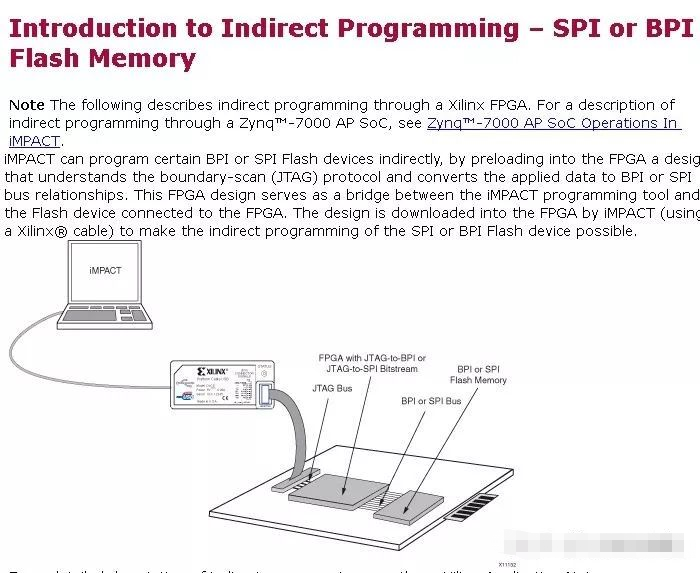

其中待测设计就是我们整个的逻辑设计模块,在线逻辑分析仪也同样是在FPGA设计中。通过一个或多个探针来采集希望观察的信号。然后通过JTAG接口,将捕获到的数据通过下载器回传给我们的用户界面,以便我们进行观察。...

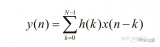

设经过AD采集得到的输入序列为x(n),其通过单位冲激响应为h(n)的因果FIR滤波器后,输出y(n)在时域可表示为线性卷积和的形式...

FPGA(Field-Programmable Gate Array)可以使用多种编程语言进行编程,具体选择的编程语言取决于开发人员的偏好、设计需求和FPGA开发工具的支持。...

“全局时钟和第二全局时钟资源”是FPGA同步设计的一个重要概念。合理利用该资源可以改善设计的综合和实现效果;如果使用不当,不但会影响设计的工作频率和稳定性等,甚至会导致设计的综合、实现过程出错。Xilinx FPGA7系列分为全局时钟(Global clock)和局部时钟(Regional cloc...

平均通信效率低:SoC中采用基于独占机制的总线架构,其各个功能模块只有在获得总线控制权后才能和系统中其他模块进行通信;从整体来看,一个模块取得总线仲裁权进行通信时,系统中的其他模块必须等待,直到总线空闲。...

设计师能够充分利用英特尔 FPGA 的 DSP 性能、带宽和其他功能特性来实现片上系统设计,消除单独使用组件来执行语音处理任务的需求,进而减少成本,特别是多通道音频应用的成本。...

FIFO的英文全称叫做First in First out,即先进先出。这也就决定了这个IP核的特殊性,先写进去的数据优先被读出,所以,FIFO是不需要地址信号线的,这也是它的一大特点,...

搞懂数据段和代码段是如何被链接成一个二进制文件的,这应该是每一个ARM程序员必须搞清楚的一个事情。...

在从事FPGA这个行业之后,在公司做的基本上都是一些“高端”的项目,像这种游戏样的“玩具”,基本上没有哪个公司会拿FPGA去做,杀鸡焉用牛刀,毕竟用个低成本单片机能干的活何必要用FPGA这种高端货呢?...

根据时序参数,决定将IIC的速率定为50KHz。发送时,数据改变在SCL的低电平的正中间;读取时,在SCL高电平的正中间进行读取。...