完善资料让更多小伙伴认识你,还能领取20积分哦,立即完善>

电子发烧友网技术文库为您提供最新技术文章,最实用的电子技术文章,是您了解电子技术动态的最佳平台。

这个EEPROM存储器存放程序的地方对我们来说不必太深究,但有一块特殊的区域我们要知道,以后编程可能会用的到。就是EEPROM存储器除了存储程序以外,还留了一块区域,专门用来存放我们PLC断电以后需要长久保存的数据。上面我们讲到在RAM存储器里的数据断电后是保存不住的,不幸的是我们的程序运行时,运算...

FIFO队列有两个位置指示指针。一个是写指针,指向队列的第一个存储单元。一个读指针,指向队列的最后一个存储单元。当有写命令的时候,数据写入写指针指向的存储单元,然后指针加一。当有读命令的时候,读指针加一,在读出读指针指向的存储单元的数据。这里读命令,指针要加一,是定义读数据,是读出读指针的下一个存储...

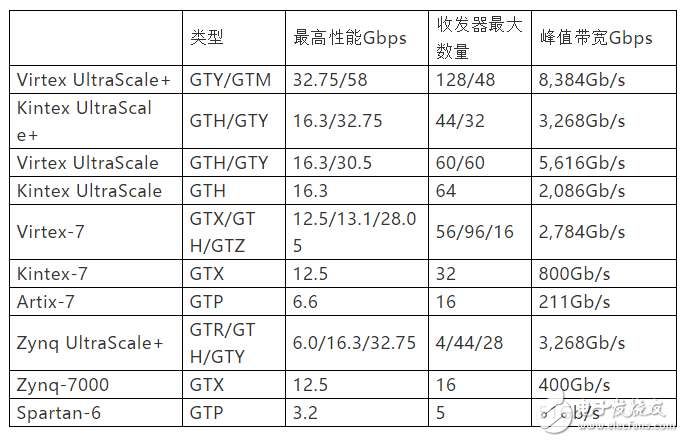

GTx接收和发送方向均由PCS和PMA两部分组成,PCS提供丰富的物理编码层特性,如8b/10b编码等;PMA部分为模拟电路,提供高性能的串行接口特性,如预加重与均衡。...

Rapid IO协议由于无主机,且各设备之间可以并行交换信息,所以广泛应用于对交换速率要求高,且交互复杂的应用中。Xilinx现在有支持Serial RapidIO Gen2的核,可以应用在此场景中,但Xilinx 的 Rapid IO 核对外接口仅有 AXI 流接口 , 且对各类数据流的处理需要外...

两个FIX_32_30相乘得到的数据是 FIX_64_60,我们发现这个结果最大值为-1~+1,所以只需要保留两位整数位即可(其中一位为符号位)即通过截位使其变成FIX_32_30,所以 temp 为 sin*cos [61:20]。...

EXOSTIV Probe从各方面都优于传统调试方案,它支持Xilinx所有系列,采用高速SerDes接口实现数据采集和通信,EXOSTIV Probe能够采集多达32768个内部信号节点,此外EXOSTIV IP提供动态多路复用控制功能,能够动态采集更多的数据集而不需要重新进行编译。...

本文试图搞清楚在 Xilinx 基于 ARM 的 Zynq-7000、Zynq UltraScale+ MPSoC 和 Zynq UltraScale+ RFSoC 器件中是否存在任何漏洞。...

信号处理系统一般不单单是模拟信号或者数字信号,一般两者都会有。信号的处理关注的是信号以及信号所包含的信息的表示、变换及运算。...

由于OFDM接收机中大多是数据串并转换后的连续低速并行数据流输入FFT,故这里采用流水线结构。之后根据OFDM子载波数选择变换长度。该IP核仅支持50MHZ采样率数据的流水线处理,如果数高速通信场合,可以再次将数据串并转换用多个FFT IP核并行运算,也就是FPGA设计中常用的“面积换速度”。...

很多初学者入门FPGA的时候所学习的编程例子都是很简单的,比如流水灯、数码管点亮之类的。这种入门级别的例子有个特点,代码量少,逻辑简单,分析容易。而且大家刚开始都是照着书本抄一遍的,基本上都是没有什么问题的。一上板子就发现效果出来了。...

IP核的全称是: AXI4-STREAM FIFO 设置注意事项:一定要选择异步时钟,也就是双时钟,如下: 关于其他配置: TLAST 一般要选择的,作为边界界定。其他可以不选。深度不必太深,因为只起到穿越时钟区域的作用。...

之前用serdes一直都是跑的比较低速的应用,3.125Gbps,按照官方文档一步一步来都没出过什么问题,这次想验证一下K7系列GTX最高线速8Gbps,看看xilinx的FPGA是不是如官方文档所说。...

基于SRL16的分布式RAM不再支持V5、S6和V6等器件,但是SRL16是所有XIlinx器件都支持的,并且在设计中应用非常频繁,因此可通过调用原语的方法来调用SRL16E甚至SRL32E来实现原来ISE分布式RAM IP核的设计。...

双口RAM概述 双口RAM(dual port RAM)在异构系统中应用广泛,通过双口RAM,不同硬件架构的芯片可以实现数据的交互,从而实现通信。...

很多数字传感器、数字控制的芯片(DDS、串行ADC、串行DAC)都是通过IIC总线来和控制器通信的。不过IIC协议仍然是一种慢速的通信方式,标准IIC速率为100kbit/s,快速模式速率为400kbit/s。本文致力于讲述如何用计数器控制和分频时钟控制两种方式完成IIC的读写操作。 IIC协议 ...

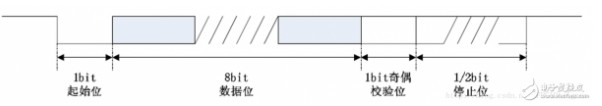

UART通信的一帧一般由11到12位数据组成。1bit的起始位,检测为低电平表示数据开始传输;紧接着8bits的数据;然后是1bit的奇偶校验位,可以是奇校验或者偶校验;最后是1bit或2bits的停止位,必须为高电平,表示一个字符数据的传输结束。...

博世力士乐在他的伺服驱动器IndraDrive上扩展了轨迹运动控制功能模块 “SMC for IndraDrive”。这意味着,现在博世力士乐的多轴系统在编程与调试环节所需要的时间大大减少了。作为一种可选的PLC编程方法,力士乐解决方案SMC使得轴耦合,轴同步和顺序化运动序列的实现速度更快。这套控制...

除了要有编程环境外,就需要有工程范例。其实工程范例很容易获得,我们可以找任意一本描述电动机控制的书籍,把其中所有的各种控制电动机的方式,当然是用继电器和接触器构成的,我们把这些机电控制方式全部编写成PLC控制方式。几个范例编完,基本上就明白了。...

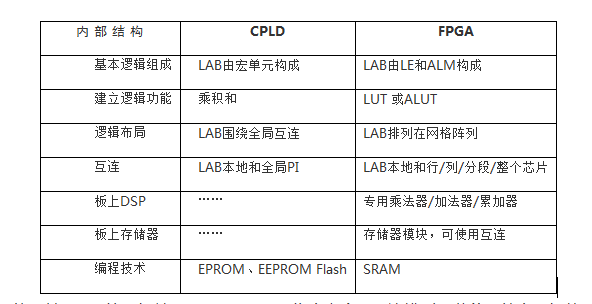

PLD和FPGA都是由逻辑阵列模块构成的,但是CPLD LAB基于乘积和宏单元,而FPGA LAB使用基于LUT的逻辑单元。CPLD LAB围绕中心全局互连排列,随着器件中逻辑数量的增加,呈指数增长。...

除了LAB,CPLD中的其他结构与PAL和PLD相似,但配置更高级。LAB之间的互连被称为可编程互连阵列,即PI或者PIA。PI与PAL和PLD中的可编程阵列相似,使用了相同的编程技术。而PI提供了LAB之间以及LAB和I/O引脚之间数据传送需要的所有走线。...