【ZYNQ Ultrascale+ MPSOC FPGA教程】第十九章 Hello World(下)

本章从FPGA工程师和软件工程师两者角度出发,介绍了ZYNQ开发的经典流程,FPGA工程师的主要工作....

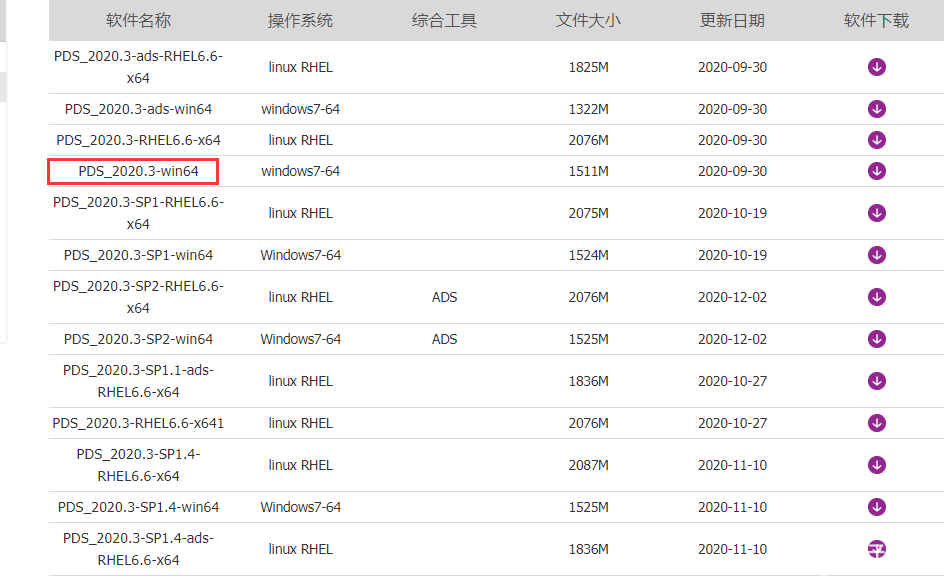

【紫光同创国产FPGA教程 第一章】Pango Design Suite 2020.3安装

ango Design Suite是深圳市紫光同创电子有限公司的FPGA开发软件,截止到目前,软件的....

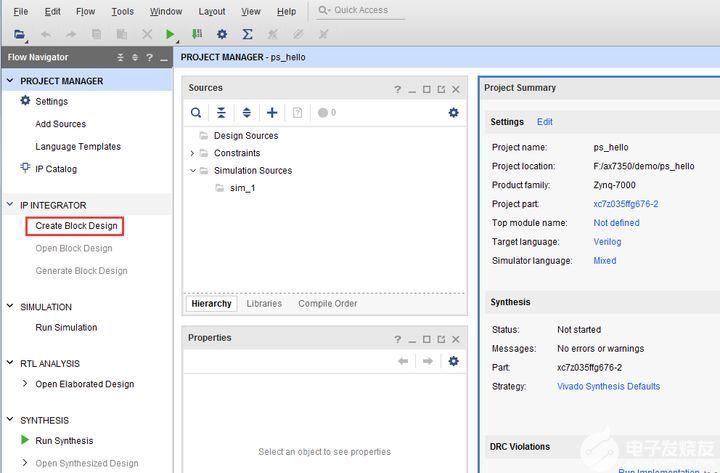

【ZYNQ Ultrascale+ MPSOC FPGA教程】第十八章 Hello World(上)

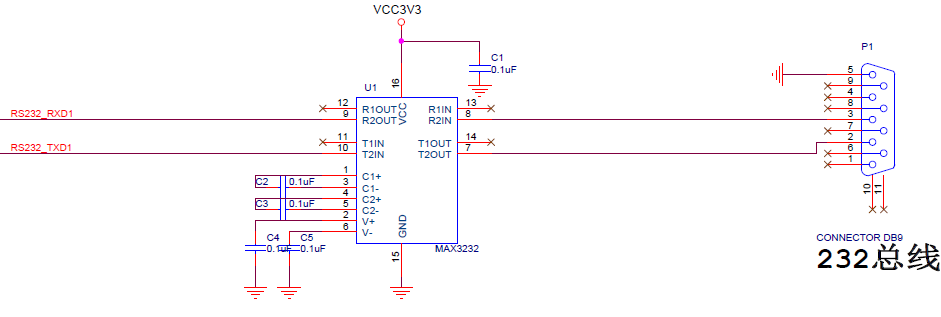

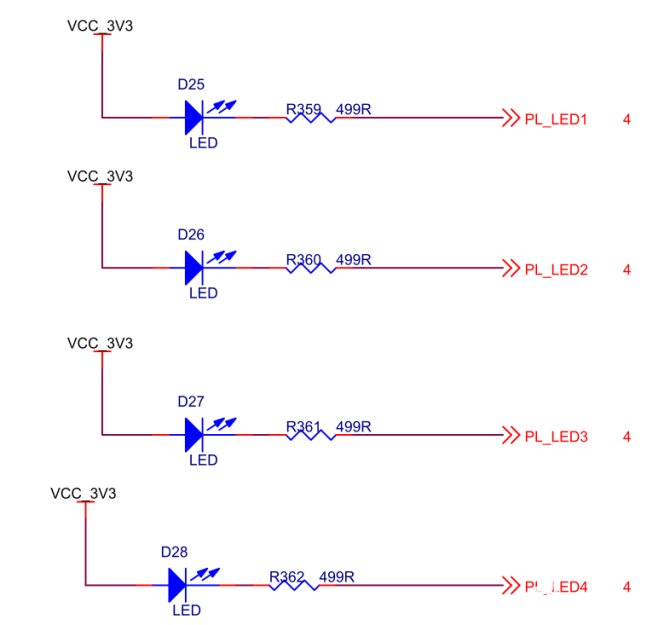

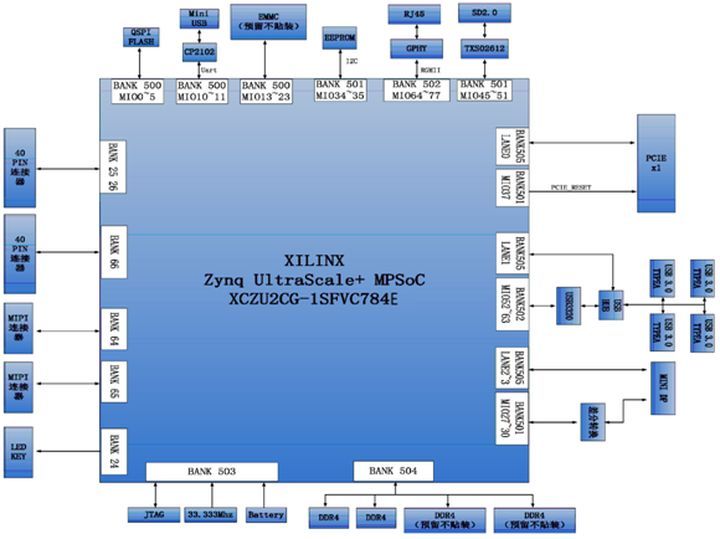

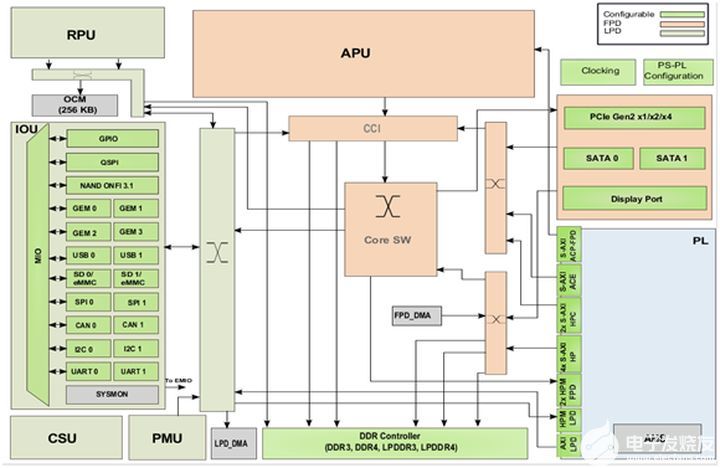

我们从原理图中可以看到ZYNQ芯片分为PL和PS,PS端的IO分配相对是固定的,不能任意分配,而且不....

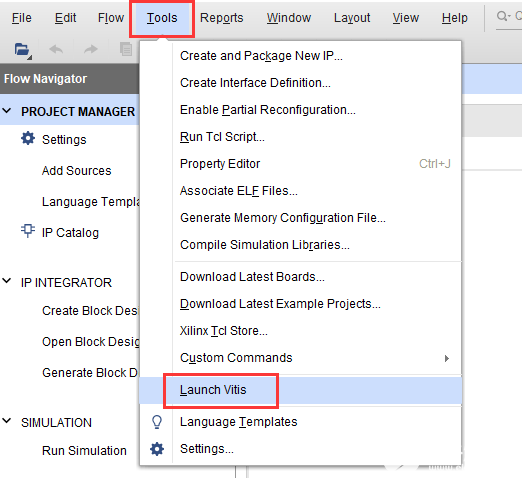

【ZYNQ Ultrascale+ MPSOC FPGA教程】第十七章Vitis准备工程及注意事项

所有的工程目录下都有个bootimage文件夹,存放了对应的BOOT.bin文件,可将此文件拷贝到V....

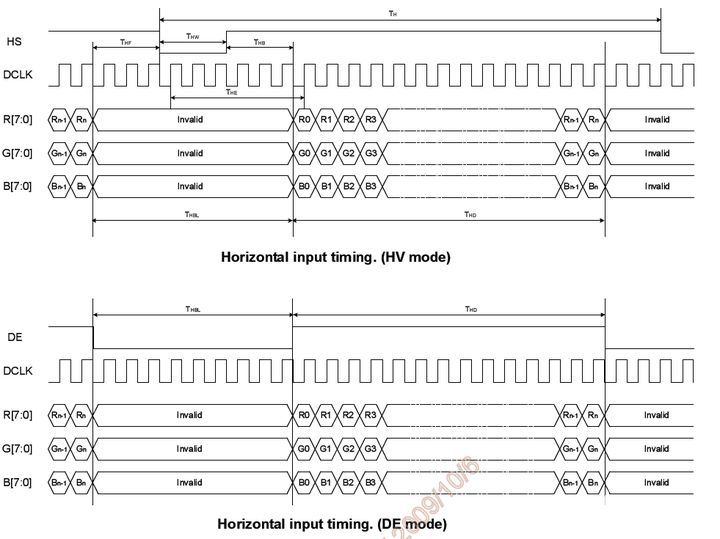

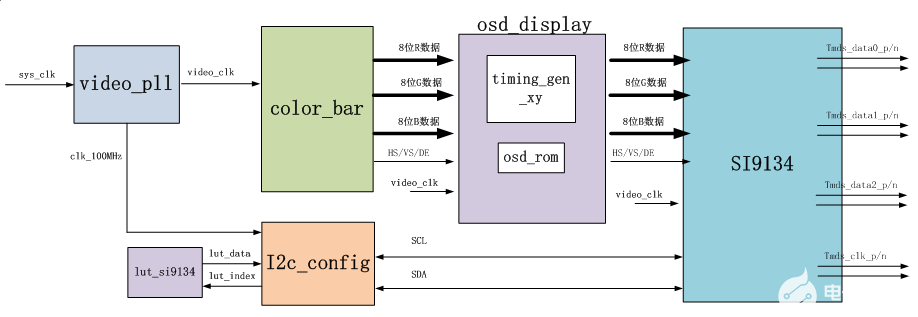

【ZYNQ Ultrascale+ MPSOC FPGA教程】第十五章HDMI字符显示实验

在HDMI输出实验中讲解了HDMI显示原理和显示方式,本实验介绍如何使用FPGA实现字符显示,通过这....

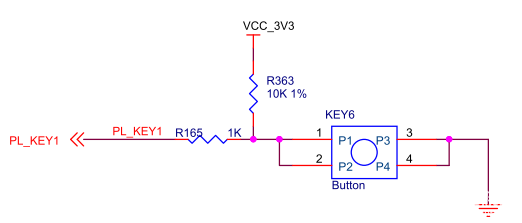

【ZYNQ Ultrascale+ MPSOC FPGA教程】第九章Vivado下按键实验

按键是FPGA设计当中最常用也是最简单的外设,本章通过按键检测实验,检测开发板的按键功能是否正常,并....

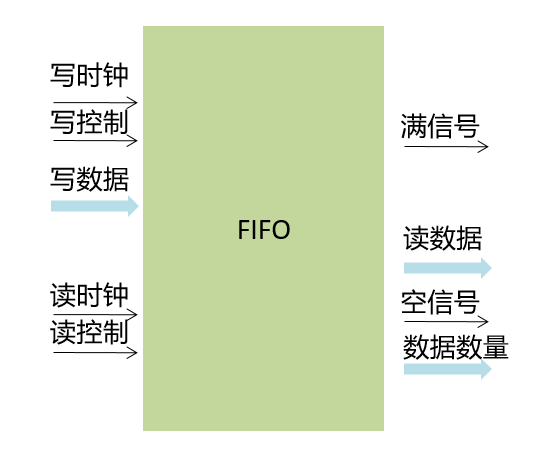

【ZYNQ Ultrascale+ MPSOC FPGA教程】第八章FPGA片内FIFO读写测试实验

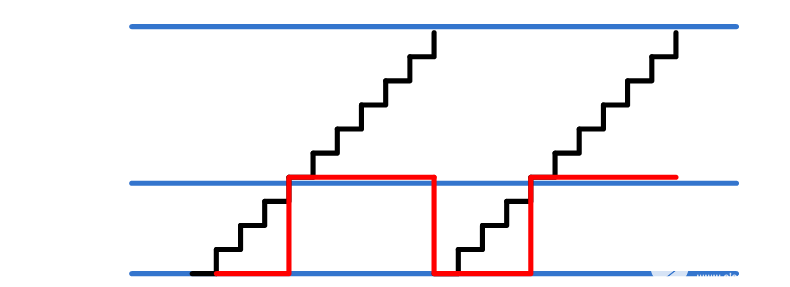

FIFO: First in, First out代表先进的数据先出,后进的数据后出。Xilinx在....

【ZYNQ Ultrascale+ MPSOC FPGA教程】第七章FPGA片内ROM测试实验

既然是ROM,那么我们就必须提前给它准备好数据,然后在FPGA实际运行时,我们直接读取这些ROM中预....

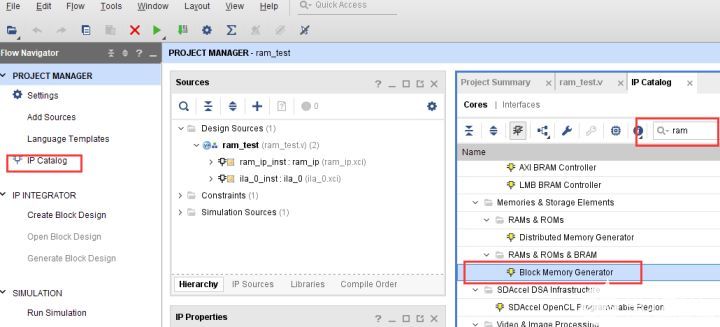

【ZYNQ Ultrascale+ MPSOC FPGA教程】第六章FPGA片内RAM读写测试实验

RAM是FPGA中常用的基础模块,可广泛用于缓存数据的情况,同样它也是ROM,FIFO的基础。本实验....

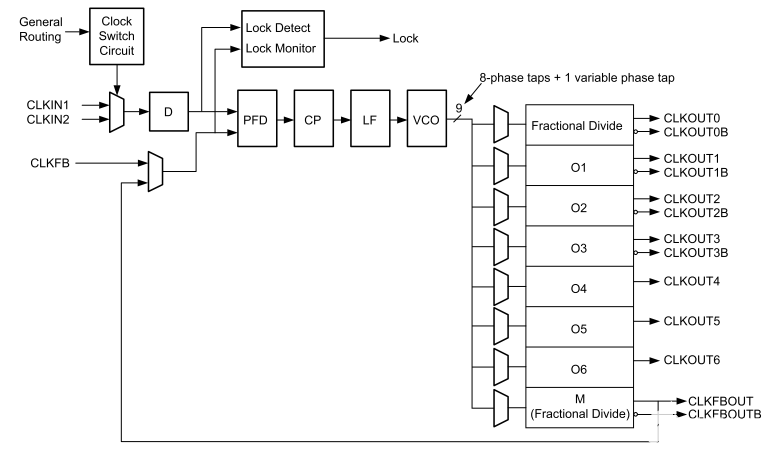

【ZYNQ Ultrascale+ MPSOC FPGA教程】第五章Vivado下PLL实验

PLL(phase-locked loop),即锁相环。是FPGA中的重要资源。由于一个复杂的FPG....

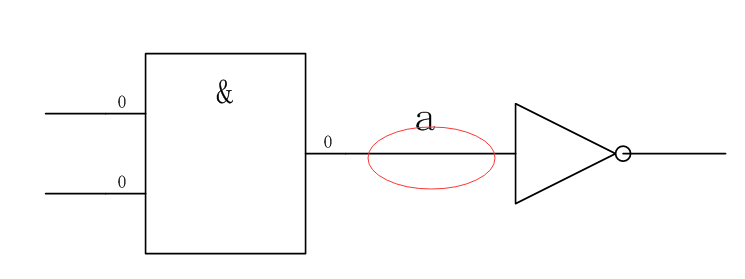

【ZYNQ Ultrascale+ MPSOC FPGA教程】第三章Verilog基础模块介绍

Wire 类型变量,也叫网络类型变量,用于结构实体之间的物理连接,如门与门之间,不能储存值,用连续赋....