verilog中函数和任务对比

verilog中函数和任务对比

在verilog中,函数和任务均用来描述共同的代码段,并且在模式内任意位置被调用,提高代码效率,让代....

数字电路常见逻辑符号

1、与门 (AND) 有两路输入信号一路输出信号,当且仅当两个输入信号均为高电平时,输出信号为高电平....

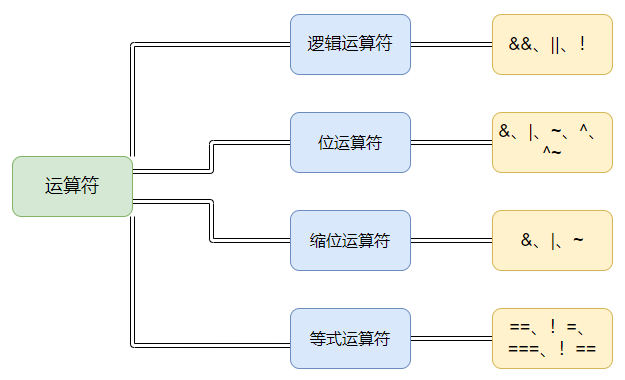

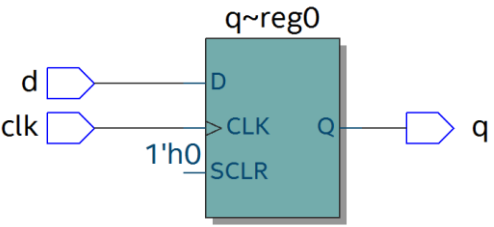

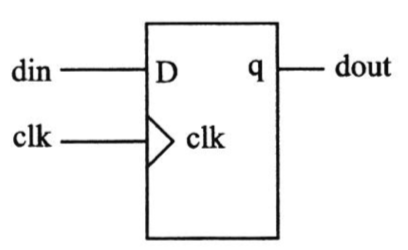

verilog可综合的语法子集

verilog可综合的语法子集

可综合的语法是指硬件能够实现的一些语法,这些语法能够被EDA工具支持,能够通过编译最终生成用于烧录到....

三极管四种工作状态对比

三极管四种工作状态对比

三极管根据发射结和集电结的偏置状态可以将工作区域分为四个,分别为截止区、放大区、饱和区、反向放大区。....