两个好习惯提高FPGA开发效率

假如我们不明确这一点,当改好代码,增加完的新的feature,跑 testbench 发现仿真失败了....

Xilinx RAM地址冲突

对于DRAM,写数据是 synchronous write,需要一个时钟周期, 读数据是 async....

Xilinx Vivado LOCK_PINS属性介绍

LOCK_PINS 是 Xilinx Vivado 做物理约束的属性之一。用来将LUT的逻辑输入(I....

为什么setup检查下一个沿而hold检查当前沿

做数字电路设计的可能都见过图一所示的setup和hold时间检查,从图中可以明显看出,setup t....

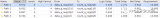

LUTRAM 读写使用不同时钟的CDC Path

当 LUTRAM 读写使用不同的时钟,写时钟 wclk_a,读时钟 rclk_b。