完善资料让更多小伙伴认识你,还能领取20积分哦,立即完善>

电子发烧友网技术文库为您提供最新技术文章,最实用的电子技术文章,是您了解电子技术动态的最佳平台。

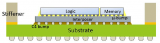

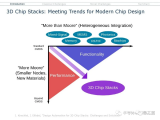

将大型SoC分解为较小的小芯片,与单颗裸晶相比具有更高的良率和更低的成本。Chiplet使设计人员可以充分利用各种IP,而不用考虑采用何种工艺节点,以及采用何种技术制造。他们可以采用多种材料,包括硅、玻璃和层压板来制造芯片。...

干法蚀刻(dry etch)工艺通常由四个基本状态构成:蚀刻前(before etch),部分蚀刻(partial etch),蚀刻到位(just etch),过度蚀刻(over etch),主要表征有蚀刻速率,选择比,关键尺寸,均匀性,终点探测。...

多个垂直堆叠的活动层(模具)较短的垂直互连:功耗、延迟、带宽..分离的和小的模具:异构集成,产量,成本,尺寸山复杂设计、设计自动化和制造过程...

超声清洗有时也被称作“无刷擦洗”,特点是速度快、质量高、易于实现自动化。它特别适用于清洗表面形状复杂的工件,如对于精密工件上的空穴、狭缝、凹槽、微孔及暗洞等处。...

1.Metal bump 金属凸块-C4 process(IBM) 2. Tape-Automated bonding 卷带接合-ACF process 3. Anisotropic conductive adhesives...

长期以来,个人计算机都可以选择增加内存,以便提高处理超大应用和大数据量工作的速度。由于3D芯片堆叠的出现,CPU芯粒也有了这个选择,但如果你想打造一台更具魅力的计算机,那么订购一款有超大缓存的处理器可能是正确的选择。...

当n型半导体与p型半导体接触时,电子与空穴都从浓度高处向浓度低处扩散,称为扩散运动。当电子进入p型区域,空穴进入n型区域后,即与对方多子复合,留下了固定不动的原子核。...

Dual in-line package (DIP) 双列直插封装:这种封装类型是最早的一种封装形式,芯片引脚排列成两行,可以直接插入插座或者焊接到电路板上。...

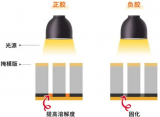

黄光的波长远离UV范围,因此不会引起光刻胶的意外曝光。黄光灯通常不含有紫外线,从而保护光敏材料免受不必要的曝光。...

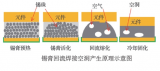

PCBA电子产品焊接导入无铅制程后,由于无铅焊料的特性,如熔点高、润湿性差、工艺窗口窄等,焊接过程出现了无铅焊接特有的缺陷及不良,如锡珠、焊点粗糙、漏焊和少锡,以及空洞等。...

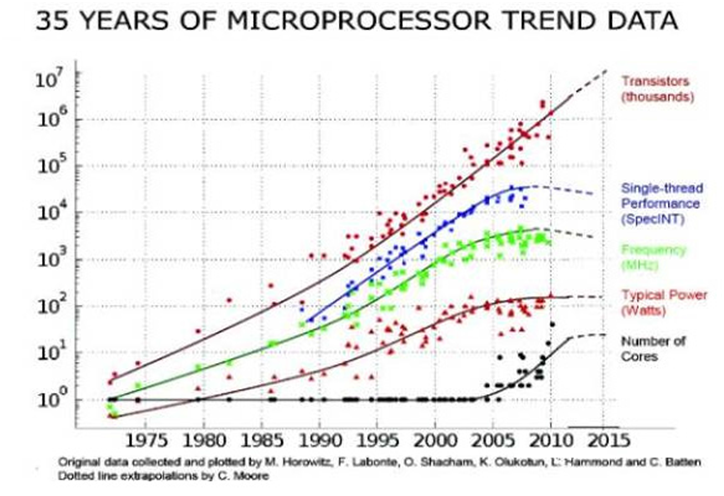

在摩尔定律的指导下,集成电路的制造工艺一直在往前演进。得意于这几年智能手机的流行,大家对节点了解甚多。例如40 nm、28 nm、20 nm、16 nm 等等,要知道的这些节点的真正含义,首先要解析一下技术节点的意思。...

BGA (Ball Grid Array)即“焊球阵列”,是在器件基板的下面按阵列方式引出球形引脚,在基板_上面装配LSI ( large Scale IntegratedCircuit)大规模集成电路芯片。它的出现解决了QFP等用周边弓|脚封装而长期难以解决的高I/O引脚数实现大规模集成电路芯...

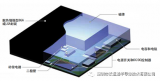

系统级封装 (System in Package) 简称SiP,SiP技术已成为现代电子领域的一项重要创新。SiP 技术使用半导体来创建包含多个 IC 和无源元件的集成封装,从而创建紧凑且高性能的产品。具体来说处理芯片、存储芯片、被动元件、连接器、天线等不同功能的器件,被封装在同一基板上,完成键合和...

3M Liqui-Cel膜接触器产品已经广泛的应用于各Fab厂超纯水溶解气体控制应用,有超过40年成功应用历史,其稳定的性能和超长的寿命赢得了业主和合作伙伴的一致认可。...

SMT加工的贴片机识别或雷射镜头受到污染、有杂物干扰识别、光源选择不当和强度、灰度不够等原因或识别系统损坏。...

1.Metal bump 金属凸块-C4 process(IBM) 2. Tape-Automated bonding 卷带接合-ACF process 3. Anisotropic conductive adhesives 异方向性导电胶 -ACP process 4.Polymer bu...

光刻胶作为影响光刻效果核心要素之一,是电子产业的关键材料。光刻胶由溶剂、光引发剂和成膜树脂三种主要成分组成,是一种具有光化学敏感性的混合液体。其利用光化学反应,经曝光、显影等光刻工艺,将所需要的微细图形从掩模版转移到待加工基片上,是用于微细加工技术的关键性电子化学品。...

打破IC发展限制,向高密度封装时代迈进。集成电路封装是指将制备合格芯片、元件等装配到载体上,采用适当连接技术形成电气连接,安装外壳,构成有效组件的整个过程,封装主要起着安放、固定、密封、保护芯片,以及确保电路性能和热性能等作用。...

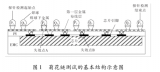

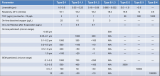

基于可靠性试验所用的菊花链测试结构,对所设计的扇出型封装结构进行了完整的菊花链芯片制造及后道组装工艺制造,并对不同批次、不同工艺参数条件下的封装样品进行电学测试表征、可靠性测试和失效样品分析。...

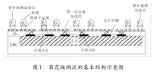

本文主要设计了用于封装可靠性测试的菊花链结构,研究了基于扇出型封装结构的芯片失效位置定位方法,针对芯片偏移、RDL 分层两个主要失效问题进行了相应的工艺改善。经过可靠性试验对封装的工艺进行了验证,通过菊花链的通断测试和阻值变化,对失效位置定位进行了相应的失效分析。...