完善资料让更多小伙伴认识你,还能领取20积分哦,立即完善>

电子发烧友网技术文库为您提供最新技术文章,最实用的电子技术文章,是您了解电子技术动态的最佳平台。

对设计者很通常的情况是花费几天或几周的时间围绕一个设计来满足时序,甚至多半利用上面描述的自动种子变化,只面对可以起伏通过已有布局的小改变和时序特性完全改变。...

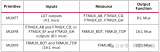

我们都知道,在7系列的FPGA中,每个CLB有两个Slice;而在UltraScale系列中,每个CLB中只有一个Slice,Slice又分成了两种类型SliceL(Logic)和SliceM(Memory),其中SliceM中的LUT可以当作分布式RAM来使用。...

在技术支持和维修方面,BYO通常缺乏立即可用的专业技术支持。这种情况通常需要依靠内部团队的知识和技能,有时甚至需要寻求外部的咨询服务,这可能导致问题解决的时间延长。...

所有代码在典型的 FPGA 和主流 FPGA 供应商中都具有高度可重用性。 可以出于任何目的对文件进行重新混合、转换和构建,甚至是商业用途。...

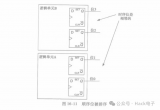

寄存器排序是布局工具把多位寄存器的相邻位分组放进单个逻辑元件所利用的方法。大多数基于单元的逻辑元件有不止一个触发器,因此,相邻位放置在一起,时序可以被优化。...

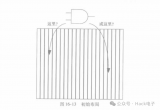

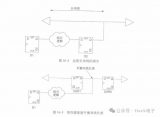

根据数据流的关系,我们可以采用单路径延迟反馈(Single-pathDelay Feedback, SDF)运算单元流水结构,SDF单元如下图所示。...

本项目主要在FPGA上实现了一个经典小游戏“俄罗斯方块”。本项目基本解决方案是,使用Xilinx Zynq系列开发板 ZedBoard 作为平台,实现主控模块,通过VGA接口来控制屏幕进行显示。...

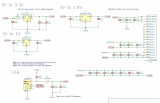

FPGAs需要多种不同的电压。在这个设计中,将I/O引脚的工作电压设置为3.3V(因为这对于业余爱好者来说比较标准),但还需要提供5V、1.8V和1.0V的电压。这意味着需要处理4种不同的电压!...

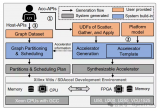

ThunderGP是基于HLS的开源通用图形处理框架,支持Vitis和SDAccel开发环境,适用于U50、U200、U250和VCU1525等Xilinx Alveo平台(官方开发板)。...

自上而下的设计是把系统模块作为基本单元,然后再逐一分解,一直这样分解下去,直到无法进一步分解,可以用EDA元件库中的元件来实现为止。...

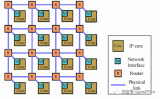

交换机根据所选拓扑采用在网络节点之间路由信号的任务。请注意,NoC 的架构假设使用了一个相当强大的开关,这将提供最低水平的延迟(最多纳秒)。...

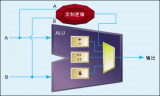

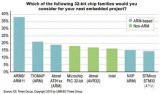

精简指令集计算(RISC)架构的目标之一即是保持指令简单化,以便让指令运行得足够快。这与复杂指令集计算(CISC)架构正好相反,后者一般不会同样快地执行指令,但每个指令可完成更多处理任务。...

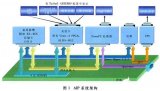

基于FPGA的单芯片实现方法具有低成本和快速面市等优点,是多芯片和ASICSoC非常有吸引力的替代方案...

转换的依据是一个简单的运算关系:“补码的整数值”+“原码绝对值的整数值”=2^B,B为位宽。比如带符号数原码1110的补码为1010:1110取绝对值0110为6;1010为10,二者加起来为2^4=16。...

AIP架构的最新应用是猎户座载人太空船的视觉处理单元(VPU)。VPU可为处理影像算法提供可重构的平台,有利于位姿估计、光学导航以及压缩/ 解压缩。...

FPGA软件包含进行设计而产生的程序、文档和数据,同时包含与之相关的软件特性和硬件特性。FPGA软件测试需要考虑软件代码正确性、软硬件接口协调性、时序性等方面的全面覆盖。...

片内PLL设计是IC设计中的一个重要环节,在无线通信、高频通信和数字通信等领域PLL的使用占据重要地位。本文以Cyclone IV系列EP4CE15F17C8N型FPGA为研究对象,其包含四个通用的PLL,分别位于芯片的四个边角,采用独立的2.5V电压供电。...

ASIC中你可以直接加宽金属线,比如两倍宽度走时钟线,复位线啦,之类的。金属线宽度变大,线上的延迟变小,对速度也是有帮助的。...