完善资料让更多小伙伴认识你,还能领取20积分哦,立即完善>

电子发烧友网技术文库为您提供最新技术文章,最实用的电子技术文章,是您了解电子技术动态的最佳平台。

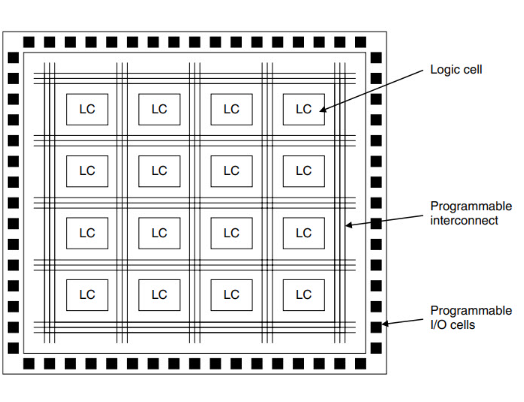

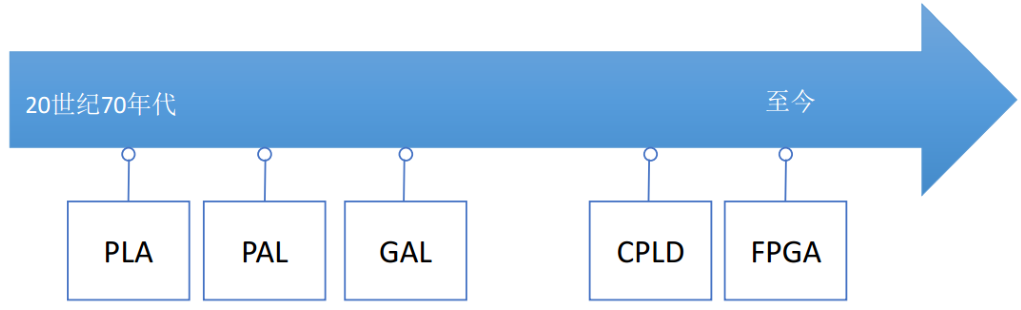

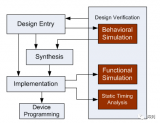

可编程逻辑器件包含多个逻辑元件,例如触发器以及可由用户配置的AND和OR门,用户可以在使用专用软件应用程序完成的编程过程中修改内部逻辑和连接。...

FPGA 在通信领域的应用可以说是无所不能,得益于 FPGA 内部结构的特点,它可以很容易地实现分布式的算法结构,这一点对于实现无线通信中的高速数字信号处理十分有利。...

时钟设计方案 在复杂的FPGA设计中,设计时钟方案是一项具有挑战性的任务。设计者需要很好地掌握目标器件所能提供的时钟资源及它们的限制,需要了解不同设计技术之间的权衡,并且需要很好地掌握一系列设计实践知识。不正确的设计或次优的时钟方案可能会导致在最好情况下较差的设计性能,或者在最坏情况下的随机和难...

对于最后一种情况,也就是位于中间白色区域的点,他需要进行双线性插值。可以看到整个点位于第四个block,所以他需要在第一个,第二个,第四个和第五个block上分别计算直方图均衡化的结果,和相应的权重。...

可编程AES加解密IP内建密钥扩展功能,使用初始密钥产生扩展密钥,用于加解密过程。可编程AES加解密IP处理128-bit分组数据,并且支持可编程的密钥长度:128-bit,192-bit和256-bit。...

对于数字设计人员来讲,只要信号从一个时钟域跨越到另一个时钟域,那么就可能发生亚稳态。我们称为“跨时钟域”即“Clock Domain Crossing”,或CDC。...

CPU、GPU遵循的是冯·诺依曼体系结构,指令要经过存储、译码、执行等步骤,共享内存在使用时,要经历仲裁和缓存。 而FPGA和ASIC并不是冯·诺依曼架构(是哈佛架构)。以FPGA为例,它本质上是无指令、无需共享内存的体系结构。...

模拟有数十亿个晶体管的现代SoC相当耗费资源,依芯片大小和复杂性,可能需要跨越多个机架、数十甚至数百个FPGA。...

FPGA 是一种伪通用计算加速器,与 GPGPU(通用 GPU)类似,FPGA 可以很好地卸载特定类型的计算。从编程角度上讲,FPGA 比 CPU 更难,但从工作负载角度上讲 FPGA 是值得的:和 CPU 基线相比,好的 FPGA 实现可以提供数量级的性能和能量优势。...

Nitro DPU系统提供了密钥、网络、安全、服务器和监控等功能支持,释放了底层服务资源供客户的虚拟机使用,并且NitroDPU使AWS可以提供更多的裸金属实例类型,甚至将特定实例的网络性能提升到100Gbps。...

据我了解,目前国内很多大学是没有开设FPGA相关课程的,所以很多同学都是自学,但是自学需要一定的目标和项目,今天我们就去看看常春藤盟校Cornell University 康奈尔大学开设的FPGA项目课程。...

并行处理是最普遍的,也是AI加速器的基础。它可以通过许多阵列的小型专用处理内核(如特定算法的GPU)来实现,或者以数据流(即专用处理器的流水线)的方式来实现。...

接下来我们下载两块开发板的测试程序,先在5CEFA7F23的下载器内添加比特流文件,输入翻转率50%比特流文件并且加载。...

这里,我们基于多个互相同步的XCZU29DR FPGA板开发了一个可扩展系统,每个单板拥有16个6.554GS/s的DAC通道和16个2.058GS/s的ADC通道,工作时无需模拟I/Q混频器。...

从这个例子可以看到,如果一个信号被自动移除了,应当首先应当考虑它是否没有在别处被用到。不过,在下一个例子里马上可以看到这并不是信号被优化掉的唯一的原因。...

Verilog HDL是一种硬件描述语言,以文本形式来描述数字系统硬件的结构和行为的语言,用它可以表示逻辑电路图、逻辑表达式,还可以表示数字逻辑系统所完成的逻辑功能。...

DR3和RAM一样,是一个存储器件,它的每个内部单元都存储了当前的数据状态值。 但DDR3和RAM本身,是没有“空”、“存有数据”,“数据满”等概念的。只要给地址,它就会把当前地址的数据给到总线上,而且这个地址可以读很多次。...

Xilinx Vivado工具的配置约束隐藏得比较深,如图1所示,在进入配置页面前,首先需要点击PROGRAM AND DEBUG->Generate Bitstream执行工程的全编译,然后点击IMPLEMENTATION->OpenImplemented Design进入实现页面。...

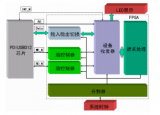

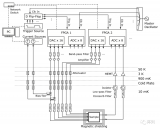

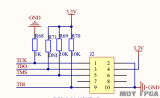

由于 PDIUSBD12 在读写时序上有时间限制,例如每次读写操作之间的间隔不能小于 500ns,而 FPGA 的系统时钟一般频率都比较高,所以不能直接使用系统时钟控制 PDIUSBD12,必须进行分频。分频器模块的功能就是按照要求由系统时钟生成所需频率的时钟信号。...