完善资料让更多小伙伴认识你,还能领取20积分哦,立即完善>

电子发烧友网技术文库为您提供最新技术文章,最实用的电子技术文章,是您了解电子技术动态的最佳平台。

接口选择 Internal ,因为该IP核通过GMII接口与“1G/2.5G Ethernet PCS/PMA or SGMII”通信,不需要产生外部物理接口...

Achronix的Speedster7t支持PCIe Gen5和112G Serdes,而AMD的高端系列Virtex Ultrascale+也仅仅支持到PCIe Gen4,也只在最高端的FPGA中支持到58Gb的GTM,大多数Virtex Ultrascale+仅仅支持32.75Gb的GTY。...

AMD 已经拥有 Zynq UltraScale+ 和 Artix UltraScale+ 系列,而 Spartan UltraScale+ FPGA 系列的推出使其不断现代化。...

CPU core:分为2种,软core和硬core.软core是用逻辑代码写的CPU模块,可以在任何资源足够的FPGA中实现,使用非常灵活。而且在大容量的FPGA中还可以集成多个软core,实现多核并行处理。...

双调排序(BitonicSort)是数据独立(Data-independent)的排序算法,即比较顺序与数据无关,特别适合并行执行。在了解双调排序算法之前,我们先来看看什么是双调序列。...

这是一款入门级别的软镜内窥镜,采OVM6946+OV426方案实现,其中镜头部分长度为1.5m,USB信号线部分为1.5m,合计约3米。...

FPGA软件包含进行设计而产生的程序、文档和数据,同时包含与之相关的软件特性和硬件特性。FPGA软件测试需要考虑软件代码正确性、软硬件接口协调性、时序性等方面的全面覆盖。...

HDL(VHSIC Hardware Description Language)是一种硬件描述语言,主要用于描述数字电路和系统的结构、行为和功能。它是一种用于硬件设计的标准化语言,能够帮助工程师们更好地描述和设计数字电路,并且广泛应用于FPGA和ASIC设计中。...

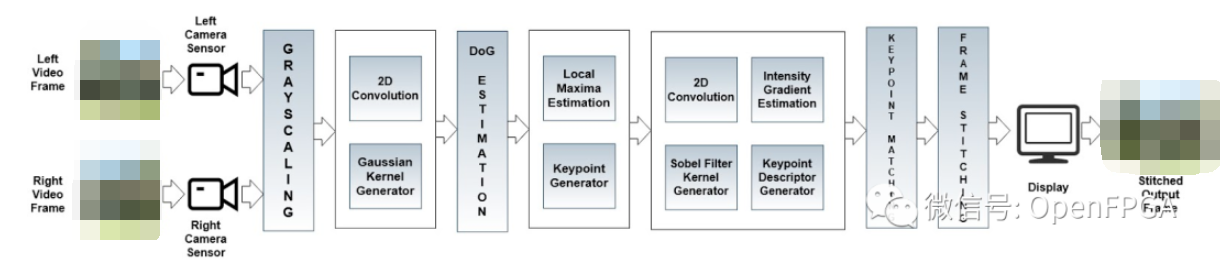

视频流的每个单独帧将具有对应于红色、绿色和蓝色的三个通道。视频帧中的颜色信息不会增强特征检测。此外,与单通道 8 位图像相比,3 通道 8 位图像的计算需要更多时间。...

就是看看超差的那个线路,增加一些中间寄存器,或者使用流水线技术,就是将组合逻辑和时序逻辑分开,大的时序逻辑,尽量优化成由很多小的时序逻辑组成一个大的时序逻辑。...

SRAM工艺的处理器是通过CMOS内部管道切换的方式工作,其产品处理速度较高,被众多用户接受。但是,CMOS工艺有一个致命缺陷,由于工艺原因,伴随CMOS工艺制成芯片产生米勒效应极其容易受到外界干扰,产生翻转。...

FPGA 在比特流被加载时计算 CRC 值,然后该值与在比特流加载结束时预期的 CRC 值进行比较。如果两个值匹配,则FPGA 成功加载。...

FPGA 和 GPU 最大的区别在于体系结构,FPGA 更适合做需要低延迟的流式处理,GPU 更适合做大批量同构数据的处理。...

采用单芯片的SoC形态,兼顾性能和功耗。FPGA-Based DPU在硬件设计上的挑战主要来自芯片面积和功耗。...

嵌入式工程师常见的情况是在硬件加速器(如FPGA)和主机CPU之间建立通信。这项工作因其繁琐和容易出错而臭名昭著。...

数据接口的同步在 FPGA/CPLD 设计中一个常见问题。很多设计工作不稳定都是源于数据接口的同步问题。...

为了加快实现 FPGA 构建环境的自动化(如用于持续集成 (CI)),并确保在开发与生命周期后期阶段完整重现设计结果,Missing Link Electronics 团队已整合出一套脚本。...

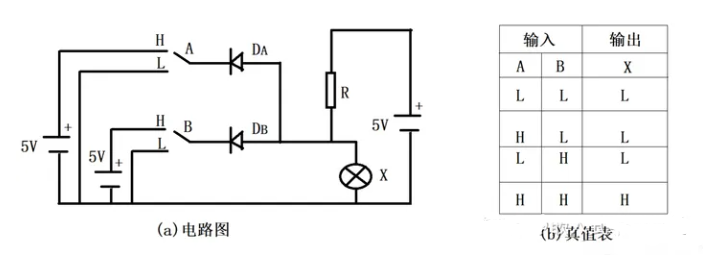

在这个串联电路中,如果两个开关都为开状态,则LED点亮;如果任何一个开关为关状态,则LED熄灭。基本逻辑电路也称作门电路,可以通过单个输入来固定输出,或反映输出。...