AMD MicroBlaze中通过AXI Timer获取时间戳

硬件的Vivado Block design设计中,添加AXI Timer

如何使用verilog参数和generate语句来编写可重用的verilog代码?

与大多数编程语言一样,我们应该尝试使尽可能多的代码可重用。这使我们能够减少未来项目的开发时间,因为我....

简谈FPGA引脚信号分配的几个原则

现在的FPGA正变得越来越复杂,向引脚分配信号的任务曾经很简单,现在也变得相当繁复。下面这些用于向多....

如何在verilog中使用If语句和case语句?

我们在上一篇文章中已经看到了如何使用程序块(例如 always 块来编写按顺序执行的 verilog....

Verilog中循环语句简介

在这篇文章中,我们讨论了可以在verilog中使用的不同类型的循环 - for循环,while循环,....

Vivado中常用TCL命令汇总

Vivado是Xilinx推出的可编程逻辑设备(FPGA)软件开发工具套件,提供了许多TCL命令来简....

CIC插值滤波器与直接频率合成器DDS的FPGA实现

CIC滤波器是无线通信中的常用模块,一般用于数字下变频(DDC)和数字上变频(DUC)系统。随着现代....

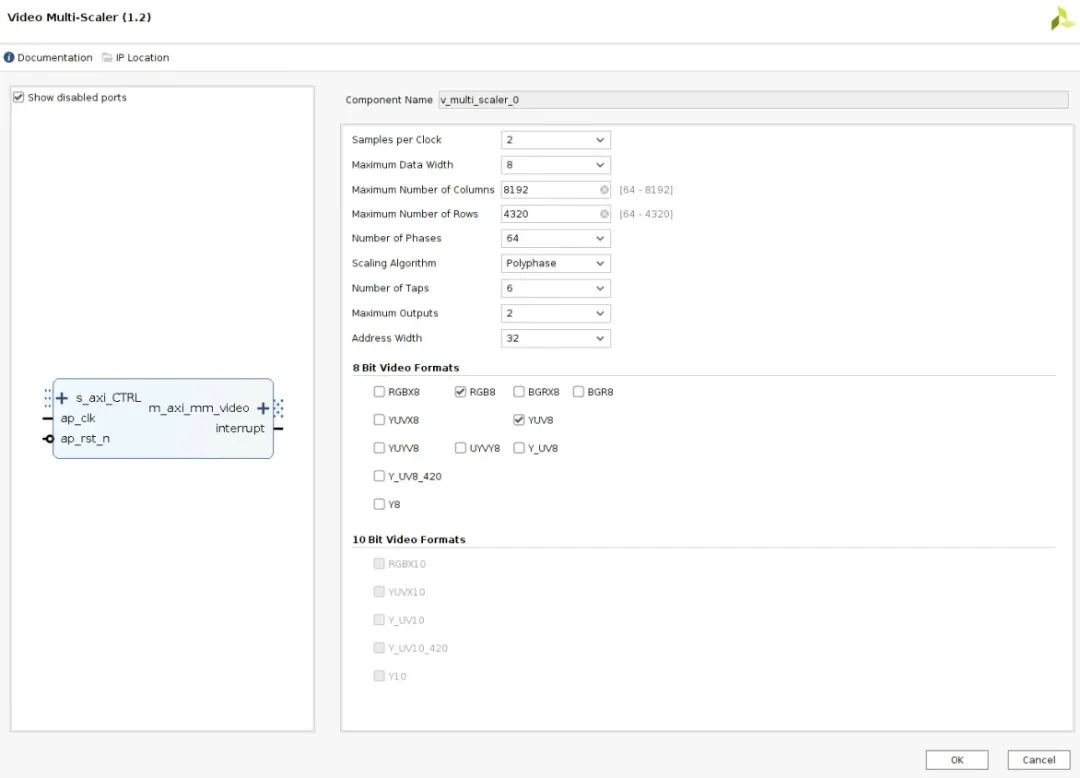

基于FPGA实现分离用软件的图像处理系统设计

灰度直方图统计直方图是图像的灰度分布统计的一种表示方法,统计目标图像中各个灰度点的像素个数,很多对于....

GPT-4 驱动的新Copilot编码助手

在经过一年的技术试验之后,Copilot 于去年夏季正式推出,能够为使用 GitHub 及受支持文本....

Vitis IDE Git集成快速入门指南

虽然“Platform”(平台)、“System Project”(系统工程)和“Applicati....

赛灵思的局部重配置技术(Partial Reconfiguration)

一般情况下,要重新配置一个FPGA需要使其处于复位状态,并通过外部控制器重新加载一个新设计到器件中。....

AXI VDMA IP 的高级用例

如果 STRIDE 等于 HSIZE,那么 AXI VDMA IP 会在没有任何跳转的情况下读取帧缓....

搜索引擎技术大战,始于昨日

“搜索引擎的技术大战,始于今日。我们会继续前进并加快步伐。更重要的是,我们希望能在搜索领域持续创新,....

国产FPGA!哪些公司比较牛?

为了满足经济发展和国防需求,打破美国的垄断,中国政府多年来投入了数百亿科研经费,通过逆向工程方式仿制....

实现高速收发器TX通道间相位对齐的方法

当TX Buffer被使能时,可以通过TXBUFSTATUS的Bit0(Half Full)的状态和....

平头哥宣布:RISC-V成功运行安卓12

美国、英国政府将限制处理器矽智财(IP)厂Arm在Neoverse V产品授权给中国厂商,由于Neo....

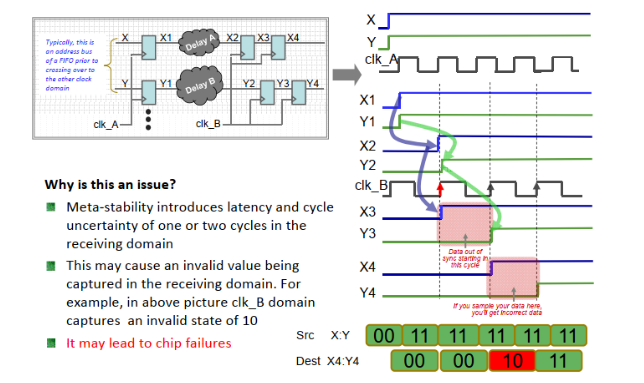

为什么回跳机制不起作用了呢?FPGA怎么挂死了呢

Xapp1247, Appendix A提供了一个很好的解决方案。利用两个timer或者称之为bar....