当FPGA开发者需要做RTL和C/C++联合仿真的时候,一些常用的方法包括使用MicroBlaze软....

![的头像]() Hack电子 发表于

Hack电子 发表于 12-13 10:11

•2534次阅读

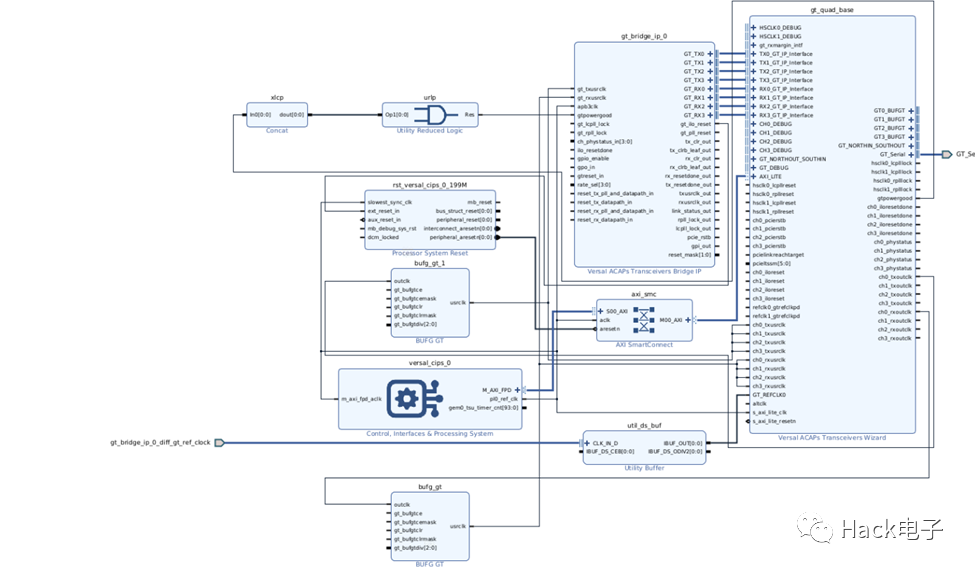

在debug GT的时候,有时候需要读出一些寄存器来分析。这篇文章介绍一种通过AXI4 Lite或者....

![的头像]() Hack电子 发表于

Hack电子 发表于 12-08 10:32

•911次阅读

编写代码容易,但编写优秀代码却是一项挑战。采纳基本编程原则是确保编写高质量代码的稳妥途径,无论软件项....

![的头像]() Hack电子 发表于

Hack电子 发表于 12-05 11:28

•1265次阅读

ILA Cross Triggering功能使得ILA核心之间、以及ILA核心与处理器(例如,AMD....

![的头像]() Hack电子 发表于

Hack电子 发表于 11-30 10:17

•1504次阅读

自 20 世纪 70 年代诞生以来,以太网已成为局域网事实上的标准。多年来,其经历了多项进步,以满足....

![的头像]() Hack电子 发表于

Hack电子 发表于 10-31 11:07

•1246次阅读

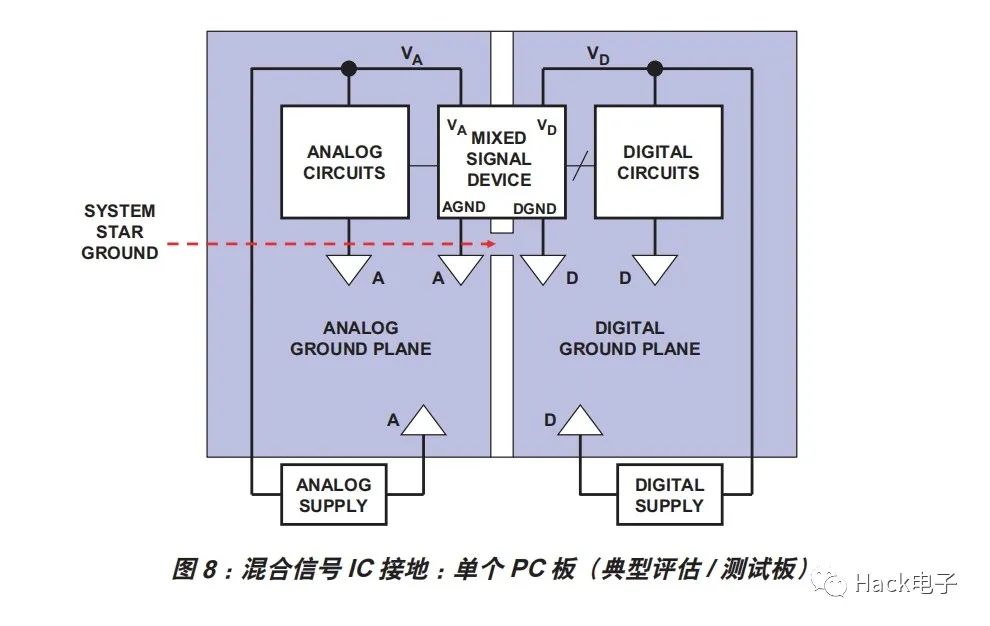

大多数 ADC、DAC 和其他混合信号器件数据手册是针对单个 PCB 讨论接地,通常是制造商自己的评....

![的头像]() Hack电子 发表于

Hack电子 发表于 10-20 14:37

•730次阅读

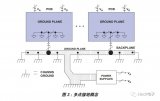

系统内的每个 PCB 至少应有完整的一层专用于接地层。理想情况下,双面电路板的一面应完全用于接地层,....

![的头像]() Hack电子 发表于

Hack电子 发表于 10-18 15:50

•963次阅读

目前的信号处理系统一般需要混合信号器件,例如模数转换器 (ADC)、数模转换器 (DAC)和快速数字....

![的头像]() Hack电子 发表于

Hack电子 发表于 10-17 15:55

•3534次阅读

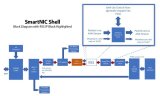

平均通信效率低。SoC中采用基于独占机制的总线架构,其各个功能模块只有在获得总线控制权后才能和系统中....

![的头像]() Hack电子 发表于

Hack电子 发表于 10-12 16:52

•3262次阅读

FIFO缓存是介于两个子系统之间的弹性存储器,其概念图如图1所示。它有两个控制信号,wr和rd,用于....

![的头像]() Hack电子 发表于

Hack电子 发表于 09-11 10:12

•924次阅读

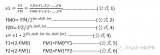

奇偶校验是一种简单、实现代价小的检错方式,常用在数据传输过程中。对于一组并行传输的数据(通常为8比特....

![的头像]() Hack电子 发表于

Hack电子 发表于 09-05 10:40

•3067次阅读

增量实现自从首次获得支持以来,不断升级演变,在此过程中已添加了多项针对性能和编译时间的增强功能。它解....

![的头像]() Hack电子 发表于

Hack电子 发表于 09-04 10:07

•996次阅读

做FFT后,我们发现这三个时域上有巨大差异的信号,频谱却非常一致。尤其是下边两个非平稳信号,我们从频....

![的头像]() Hack电子 发表于

Hack电子 发表于 08-28 17:01

•412次阅读

testbench是写输入激励的,是一种验证手段。

![的头像]() Hack电子 发表于

Hack电子 发表于 08-19 10:58

•783次阅读

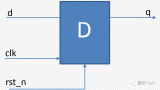

D触发器结构如下图所示,先有时钟上升沿,然后才有D的值赋给Q,没有上升沿Q值保持不变,时序逻辑在时钟....

![的头像]() Hack电子 发表于

Hack电子 发表于 08-18 10:23

•2199次阅读

相干就是信号相似的程度,下图最上方波形与下面三个的相关性,主要考察频率的相似性。

![的头像]() Hack电子 发表于

Hack电子 发表于 08-18 10:09

•2556次阅读

Verilog规范对于一个好的IC设计至关重要。

![的头像]() Hack电子 发表于

Hack电子 发表于 08-17 10:14

•1686次阅读

本篇博文旨在演示如何在 Zynq 设计中使用 Vitis 视觉库函数 (remap) 作为 HLS ....

![的头像]() Hack电子 发表于

Hack电子 发表于 08-01 10:18

•785次阅读

半导体LSI的EDA模型之一是"IBIS模型",完整称为Input/OutputBuffer Inf....

![的头像]() Hack电子 发表于

Hack电子 发表于 07-14 10:10

•2274次阅读

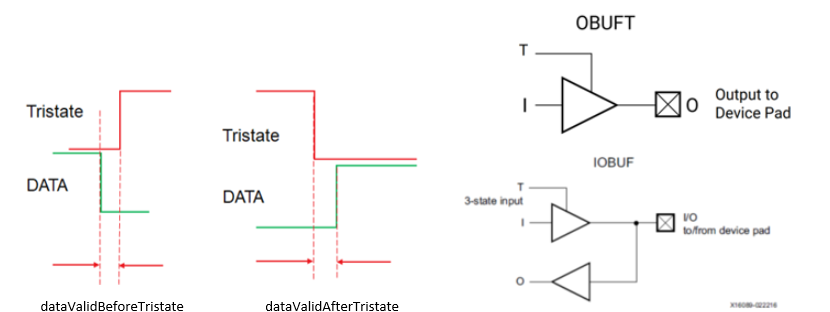

本文着重探讨 HDIO OBUFT 和 IOBUF 用例。如果含三态控制 (OBUFT/IOBUF)....

![的头像]() Hack电子 发表于

Hack电子 发表于 07-12 10:04

•1749次阅读

在HLS中用C语言实现8192点FFT,经过测试,实验结果正确,但是时序约束不到100M的时钟,应该....

![的头像]() Hack电子 发表于

Hack电子 发表于 07-11 10:05

•1240次阅读

笔者在校的科研任务,需要用FPGA搭建OFDM通信系统,而OFDM的核心即是IFFT和FFT运算,因....

![的头像]() Hack电子 发表于

Hack电子 发表于 07-10 10:43

•1518次阅读

FPGA实现除法的方法有几种,比如直接用/来进行除法运算,调用IP核进行除法运算,但这两种方式都有个....

![的头像]() Hack电子 发表于

Hack电子 发表于 07-04 10:03

•1511次阅读

AMD宣布计划在四年内投资高达 1.35 亿美元,在爱尔兰实现持续增长。

![的头像]() Hack电子 发表于

Hack电子 发表于 06-28 14:53

•489次阅读

它用TensorFlow.js加载了一个10层的预训练模型,相当于在你的浏览器上跑一个CNN模型,只....

![的头像]() Hack电子 发表于

Hack电子 发表于 06-28 14:47

•4184次阅读

大多数FPGA程序员认为,高级工具总是发出更大的比特流,作为提高生产率的 "代价"。但是这总是真的吗....

![的头像]() Hack电子 发表于

Hack电子 发表于 06-27 10:10

•753次阅读

在固化时,会遇到找不到flash器件的问题,这里稍微作个总结: (针对xinlinx的芯片)。

![的头像]() Hack电子 发表于

Hack电子 发表于 06-21 10:06

•6607次阅读

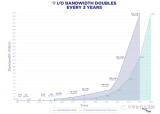

随着PCI Express 6.0 于去年初完成,PCI-SIG 迅速开始着手开发下一代 PCIe ....

![的头像]() Hack电子 发表于

Hack电子 发表于 06-19 15:24

•2135次阅读

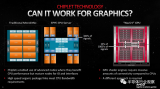

11月3日,AMD 透露了其 RDNA 3 GPU 架构和 Radeon RX 7900 系列显卡的....

![的头像]() Hack电子 发表于

Hack电子 发表于 06-12 10:14

•1526次阅读

Verilog模块之间的连接是通过模块端口进行的。 为了给组成设计的各个模块定义端口,我们必须对期望....

![的头像]() Hack电子 发表于

Hack电子 发表于 06-12 10:05

•1620次阅读