前言 当你器件的引脚贼少的时候,需要主机和从机通信,spi就派上了用场,它可以一对多,但只是片选到的....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 11-16 10:35

•344次阅读

摘要 经典滤波器的滤波思路是从频率域上将噪声滤掉,关键是设计相应的滤波器传递函数H(s)、H(z),....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 11-15 12:38

•1061次阅读

JTAG是一种IEEE标准用来解决板级问题,开发于上个世纪80年代。今天JTAG被用来烧录、debu....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 11-15 10:02

•272次阅读

什么叫滤波器? 简单的说,就像筛米,留下你需要的米,滤掉不需要的米头。过滤的功能。 什么叫数字滤波器....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 11-13 10:42

•334次阅读

① 利用电路的某种频率响应特性来测量频率,如谐振测频法[低频测量,应用较广]、电桥测频法[高频、微....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 11-12 11:41

•208次阅读

SDRAM是做嵌入式系统中,常用是的缓存数据的器件。基本概念如下(注意区分几个主要常见存储器之间的差....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 11-05 17:35

•345次阅读

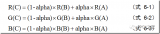

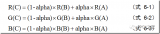

Alpha通道是一个8位的灰度通道,该通道用256级灰度来记录图像中的透明度信息,定义透明、不透明和....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 05-01 10:28

•673次阅读

一个视频序列是由N个帧组成的,采集图像的时候一般有2种扫描方式,一种是逐行扫描(progressiv....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 04-30 11:50

•3492次阅读

Verilog与VHDL语法是互通且相互对应的,如何查看二者对同一硬件结构的描述,可以借助EDA工具....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 04-28 17:47

•2406次阅读

传感器是任何工业系统,尤其是工业物联网解决方案的关键组成部分。从简单的温度测量热电偶,到结合多个异构....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 04-26 09:56

•701次阅读

2000年的时候,做设计基本都是使用Xilinx公司的Virtex和Virtex-E系列芯片。那时候....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 04-26 09:54

•713次阅读

芯片到芯片SERDES最初用于盒间通信。但是,因为它能出色地处理同一块电路板上的芯片间通信,因而在....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 04-11 11:11

•908次阅读

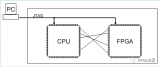

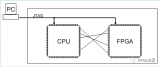

CPU是相通的,相信大部分的同学都学习过单片机,是有一定基础的。如果你碰到问题,去尝试了,自己把问题....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 03-13 09:38

•594次阅读

IP(Intelligent Property) 核是具有知识产权核的集成电路芯核总称,是经过反复验....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 03-07 09:35

•1240次阅读

SystemVerilog 接口的开发旨在让设计中层级之间的连接变得更加轻松容易。 您可以把这类接....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 03-04 15:25

•944次阅读

集成电路被誉为高端制造业的“皇冠明珠”,而在集成电路里,FPGA又被称为“万能芯片”,作为可定制的芯....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 01-23 10:46

•973次阅读

CPLD和FPGA都是由逻辑阵列模块构成的,但是CPLD的LAB基于乘积和宏单元,而FPGA的LAB....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 01-23 09:17

•1079次阅读

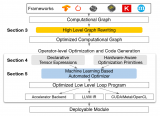

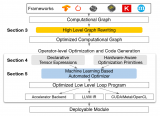

卷积占据了CNN网络中绝大部分运算,进行乘法运算通常都是使用FPGA中的DSP,这样算力就受到了器件....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 01-19 09:14

•1414次阅读

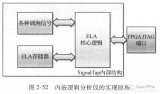

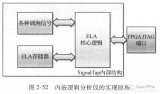

对于FPGA调试,主要以Intel FPGA为例,在win10 Quartus ii 17.0环境下....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 01-12 09:34

•2508次阅读

大家在进行FPGA选型时都会看见一个参数:Speed Grade,这就是芯片的速度等级。

![的头像]() FPGA之家 发表于

FPGA之家 发表于 01-08 09:20

•3185次阅读

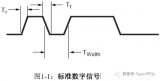

在数字设计中,时钟代表从寄存器(register)到寄存器可靠传输数据的时间基准。

![的头像]() FPGA之家 发表于

FPGA之家 发表于 01-04 09:16

•3049次阅读

一般情况下, i2c 设备焊接没什么问题,按照设备手册一步步来,基本上就顺风顺水能够用起来。如果这么....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 12-26 09:33

•1297次阅读

首先个人用的是QuartusII11.0,开发板用的是CycloneIV的EP4CE6E22C8N芯....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 12-25 09:13

•1348次阅读

有一个有趣的现象,众多数字设计特别是与FPGA设计相关的教科书都特别强调整个设计最好采用唯一的时钟域....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 12-22 09:04

•1524次阅读

笔者与SDRAM有段不短的孽缘,它作为冤魂日夜不断纠缠笔者。笔者尝试过许多方法将其退散,不过屡试屡败....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 12-15 09:09

•1424次阅读

写了这么多FPGA的文章却从来没有涉及过国产FPGA,很多网友甚至不知道还有国产FPGA。下面列举一....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 12-12 11:30

•4650次阅读

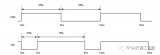

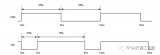

AD9249的SPI控制模块包含4根信号线,即CSB1、CSB2、SDIO以及SCLK。但CSB1、....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 12-12 10:47

•2499次阅读

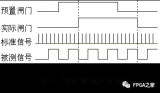

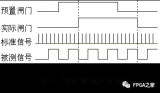

本篇将以德州仪器(TI)的高速ADC芯片—ads52j90为例,进行ADC的4线SPI配置时序介绍与....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 12-11 09:05

•1851次阅读

I2C协议中最重要的一点是I2C地址。这个地址有7位和10位两种形式。

![的头像]() FPGA之家 发表于

FPGA之家 发表于 12-05 09:16

•1648次阅读

有将近两个月没有学习一些新东西,更新一下博客了。一直在忙公司的一个项目,是做一款支持LSTM和RNN....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 11-30 09:36

•2391次阅读