PYNQ经典项目分享:可重配置IO

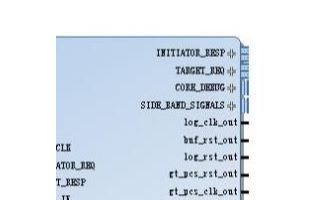

上图为工程项目示意图。通过软硬件划分,在PS端中负责Linux和通信,PL端例化了6个PR(Part....

Aurora IP建立仿真及测试

在Vivado软件中,我们生成好IP后可以可以打开带有例子的工程,进行仿真查看LANE_UP和CHA....

为什么在Verilog HDL设计中一定要用同步而不能用异步时序逻辑?

同步时序逻辑是指表示状态的寄存器组的值只可能在唯一确定的触发条件发生时刻改变。只能由时钟的正跳沿或负....

通信中dBFS、dBm、dBV、dBW、0dB、-3dB的定义解析

dBV(V大写),dBu(u小写),是模拟音频时代最常用到的两个单位。

简单来说专业音频领域,标准....

介绍FPGA设计中时序分析的一些基本概念

时钟的时序特性主要分为抖动(Jitter)、偏移(Skew)、占空比失真(Duty Cycle Di....

FPGA复位电路的实现——以cycloneIII系列芯片为例

有人说FPGA不需要上电复位电路,因为内部自带上电复位信号。也有人说FPGA最好加一个上电复位电路,....

初识FPGA CLB之LUT实现逻辑函数

LUT中文名字叫查找表。以7系列的FPGA为例,每一个Slice里面有四个LUT。FPGA就是通过L....

仔细看完你就懂卡尔曼滤波(Kalman Filter)

回忆一下HMM的基本模型(例如以下图所看到的)。当中涂有阴影的圆圈(yt-2, yt-1, yt)相....

数据采集(DAQ)基础知识:重要准则和通用术语

数据采集系统所使用的计算机会极大地影响连续采集数据的最大速度,而当今的技术已可以使用Pentium和....

SRIO IP核的三层协议的作用?

数据从远程设备(假设为DSP的SRIO端)传输过来,FPGA端(假设我们这端为FPGA的SRIO端口....

基于EV10AQ190的高速ADC接口设计

外部给该ADC芯片提供一个时钟CLK,频率为2.5GHz,通过内部时钟电路,2分频之后的时钟送到核A....

一种傅里叶分析新颖的理解方法

有了“1”,还要有“0”才能构成世界,那么频域的“0”是什么呢?cos(0t)就是一个周期无限长的正....

解读ADC采样芯片EV10AQ190A的工作模式

直接说重点,任意一个输入端口输入的模拟信号同时进入ADC芯片的四个核(也可以理解为4个通道),这四个....

解读ADC采样芯片(EV10AQ190A)的工作模式(四通道模式)

由上图可知,四通道模式有4个输入端口,我们分别称其为A端口,B端口,C端口,与D端口,四个端口分别对....

解读ADC采样芯片(EV10AQ190A)的采样(工作)模式(双通道模式)

当信号从A输入端口输入时,就意味着使用ADC A和ADC B通道对输入的模拟信号进行采样,双通道组态....

手把手教系列之一阶数字滤波器设计实现(附代码)

一阶数字滤波计算简单,实现代价非常低。在滤除高频噪声时应用很广泛。其本质是 IIR 滤波器,为啥要单....

如何理解FPGA的配置状态字寄存器

赛灵思的FPGA有多种配置接口,如SPI,BPI,SeletMAP,Serial,JTAG等;如果从....

ARM和FPGA究竟是如何进行通信的呢?

ZYNQ拥有ARM+FPGA这个神奇的架构,那么ARM和FPGA究竟是如何进行通信的呢?本章通过剖析....

FPGA的算法解析1:整数操作与加减法器

整数在 IEEE 的规定上有短整数 short integer , 中整数 integer 和 长整....

傅立叶变换的实质-正交之美

对于信号,如果我们想用谐波来表示它的话,我们最好基于不同的频率将之进行分解,那么接下来的问题就是寻找....

Xilinx FPGA的FMC接口

FMC标准定义了单宽度(69mm*76.5mm)和双宽度(139mm*76.5mm)两种尺寸。单宽度....

FPGA系列之“Zynq MPSoC PS-PL AXI Interfaces”

S_AXI_ACP_FPD接口实现了PS 和PL 之间的低延迟连接,通过这个128位的接口,PL端可....

Vivado怎么避免信号被优化掉

刚写了一段 Verilog代码,辛辛苦苦花了很长时间综合,在debug的过程中,却找不到需要debu....