消失了好久,没有写文章,也没有做笔记,因为最近再赶一个比赛,时间很紧,昨天周六终于结束了,所以趁着周....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 11-20 10:04

•715次阅读

带宽是影响FPGA加速器的重要因素,因为大量的并行计算对数据量要求很大。

![的头像]() FPGA之家 发表于

FPGA之家 发表于 11-16 16:36

•1373次阅读

单片机晶振电路中两个微调电容不对称会怎样?相差多少会使频率怎样变化?我在检测无线鼠标的接受模块时,发....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 11-15 15:54

•841次阅读

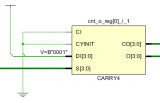

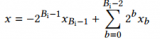

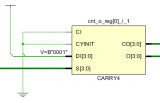

大规模的整数加法在数字信号处理和图像视频处理领域应用很多,其对资源消耗很多,如何能依据FPGA物理结....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 11-08 09:06

•1465次阅读

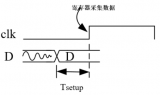

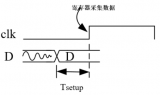

为了确保寄存器在时钟沿稳定采集数据,那么必须要满足寄存器的建立,保持时间要求。 建立时间要求:在寄存....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 11-07 09:30

•550次阅读

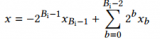

由于卷积核数据在计算过程中保持不变,更新较慢。这样就可以利用LUT来存储权重并同时进行乘法运算。

![的头像]() FPGA之家 发表于

FPGA之家 发表于 11-06 09:07

•783次阅读

方法1.通过状态机来实现,通过verilog控制FPGA,让它该快的时候快,该慢的时候慢。

![的头像]() FPGA之家 发表于

FPGA之家 发表于 11-02 09:48

•681次阅读

Xilinx 提供两款工具来构建和部署嵌入式 Linux 解决方案。这些工具有 Xilinx 的 P....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 10-31 16:59

•616次阅读

Vitis 统一软件平台包括一组广泛的、性能优化的开源库,这些库提供了即开即用的加速功能,并且对现有....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 10-30 17:23

•703次阅读

当您想到处理性能时,脑子里最先出现的影响因素往往并不是存储吧?但是,如果您正在处理海量的大型数据集,....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 10-24 16:41

•670次阅读

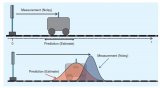

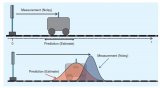

通常情况下所使用的Kalman滤波器是离散时间系统形式的。我们真正想得到的物理量表示成系统状态中的某....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 10-19 10:07

•2586次阅读

谐振器和负载电容要求必须尽可能地靠近振荡器的引脚,减少失真和起振时间。外部用户时钟必须使用占空比约为....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 10-16 16:48

•1277次阅读

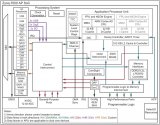

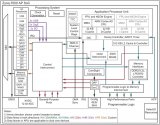

ARM端配置如下图所示,以5处的ARM-A9为核心,使用1处的UART1打印调试信息,使用2处的网口....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 10-16 16:43

•1778次阅读

首先要做的是最简单的均值滤波算法。均值滤波是典型的线性滤波算法,它是指在图像上对目标像素给一个模板,....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 10-16 09:23

•798次阅读

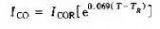

由于P-N结的正向压降受温度的影响较大,所以用P-N为基本单元构成的双极型半导体逻辑元件(TTL、H....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 10-13 16:07

•1173次阅读

PON接入:无源光网络 (PON) 是网络运营商部署的主要宽带接入技术之一。依托可编程逻辑和硬件加速....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 10-12 16:16

•1160次阅读

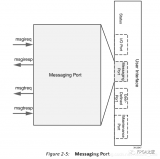

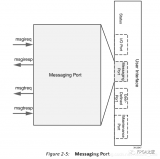

消息传递端口是可选接口(消息也可以组合到I / O端口上,并使用Vivado集成设计环境(IDE)设....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 10-10 15:58

•1146次阅读

在 SystemVerilog 中,联合只是信号,可通过不同名称和纵横比来加以引用。

![的头像]() FPGA之家 发表于

FPGA之家 发表于 10-08 15:45

•1292次阅读

Step3: 按照“Vivado中进行ZYNQ硬件部分设计”中介绍的,直到在SDK中编写C代码步骤。....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 09-23 09:25

•1022次阅读

ZYNQ内部的总体框架如所示,PS中包含2个ARM Cortex-9的内核,一些基本的外设扩展口以及....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 09-22 09:26

•857次阅读

硬件描述语言(verilog,systemVerilog,VHDL等)不同于软件语言(C,C++等)....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 09-21 09:07

•1235次阅读

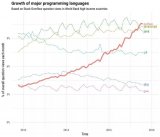

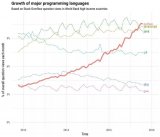

一个人开发一门语言,难度那是相当大的。好在当时而立之年的Guido已经有了相当的开发经验。此前,他花....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 09-10 09:07

•735次阅读

VHDL与Verilog硬件描述语言在数字电路的设计中使用的非常普遍,无论是哪种语言,仿真都是必不可....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 09-09 10:16

•1665次阅读

IIR(Infinite Impulse Response)无线脉冲响应滤波器。

![的头像]() FPGA之家 发表于

FPGA之家 发表于 09-07 09:51

•1319次阅读

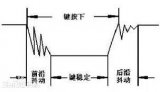

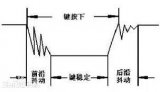

通常的按键所用开关为机械弹性开关,当机械触点断开、闭合时,由于机械触点的弹性作用,一个按键开关在闭合....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 09-05 10:43

•1177次阅读

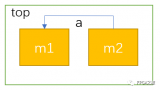

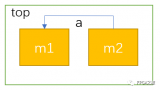

在开始设计前,根据设计划分好各功能模块(为了叙述方便,这里以对“FPGA数字信号处理(十三)锁相环....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 09-04 09:54

•1610次阅读

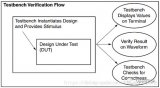

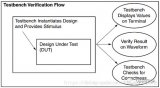

自动化验证testbench结果可以减少人工检查的时间和可能犯的失误,尤其对于比较大的设计。

![的头像]() FPGA之家 发表于

FPGA之家 发表于 09-04 09:15

•852次阅读

用“数组”来表述Verilog HDL中的定义并不准确,但对大多数人来说应该更好理解。

![的头像]() FPGA之家 发表于

FPGA之家 发表于 09-02 09:21

•1519次阅读

将设计和验证从逻辑上和时间上分开,使得两个小组可以相对独立。

![的头像]() FPGA之家 发表于

FPGA之家 发表于 09-01 15:38

•1259次阅读

对于小型设计来说,最好的测试方式便是使用TestBench和HDL仿真器来验证其正确性。一般Te....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 09-01 09:57

•1147次阅读