CRC即循环冗余校验码:是数据通信领域中最常用的一种查错校验码,其特征是信息字段和校验字段的长度可以....

Vivado的时序约束是保存在xdc文件中,添加或创建设计的工程源文件后,需要创建xdc文件设置时序....

Verilog HDL(Hardware Description Language)是一种硬件描述语....

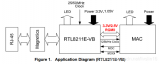

以太网MAC模块负责实现以太网MAC子层的功能,完成802.3ab的数据封装与解封。其同时负责适配硬....

本文将使用三段式状态机(Moore型)的写法来对DS18B20进行测温操作,以便了解DS18B20和....

AXI接口FIFO是从Native接口FIFO派生而来的。AXI内存映射接口提供了三种样式:AXI4....

ADC和DAC是FPGA与外部信号的接口,从数据接口类型的角度划分,有低速的串行接口和高速的并行接口....

复位电路也是数字逻辑设计中常用的电路,不管是 FPGA 还是 ASIC 设计,都会涉及到复位,一般 ....

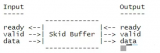

skid buffer(pipeline缓冲器)介绍 解决ready/valid两路握手的时序困....

DDR内存控制器是一个高度集成的组件,支持多种DDR内存类型(DDR2、DDR3、DDR3L、LPD....

调试,即Debug,有一定开发经验的人一定会明确这是设计中最复杂最磨人的部分。对于一个庞大复杂的FP....

增量式编码器是一种将位移信息转换成周期性电信号,再将电信号转换成脉冲计数的装置。

Xilinx的FIR IP核属于收费IP,但是不需要像 Quartus那样通过修改license文件....

1、在verilog中有时会用signed修饰符来修饰定义的数据,运算的时候也会用$signed()....

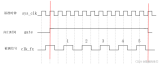

根据下面的时序图实现这个组合逻辑电路。

本文详细介绍了多种图像处理技术,包括RG/GB单通道提取、亮度和对比度调整、图像反转、均值滤波、高斯....

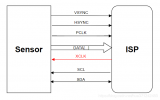

DVP(Digital Video Port) 是传统的sensor输出接口,采用并行输出方式,d数....

其实使用到ADI的东西,基本也就没有太去关注协议这些东西,只是简简单单的有个了解就行,在实际调试的时....

SPI = Serial Peripheral Interface,是串行外围设备接口,是一种高速,....

像素行与像素窗口 一幅图像是由一个个像素点构成的,对于一幅480*272大小的图片来说,其宽度是48....

1. 前言 最近在做以太网相关的东西,其中一个其中想要使用MAC通过光电转换模块来完成数据的收发。在....

AWID[3:0]与ARID[3:0]:对于只有一个主机从机设备,该值可设置为任意。

一般来讲,如果要实现移位寄存器的话,通常都是写RTL用reg来构造,比如1bit变量移位一个时钟周期....

一、移位寄存器 SLICEM函数发生器也可以配置为32位移位寄存器,而无需使用slice中可用的触发....

xilinx FPGA IOB约束使用以及注意事项 一、什么是IOB约束 在xilinx FPGA中....

1. XADC介绍 xadc在 所有的7系列器件上都有支持,通过将高质量模拟模块与可编程逻辑的灵活性....

一.依据模拟环设计数字环 根据信号与系统的分析理论,一个系统完全由系统函数来确定,因此我们可从系统函....

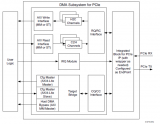

1.1 课程介绍 这一章开始主要介绍 XILINX FPGA PICE IP XDMA IP的使用....

1、FPGA频率测量? 频率测量在电子设计和测量领域中经常用到,因此对频率测量方法的研究在实际工程应....

一 傅里叶变换FFT 想必大家对傅里叶老人家都不陌生了,网上也有这方面的很多资料。通过FFT将时域信....