ISP从图像传感器获取 RAW 像素,并将其转换为与人类对所捕获场景的感知相匹配的图像。ISP 是每....

![的头像]() Hack电子 发表于

Hack电子 发表于 11-18 10:21

•471次阅读

由于定点的四则运算比较简单,如加减法只要注意符号扩展,小数点对齐等问题即可。在本文中,运用在前一节中....

![的头像]() Hack电子 发表于

Hack电子 发表于 11-16 11:19

•473次阅读

前言 最近看advanced fpga 以及fpga设计实战演练中有讲到复位电路的设计,才知道复位电....

![的头像]() Hack电子 发表于

Hack电子 发表于 11-15 11:13

•177次阅读

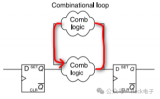

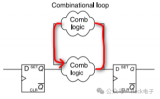

组合逻辑环路(Combinational Loops):指组合逻辑的输出信号不经过任何时序逻辑电路(....

![的头像]() Hack电子 发表于

Hack电子 发表于 11-15 10:49

•236次阅读

本文将首先介绍FPGA的基础知识,包括FPGA的工作原理以及为什么要使用FPGA等,然后讨论设计和执....

![的头像]() Hack电子 发表于

Hack电子 发表于 11-11 11:29

•942次阅读

科学计数法 你可能不了解「浮点数」,但你一定了解「科学记数法」。 10进制科学记数法把一个数表示成a....

![的头像]() Hack电子 发表于

Hack电子 发表于 11-11 09:59

•272次阅读

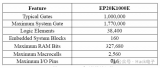

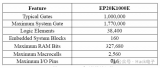

我们在比较FPGA的芯片参数时经常说某一款FPGA是多少万门的,也有的说其有多少个LE,那么二者之间....

![的头像]() Hack电子 发表于

Hack电子 发表于 11-11 09:45

•303次阅读

随着医疗科技的飞速发展,医疗成像设备在医学诊断和治疗中扮演着至关重要的角色。从传统的X射线到先进的计....

![的头像]() Hack电子 发表于

Hack电子 发表于 11-07 09:00

•361次阅读

本文介绍了Vidado中FFT IP核的使用,具体内容为:调用IP核>>配置界面介绍>>IP核端口介....

![的头像]() Hack电子 发表于

Hack电子 发表于 11-06 09:51

•1006次阅读

在数字信号处理系统中,有限脉冲响应(finite impulse response,FIR)数字滤波....

![的头像]() Hack电子 发表于

Hack电子 发表于 11-05 16:26

•678次阅读

之前已经介绍过《FPGA在汽车电子中应用-ADAS》,但是很多人留言说是没有相关例程,应用不够直观,....

![的头像]() Hack电子 发表于

Hack电子 发表于 11-05 09:19

•274次阅读

镜头由一组或多组光学玻璃镜片组成,透过机械的结构以光学原理形成镜像,不同的镜片组合成像距离也各有长短....

![的头像]() Hack电子 发表于

Hack电子 发表于 11-01 09:55

•396次阅读

本博客提供了基于2023.2 Vivado的参考工程,展示如何使用Microblaze 地执行(XI....

![的头像]() Hack电子 发表于

Hack电子 发表于 10-29 14:23

•379次阅读

下载这个最大的、支持所有的 OS 如 Windows/Linux 的安装包。

![的头像]() Hack电子 发表于

Hack电子 发表于 10-29 09:47

•739次阅读

用RAM实现一个DDS,从原理上来说很简单,在实际使用的时候,可能没有直接使用官方提供的IP核来的方....

![的头像]() Hack电子 发表于

Hack电子 发表于 10-25 16:54

•1058次阅读

ZYNQ PL 部分等价于 Xilinx 7 系列 FPGA,因此我们将首先介绍 FPGA 的架构。....

![的头像]() Hack电子 发表于

Hack电子 发表于 10-25 16:50

•1264次阅读

在使用FPGA的时候,有些IP核是需要申请后才能使用的,本文介绍如何申请xilinx IP核的lic....

![的头像]() Hack电子 发表于

Hack电子 发表于 10-25 16:48

•391次阅读

这里讲解SATA主机协议的物理层的实现过程。

![的头像]() Hack电子 发表于

Hack电子 发表于 10-22 15:17

•318次阅读

如果您不确定如何设置环境变量,尝试"1" 或 "TRUE"。

![的头像]() Hack电子 发表于

Hack电子 发表于 10-22 13:32

•213次阅读

许多FPGA有构造在输入和输出缓冲器中的触发器来优化芯片的时序入和出。同时这些专门的IO缓冲器是使能....

![的头像]() Hack电子 发表于

Hack电子 发表于 04-01 11:37

•618次阅读

14.2节提到的问题①,即设计中有很大的扇出,对于如何获知该扇出信号有多种途径。常见的途径是通过FP....

![的头像]() Hack电子 发表于

Hack电子 发表于 03-20 17:33

•2769次阅读

随着电子技术的进步.FPGA逻辑电路能完成的功能越来越多,同样也带来了一个很大的问题,即逻辑电路的规....

![的头像]() Hack电子 发表于

Hack电子 发表于 03-18 10:57

•847次阅读

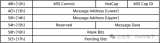

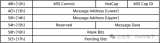

Xilinx PCIE IP中MSI中断相关的地址如下图1所示,如果想要成功产生中断,MSI Con....

![的头像]() Hack电子 发表于

Hack电子 发表于 02-25 09:24

•2773次阅读

DE2_TV中,有关于寄存器的配置的部分,采用的方法是通过IIC的功能,这里对IIC总线的FPGA实....

![的头像]() Hack电子 发表于

Hack电子 发表于 01-05 10:16

•1076次阅读

DisplayPort 1.4 Tx Subsystem core的最简pipeline就是如它的l....

![的头像]() Hack电子 发表于

Hack电子 发表于 12-29 10:09

•550次阅读

有时候在debug GT的时候,需要用Digital monitor读出RX equalizer的c....

![的头像]() Hack电子 发表于

Hack电子 发表于 12-16 10:27

•687次阅读

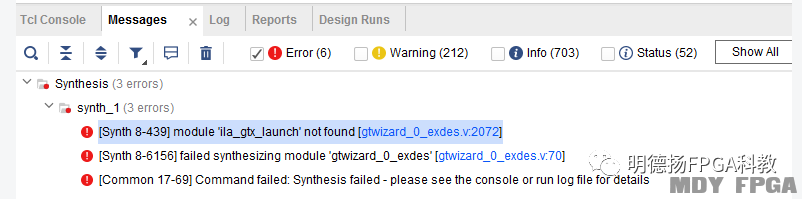

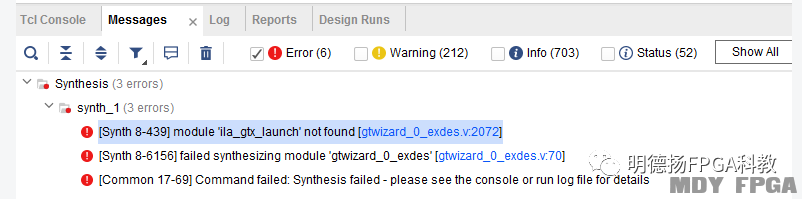

【关键问题!!!!重要!!!】VIVADO会在MESSAGE窗口出提示很多错误和警告信息!

![的头像]() Hack电子 发表于

Hack电子 发表于 12-15 10:11

•2051次阅读

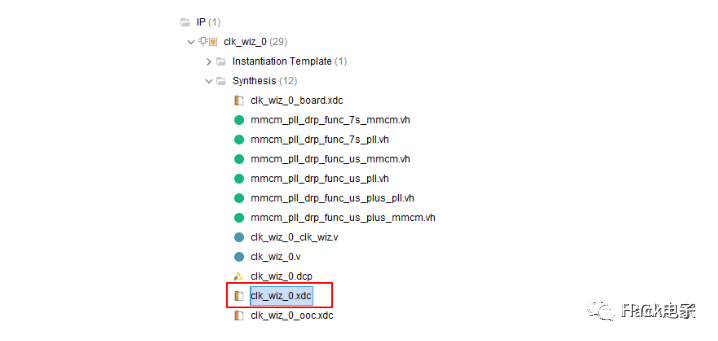

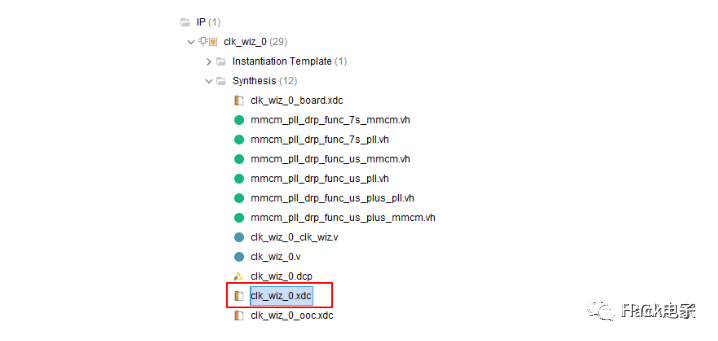

在约束文件XDC(SCOPED_TO_REF、SCOPED_TO_CELLS)中使用“create_....

![的头像]() Hack电子 发表于

Hack电子 发表于 12-15 10:10

•2884次阅读

你可以随意去除水印,瑕疵,还可以选中去除的区域(路人甲,人物),处理后自动擦除,自动根据周边的区域自....

![的头像]() Hack电子 发表于

Hack电子 发表于 12-13 10:27

•469次阅读

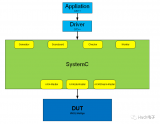

当FPGA开发者需要做RTL和C/C++联合仿真的时候,一些常用的方法包括使用MicroBlaze软....

![的头像]() Hack电子 发表于

Hack电子 发表于 12-13 10:13

•1291次阅读