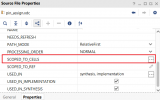

有时我们对时序约束进行了一些调整,希望能够快速看到对应的时序报告,而又不希望重新布局布线。这时,我们....

vivado -mode tcl和vivado -mode batch有什么区别?

随着FPGA规模的增大,设计复杂度的增加,Vivado编译时间成为一个不可回避的话题。尤其是一些基于....

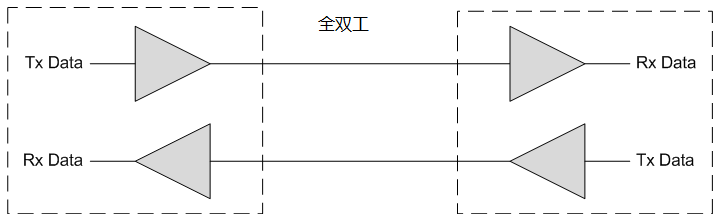

典型的全双工(Full Duplex)系统如下图所示,芯片1和芯片2之间有彼此独立的数据传输线,这意....

从综合角度看,Vivado 2024.1对SystemVerilog和VHDL-2019的一些特性开....

Vivado 2024.1已正式发布,今天我们就来看看新版本带来了哪些新特性。

对于逻辑级数较大的路径,常用的时序收敛的方法之一就是采用Retiming(中文翻译为重定时)。Ret....

典型的排序算法包括冒泡排序、选择排序、插入排序、归并排序、快速排序、希尔排序、计数排序、双调排序等。

FPGA设计中,生成时钟分为两大类:自动生成时钟和用户生成时钟。

采用UltraScale/UltraScale+芯片进行DFX设计时,建议从以下角度对设计进行检查。

生成时钟包括自动生成时钟(又称为自动衍生时钟)和用户生成时钟。自动生成时钟通常由PLL或MMCM生成....

UltraScale/UltraScale+芯片开始支持BUFG_*、PLL和MMCM出现在动态区,....

对于UltraScale/UltraScale+芯片,几乎FPGA内部所有组件都是可以部分可重配置的

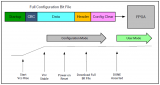

Fullconfiguration bitstreams对应的是静态区加动态区的完整设计,因此,该文....

假定设计中存在两个RP,分别为RP1和RP2,那么就要避免出现RP1输出直接连接到RP2或者相反从R....

相比于Project模式,Vivado Non-Project模式可以提供用户更多的控制权,进而用户....

针对DFX设计,Vivado提供了命令report_pr_configuration_analysi....

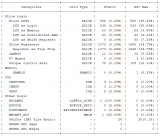

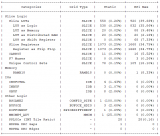

选项-complexity聚焦在设计的资源使用情况,会给出指定RP下各RM的资源使用情况,同时给出各....

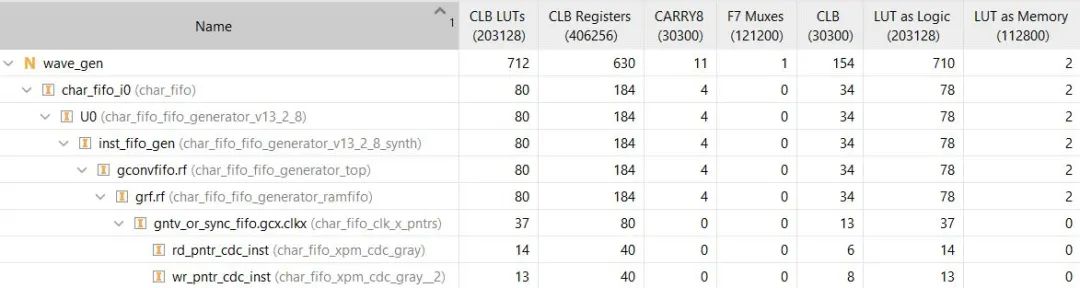

FIFO为什么不能正常工作?复位信号有效长度不够,接口时序不匹配,可看下面这篇文章。 本文将介绍: ....

我们再从对可综合代码的支持角度看看SystemVerilog相比于Verilog的优势。针对硬件设计....

谈到SystemVerilog,很多工程师都认为SystemVerilog仅仅是一门验证语言,事实上....

SystemVerilog引入了interface,这里我们从可综合的RTL代码的角度聊聊inter....

谈到package,用过VHDL的工程师并不陌生。实际上,SystemVerilog中的packag....

DFX模式下要求在设计的顶层文件,每个RP对应的RM只以一个空的接口形式存在,这样对顶层综合时,RM....

DFX(Dynamic Function eXchange)的前身是PR(部分可重配置,Partia....

命令set_multicycle_path常用来约束放松路径的约束。通常情况下,这种路径具有一个典型....

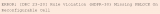

在FPGA设计中,我们经常会碰到这样的情形:从快时钟域到慢时钟域完成位宽转换,这时,这两个时钟是同步....

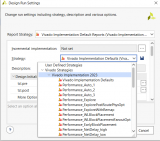

Vivado提供了丰富的Implementation Strategy,如下图所示。这使得扫描策略成....

Vivado以IP为核心的设计理念的一个重要支撑就是IP Integrator(简称IPI,IP集成....

在常规非DFX(DynamicFunction eXchange)的Vivado设计中,我们可能会碰....