基于PVD 薄膜沉积工艺

PVD篇 PVD是通过溅射或蒸发靶材材料来产生金属蒸汽,然后将金属蒸汽冷凝在晶圆表面上的过程。应用材....

什么是Hybrid Bonding?Hybrid Bonding是铜铜键合吗?

在Hybrid Bonding前,2D,2.5D及3D封装都是采用焊锡球凸点(solder bump....

TSV关键工艺设备及特点

TSV 是目前半导体制造业中最为先进的技术之一,已经应用于很多产品生产。实现其制程的关键设备选择与工....

DISCO:一家少被提及的半导体设备巨头

在深入探讨这些主题之前,让我们简要介绍一下公司的历史以及他们独特的文化。在专注于半导体之前,DISC....

DRAM的电容技术发展历程

通过控制温度来控制晶相,将非晶AlO、T相ZrO制作为新型介质薄膜。因为主要贡献点是EOT很低的新型....

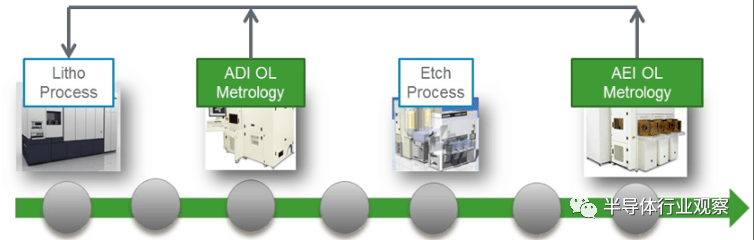

一文解读DRAM的9大刻蚀技术

在将晶圆制成半导体的过程中需要采用数百项工程。其中,一项最重要的工艺是蚀刻(Etch)——即,在晶圆....

台积电3nm FinFET工艺

最小 Lg 是沟道栅极控制的函数,例如从具有不受约束的沟道厚度的单栅极平面器件转移到具有 3 个栅极....

台积电:未来十年的CMOS器件技术

添加更多的栅极(例如在 FinFET 中),将使其中的沟道被限制在三个栅极之间,从而能够将 Lg 缩....

志橙半导体:半导体芯片设备提供核心部件-SiC涂层石墨基座

志橙半导体成立于2017年底,专注于为半导体芯片设备提供核心部件-SiC涂层石墨基座,据称是国内首家....

微导纳米募集资金10亿元将聚焦光伏、半导体两大赛道

2019年、2020年和2021年,微导纳米的营收分别为2.16亿元、3.13亿元和4.28亿元;净....

晶体管缩放:将FinFET扩展到5nm以上;启用门全方位拐点

FinFET路线图有三个重要的技术挑战:翅片弯曲、高k金属栅极(HKMG)和接口关键尺寸缩放以及源极....

海力士:引领High-k/Metal Gate工艺变革

栅极由绝缘膜(栅氧化层, gate oxide)和电极(栅电极, gate electrode)组成....

蔡司PROVE - 光掩膜量测解决方案

和晶圆制造工艺类似,图形放置位置是光掩膜量测中相当重要的一部份。完整的芯片设计不仅对每一层光掩膜的特....