(1)ERROR:Interface Designer constraint generatio....

感谢朋友提供的视频。 1.软件安装 step1: 安装Python,注意勾选“Add Python ....

通过get_port命令查看接口。 get_ports * 以LVDS的输入输出为例 怎样去查看ou....

因为目前软件的限制,RISCV的逻辑不能同时共用JTAG,所以如果想要同时去调试逻辑和RISCV的话....

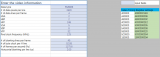

易灵思RAM在使用时可以会遇到一些问题,这里把常用的问题总结下。 1、ram初始化文件路径是工程路径....

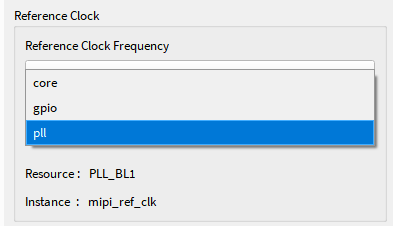

MIPI Dsi的使用相比于CSI多了一些寄存器控制,生成的example直接仿真是可以的,但是修改....

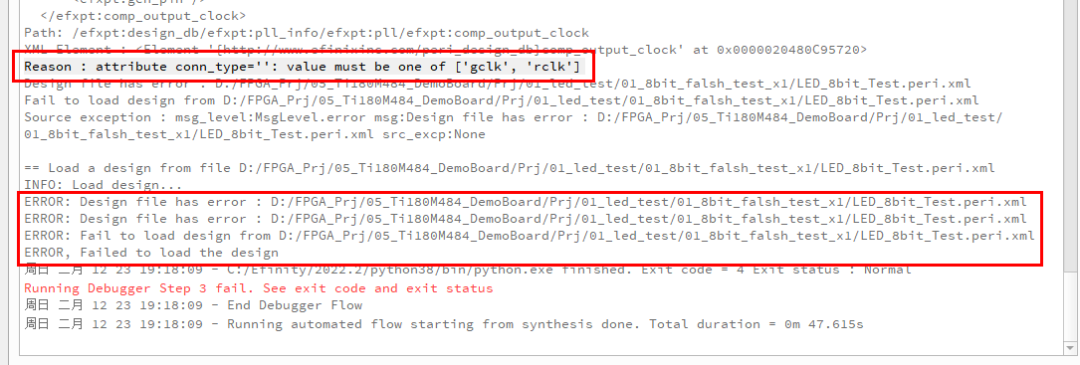

(1)ERROR:Interface Designer constraint generation ....

(1)ERROR:Interface Designer constraint generation ....

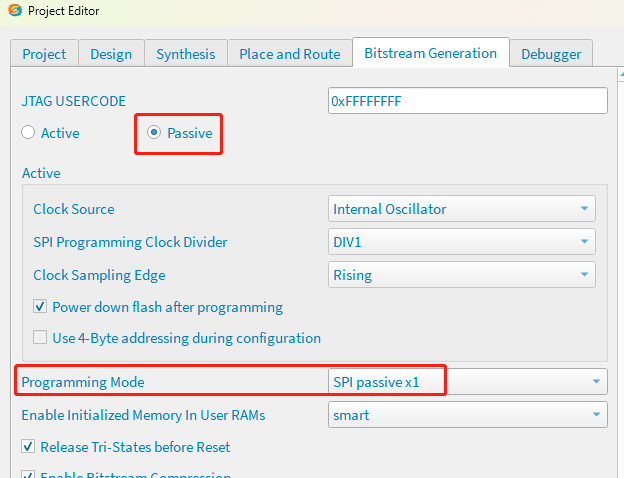

选择Generic Image Combination.并选择右侧的“*”添加文件,逻辑文件是生成的....

step1:安装Python,注意勾选“Add Python 3.7 to PATH” (2022版....

最近陆续有客户在评估易灵思的Ti180。Ti180的MIPI 2.5G是硬核。今天做一个简单的移植来....

MIPI Dsi的使用相比于CSI多了一些寄存器控制,生成的example直接仿真是可以的,但是修改....

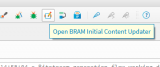

之前有人问题易灵思的BRAM是否可以修改ROM的初始化参数,像xilinx一样不需要编译,也有人问R....

生成相应的下载文件。注意修改Bitstream生成模式时,不需要进行工程的全编译,只需运行最后一步数....

易灵思RAM在使用时可以会遇到一些问题,这里把常用的问题总结下。

除通过外部多功能IO来选择之外,易灵思通过内部重配置实现远程更新操作也非常简单。

MIPI Dsi的使用相比于CSI多了一些寄存器控制,生成的example直接仿真是可以的,但是修改....

MIPI Dsi的使用相比于CSI多了一些寄存器控制,生成的example直接仿真是可以的,但是修改....

MIPI Dsi的使用相比于CSI多了一些寄存器控制,生成的example直接仿真是可以的,但是修改....

说明:该下载器把SPI与JTAG管脚进行了分开处理。 鉴于JTAG使用较多,SPI使用较少,所以把J....

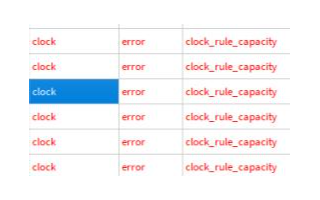

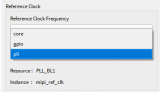

关于clkout4的说明其实不多,在PLL的说明中提到CLKOUT4只用于top和bottom的区域....

最近陆续有客户在评估易灵思的Ti180。Ti180的MIPI 2.5G是硬核。今天做一个简单的移植来....

如果普通的GPIO怎么走全局时钟网络,其实很简单,打开原主文档,找到EFX_GBUFCE,该部分提供....

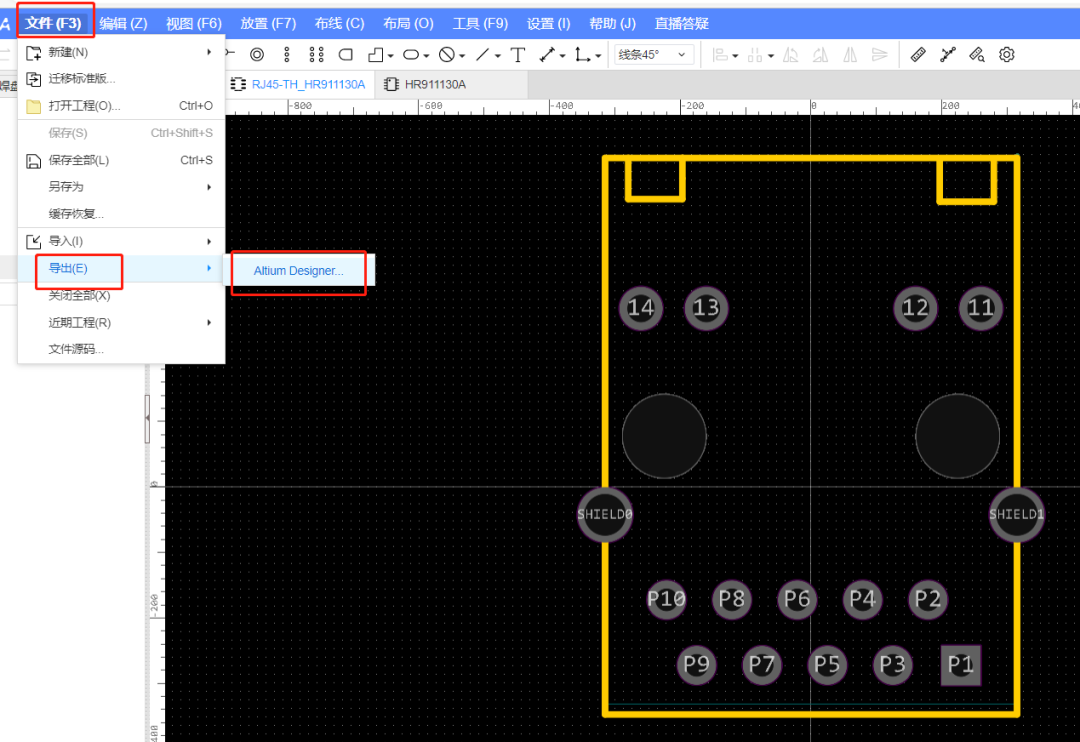

怎样把立创的PCB转成allegro的

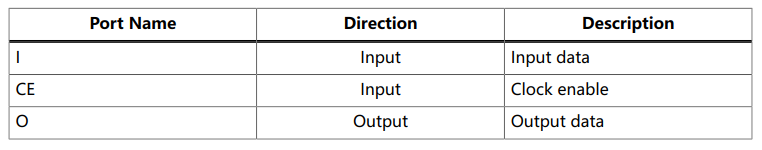

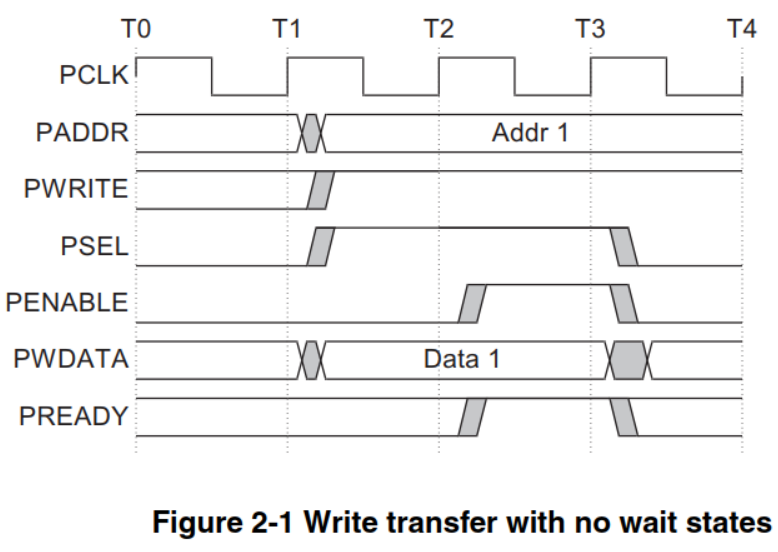

APB3是一个低功耗低成本接口。所有信号在时钟上升沿传输,每次传输需要两个时钟周期。

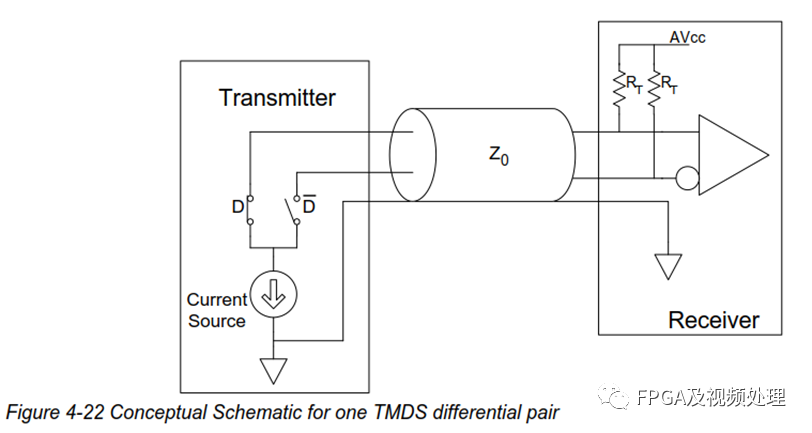

xilinx和altera都有通过IO驱动HDMI的方案,支持的分辨率各有不同,这跟不同系列的FPG....

如果工程直接复制另一个工程,路径一定要修改,建议重新eclipse工程。

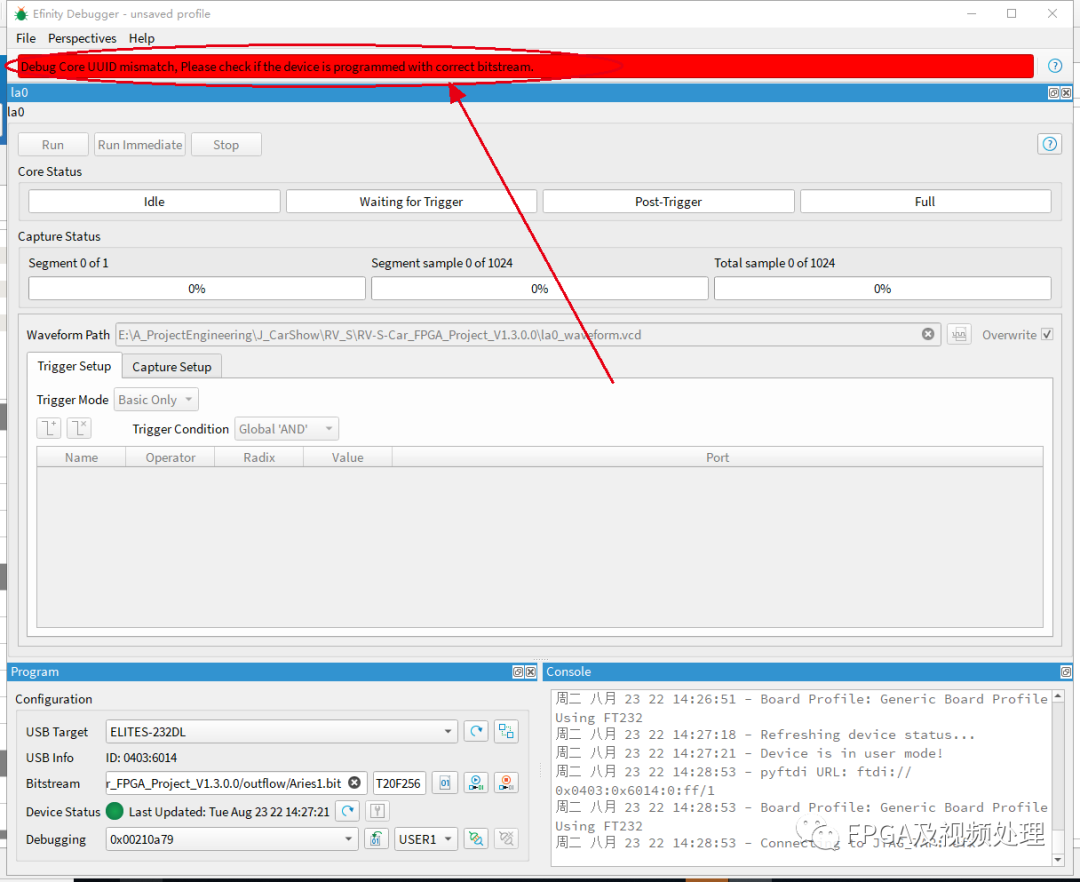

Efinity在Debug时会出现UUID mismatch错误。很多刚开始使用的人经常遇到。

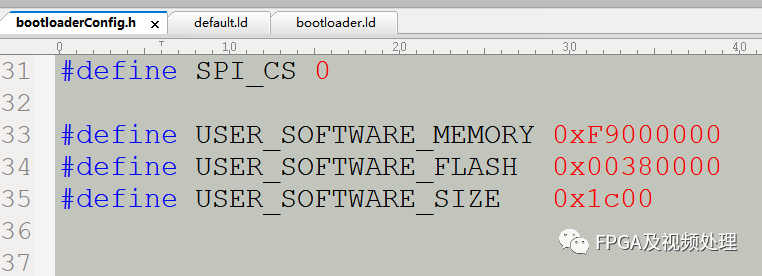

Ti60F100内部是一个16Mbit的flash,每个地址对应的是一个8位的数据,所以,地址范围是....

Efinity用新版本的软件打开老工程时,可能会出现编译不能通过的情况,并且打不开interface....