随着现在AI的快速发展,使用FPGA和ASIC进行推理加速的研究也越来越多,从目前的市场来说,有些公....

![的头像]() 傅里叶的猫 发表于

傅里叶的猫 发表于 10-29 14:12

•334次阅读

在当今飞速发展的通信技术领域,Xilinx RFSoC(Radio Frequency System....

![的头像]() 傅里叶的猫 发表于

傅里叶的猫 发表于 10-25 10:28

•655次阅读

今天我们看的这篇论文介绍了在多FPGA集群上实现高级并行编程的研究,其主要目标是为非FPGA专家提供....

![的头像]() 傅里叶的猫 发表于

傅里叶的猫 发表于 07-24 14:54

•1234次阅读

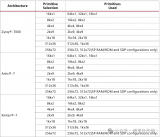

当使用ram时,width是960bit,depth是16bit,只有15Kb大小, 为什么占用了很....

![的头像]() 傅里叶的猫 发表于

傅里叶的猫 发表于 05-06 14:12

•534次阅读

在数字设计的Implementation过程中,从RTL到GDSII的每一步都是高度计算密集型的。

![的头像]() 傅里叶的猫 发表于

傅里叶的猫 发表于 04-17 10:11

•429次阅读

在时序报告中,会显示出clock path skew,如果时钟偏移超过0.5ns,就需要额外关注了。

![的头像]() 傅里叶的猫 发表于

傅里叶的猫 发表于 03-13 09:06

•1449次阅读

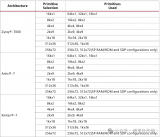

已从该架构中移除BUFMRs、BUFRs、BUFIOs及其相关的路由资源,并被新的时钟缓冲器、时钟路....

![的头像]() 傅里叶的猫 发表于

傅里叶的猫 发表于 03-12 10:03

•1233次阅读

单bit通过两级同步打拍可以有效的解决亚稳态问题。

![的头像]() 傅里叶的猫 发表于

傅里叶的猫 发表于 03-08 09:02

•1324次阅读

UVM中的phase,按照其是否消耗仿真时间($time打印出的时间)的特性,可以分成两大类

![的头像]() 傅里叶的猫 发表于

傅里叶的猫 发表于 02-29 09:26

•1373次阅读

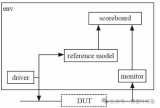

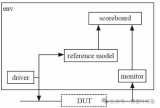

先抛开UVM,回想一下我们在平时写完程序后,是不是肯定需要灌一个激励给DUT,然后再从DUT获取结果....

![的头像]() 傅里叶的猫 发表于

傅里叶的猫 发表于 02-27 09:08

•5867次阅读

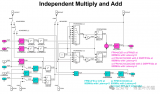

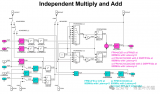

Versal FPGA中最新的DSP原语DSP58,它在最新的DSP48版本上已经有了许多改进,主要....

![的头像]() 傅里叶的猫 发表于

傅里叶的猫 发表于 02-22 09:22

•1418次阅读

proFPGA是mentor的FPGA原型验证平台,当然mentor被西门子收购之后,现在叫西门子E....

![的头像]() 傅里叶的猫 发表于

傅里叶的猫 发表于 01-22 09:21

•1376次阅读

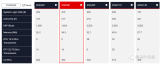

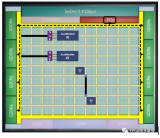

XC7K325T在FPGA圈可谓是家喻户晓,很多FPGA工程师都用过,因为性价比非常高,又因为使用的....

![的头像]() 傅里叶的猫 发表于

傅里叶的猫 发表于 01-09 09:47

•1093次阅读

XC7K325T在FPGA圈可谓是家喻户晓,很多FPGA工程师都用过,因为性价比非常高,又因为使用的....

![的头像]() 傅里叶的猫 发表于

傅里叶的猫 发表于 01-04 09:25

•1707次阅读

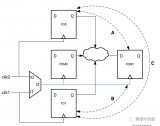

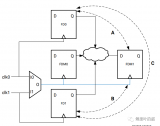

时序场景如下图所示,clk0和clk1两个时钟输入,经过BUFGMUX后,输出到后面的逻辑,但同时c....

![的头像]() 傅里叶的猫 发表于

傅里叶的猫 发表于 12-19 12:56

•1039次阅读

时序场景如下图所示,clk0和clk1两个时钟输入,经过BUFGMUX后,输出到后面的逻辑,但同时c....

![的头像]() 傅里叶的猫 发表于

傅里叶的猫 发表于 12-11 13:55

•596次阅读

HBX-G500是一款高性能可编程加速卡,为AI、计算、网络等领域,提供多通道的高带宽存储、高性能计....

![的头像]() 傅里叶的猫 发表于

傅里叶的猫 发表于 11-29 09:16

•998次阅读

lwIP(Lightweight IP)是一个为嵌入式系统设计的轻量级TCP/IP协议栈。

![的头像]() 傅里叶的猫 发表于

傅里叶的猫 发表于 10-29 17:37

•1951次阅读

内置校准: DDR3和DDR4控制器通常具有内置的校准机制,如ODT (On-Die Termina....

![的头像]() 傅里叶的猫 发表于

傅里叶的猫 发表于 09-11 09:14

•824次阅读

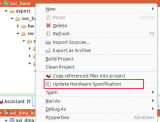

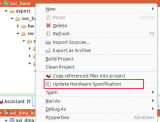

在zynq调试时,经常需要更新xsa文件,更新步骤如下

![的头像]() 傅里叶的猫 发表于

傅里叶的猫 发表于 08-14 09:14

•1568次阅读

前言:本文章为FPGA问答系列,我们会定期整理FPGA交流群(包括其他FPGA博主的群)里面 有价值....

![的头像]() 傅里叶的猫 发表于

傅里叶的猫 发表于 08-08 14:10

•1258次阅读

AXI接口虽然经常使用,很多同学可能并不清楚Vivado里面也集成了AXI的Verificati....

![的头像]() 傅里叶的猫 发表于

傅里叶的猫 发表于 07-27 09:19

•1169次阅读

AXI接口虽然经常使用,很多同学可能并不清楚Vivado里面也集成了AXI的Verificatio....

![的头像]() 傅里叶的猫 发表于

傅里叶的猫 发表于 07-27 09:16

•1647次阅读

版图文件很大,需要处理的数据量非常大,但本身的逻辑判断并不复杂,所以通常不刚需高主频机型,但要求多核....

![的头像]() 傅里叶的猫 发表于

傅里叶的猫 发表于 07-17 15:25

•699次阅读

对于发送时钟和接收时钟是同一时钟的单周期路径,时钟抖动对建立时间有负面影响,但对保持时间没有影响。

![的头像]() 傅里叶的猫 发表于

傅里叶的猫 发表于 06-12 09:15

•635次阅读

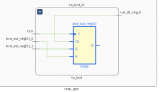

Vivado Schematic中的实线和虚线有什么区别?

![的头像]() 傅里叶的猫 发表于

傅里叶的猫 发表于 06-06 11:13

•1141次阅读

FPGA中的Bank和Clock Region有什么关系?

![的头像]() 傅里叶的猫 发表于

傅里叶的猫 发表于 05-15 09:32

•1147次阅读

我们以一个简单的加法器为例,来看下如何用vcs+verdi仿真Verilog文件并查看波形。

![的头像]() 傅里叶的猫 发表于

傅里叶的猫 发表于 05-08 16:00

•6409次阅读

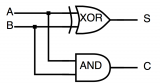

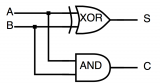

在计算机中,CPU作为中央处理器,内部包含了算术逻辑单元,可以实现数学运算。要计算1+1=2,就需要....

![的头像]() 傅里叶的猫 发表于

傅里叶的猫 发表于 04-27 10:02

•2145次阅读

在默认情况下,一个port只需要一个min和max的dealy值,如果我们设置两次,那么第二次设置的....

![的头像]() 傅里叶的猫 发表于

傅里叶的猫 发表于 04-13 09:07

•1103次阅读