我们已经了解了很多的 KEIL 调试方法,但是到底该怎么使用这些方法呢?这篇文章将介绍个人的调试经验....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 09-02 10:29

•11610次阅读

Vivado调用Questa Sim或ModelSim仿真中存在的一些自动化问题的解决方案。 Viv....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 09-02 10:12

•8387次阅读

Q1 背景: 软件 vivado2018.2 开发板 KC705 设计中涉及到两个时钟域(外部提供的....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 08-26 10:48

•7746次阅读

做芯片第一应该关注的是芯片的PPA(Performance, Power, Area),本篇浅显的部....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 08-26 10:29

•4014次阅读

引言:本文我们介绍FPGA外设DDR2/DDR3硬件设计相关内容,包括PCB板层数估计,信号端接、信....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 08-26 10:12

•3989次阅读

下列 时序检查语句 错误的是() A. $setup(posedge clk, data, tSU)....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 08-25 11:52

•4341次阅读

数字电路设计中遇到跨时钟域(Clock Domain Crossing, CDC)的电路时一般都需要....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 08-25 11:46

•2403次阅读

【前言】 最近手上写了一个练手的小项目,项目的大致要求是实现一个取指,执行电路。取指的指令预存在,从....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 07-27 16:55

•1721次阅读

1 引言 图像增强是指按特定的需要突出一幅图像中的某些信息,同时削弱或者去除某些不需要的信息的处理方....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 07-27 15:08

•2925次阅读

本文将介绍如何使用Icarus Verilog+GTKWave来进行verilog文件的编译和仿真。....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 07-27 09:16

•5297次阅读

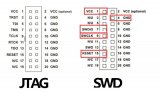

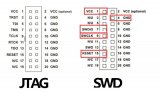

01JTAG简介 JTAG(JointTest ActionGroup)是一个接口,为了这个接口成立....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 07-23 17:53

•67229次阅读

最近在使用示波器测一些波形数据,需要保存记录,以前通常是使用U盘的方式来存波形数据,然后拿到电脑端去....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 07-23 15:19

•10334次阅读

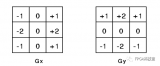

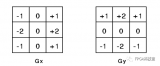

Sobel 原理介绍 索贝尔算子(Sobel operator)主要用作边缘检测,在技术上,它是一离....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 07-23 14:53

•2232次阅读

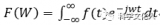

01 FFT简介 快速傅里叶变换 (Fast Fourier Transform,FFT), 即利用....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 07-23 14:29

•6126次阅读

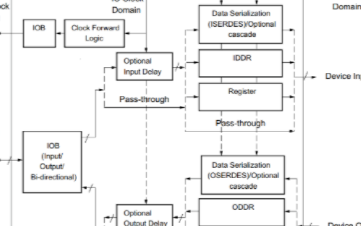

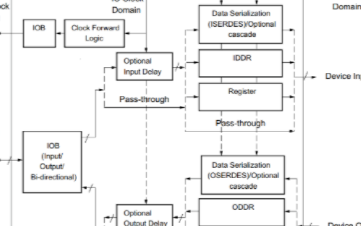

SERDES的优势 引脚数量和通道优势 SERDES最明显的优势是具备更少的引脚数量和线缆/通道数量....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 07-23 11:59

•4280次阅读

时序仿真与功能仿真的步骤大体相同,只不过中间需要添加仿真库、网表(.vo)文件和延时(.sdo)文件....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 07-23 11:55

•2270次阅读

尽管SERDES(SERializer/DESerializer)拥有十分复杂的设计和验证过程,但已....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 07-23 11:21

•4505次阅读

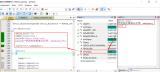

4.1 新建仿真工程 在开始动手仿真之前,首先,我们需要创建一个文件夹用来放置我们的 ModelSi....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 07-23 11:10

•4012次阅读

亚稳态的概念 亚稳态是指触发器无法在某个规定时间段内达到一个可确认的状态。当一个触发器进入亚稳态引时....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 07-23 11:03

•4627次阅读

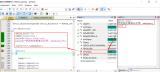

3 ModelSim工程实战之自动仿真说完了 ModelSim 的使用流程,接下来我们将会对每个流程....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 07-23 10:51

•2033次阅读

在一个嵌入式系统中,可能存在许多输入或输出的IO口,输入有霍尔传感器、红外对管等,输出有LED、电源....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 07-23 10:45

•1812次阅读

[导读] 大家好,我是逸珺。 之前挖了图解freeRTOS的坑,挖了坑就得填。今天就从使用开始,先把....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 07-23 10:21

•4088次阅读

【Linux 从头学】是什么这两年多以来,我的本职工作重心一直是在 x86 Linux 系统这一块,....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 07-06 10:21

•4513次阅读

雷达信号处理离不开高速ADC/DAC的使用,而高速ADC/DAC的信号处理对时序的要求非常苛刻。Xi....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 07-02 17:57

•4915次阅读

1、结构描述形式 从电路结构的角度来描述电路模块,称为结构描述形式。 Verilog HDL中定义了....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 07-02 16:29

•2992次阅读

一、简介部分 Zynq是由两个主要部分组成的:一个是由双核 ARM CortexA9 构成的处理系统....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 07-02 11:00

•8059次阅读

Verilog HDL提供了两种类型的显式时序控制:一种是延迟控制,即定义执行语句的延迟时间;另一种....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 07-02 10:52

•1745次阅读

仿真是我们在验证逻辑功能的常用手段。通过仿真,我们可以提早发现一些隐含的逻辑Bug。仿真一般分为功能....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 07-02 10:49

•3075次阅读

一个不容忽视的现实是:很多时候,我们穿衣服时第一道扣子扣错了,却总在扣最后一道扣子的时候才发现。衣服....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 07-02 10:48

•2038次阅读

仿真是我们在验证逻辑功能的常用手段。通过仿真,我们可以提早发现一些隐含的逻辑Bug。仿真一般分为功能....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 07-02 10:43

•2872次阅读