INNOVUS/ICC2吐出的netlist经过Formal/LEC验证后,Star-RC/QRC抽....

DUT的配置寄存器的值是实际值,reg_model有镜像值、期望值的概念。

通常RTL设计要求对芯片/module的输入信号进行reg_in打拍处理,对芯片/module的输出....

5月24日,国家集成电路产业投资基金三期股份有限公司成立,法定代表人为张新,注册资本3440亿人民币....

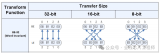

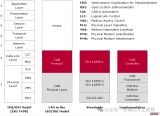

AXI4和AXI3是高级扩展接口(Advanced eXtensible Interface)的两个....

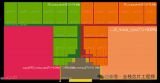

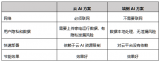

在当前产能利用率低,加上产能陆续开出,尤其是中国大陆业者持续不断扩产的情况下,成熟制程的晶圆代工报价....

正常模式下常见的几个折叠命令: 命令速记: z+f+数字+Enter:创建折叠,从当前光标所在行折叠....

本文接着解析SDF3.0的Timing Checks Entries、Timing Environm....

我们知道Cadecne发明的低功耗文件是CPF,Synopsys发明的低功耗文件格式是UPF

VCLP(VC Low Power)是Synopsys提供的一款低功耗静态规则检查工具,它能够帮助验....

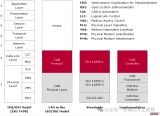

CAN总线(Controller Area Network)是一种用于车辆、工业自动化和其他领域的高....

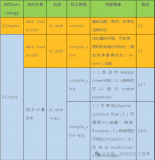

本项目采用hierarchy UPF方式划分了7个power domain、voltage doma....

DVFS(Dynamic Voltage and Frequency Scaling)即动态电压频率....

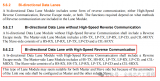

DPHY在high-speed模式下有双向传输的功能吗?我看dphy的协议里有这么两段描述,不太理解....

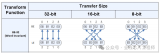

大端,最高字节存储在最低的内存地址,小端则是最低有效字节存储在最低的内存地址。在Verilog中实现....

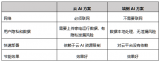

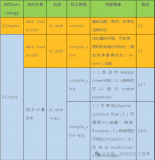

DDR内存技术自问世以来,已经经历了多代的迭代和优化。每一代DDR内存都在性能、容量、功耗和功能上有....

算法全是指海思整个算法库包含完整的基础算法库,可以覆盖电机、电源、电池等多个场景,从类型上可以覆盖大....

并不是因为上述.vh代码不存在,而是由于^M换行符的存在造成的错误。gvim怎么显示^M换行符呢?这....

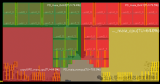

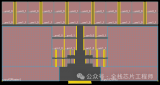

invs的M1蓝色走线总和STD CELL里面的M1 SHORT 怎么处理好?大概70多个short....

不同的core电压和不同的IO电压之间,power island之间,数字和模拟电源之间都需要加入p....

ISP算法仿真中,小编会用reference model调用DPI接口用C++ 算法实现pixel算....

约束ICG的latency为-400ps,目的是把ICG从reg拉开400ps,如果不约束ICG的Q....

我们知道芯片上电后,没有POR复位的或者不带复位的寄存器q端要么处于1,要么处于0状态,对于仿真机器....

时钟传播延迟Latency,通常也被称为插入延迟(insertion delay)。它可以分为两个部....

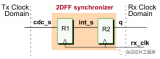

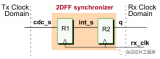

结构:同一个信号源头,两个同步处理器。这里提一下,有两个CDC分析工具的参数配置:

小编首先联想到partition是否将pin push下去,我们可以debug一下,回到maia_t....

先进工艺不再wire load model进行静态时序分析,否则综合结果与后端物理电路差距很大,因此....

进阶版本的低功耗设计如下:7个power domain

下面Cortex-A72培训营VIP学员问:单核CPU PR做完后,怎么输出数据到TOP去做多核的h....

最经典的2DFF 1-bit同步器如下,下图结构通常用于单bit控制信号的异步处理