决策语句允许程序块的执行流程

SystemVerilog case语句与C switch语句类似,但有重要区别。SystemVer....

systemverilog的决策语句if…else语句介绍

决策语句(Decision statements)允许程序块的执行流程根据设计中信号的当前值分支到特....

HDLBits: 在线学习SystemVerilog-Problem

题目输入是一个向量,我们在设计的时候不可能按照case或者三元运算去做设计(工作量巨大),所以我们需....

pulseview软件导入并添加串口解码器

经过研究,逻辑分析仪软件例如pulseview能够通过导入其他格式波形(例如vcd)文件,再对相应通....

与PDM接口相关的开源项目

优秀的 Verilog/FPGA开源项目介绍(三十四)- PDM音频接口设计及信号处理 绪论 今....

如何在应用程序中实现 IDELAY 功能

IO 灵活性是FPGA 最大的优点之一。如果我们设计的 PCB 信号走线不完美,IO的灵活性使我们能....

如何在应用程序中实现 IDELAY 功能

可以在下面看到整体仿真延迟比较小,无法看到该级别延迟的影响。然而,随着仿真执行不同的测试,我们将看到....

基于使用FPGA实现低延迟的成像系统

上面的架构是比较通用的架构,官方也有例程可以参考,但是上面架构多了一个VDMA,这就导致视频传输的时....

如何灵活使用三元运算符

给定四个无符号数,请找出最小值。无符号数可以与标准比较运算符(a < b)进行比较。使用条件运算符描....

generate的用法与结构

主要是generate的用法,整个文件的功能是实现可选多通道数据发送,我们知道Cameralink中....

请问一下怎样去使用HLS创建IP呢

每次我们更改硬件时,我们都需要告诉 HLS 将其导出为硬件描述语言并生成 Vivado 需要的所有各....

FPGA设计过程中常用的FIFO

无论何时,在复杂的 FPGA 设计过程中,都不可避免地需要在模块之间发送数据,实现这一点的常用的是 ....

关于HDLBits的Verilog实现

从这一题开始我们将进行过程块的学习,也就是时序和组合逻辑的一些知识,下面简单介绍一下这方面知识:

简单介绍一下时序和组合逻辑的一些知识

由于数字电路是由用导线连接的逻辑门组成的,因此任何电路都可以表示为module和assign语句的某....

使用Verilog/SystemVerilog硬件描述语言 (HDL) 练习数字硬件设计

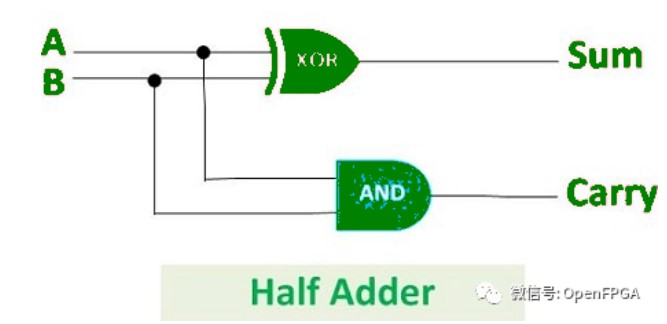

给出了一个可以做16bit加法的模块add16,实例化两个add16以达到32bit加法的。

如何创建FPGA内核/SoC所需的所有常用组件

LiteX 框架为创建 FPGA 内核/SoC、探索各种数字设计架构和创建完整的基于 FPGA 的系....

使用Vitis HLS创建Vivado IP

LUT 或 SICE是构成了 FPGA 的区域。它的数量有限,当它用完时,意味着您的设计太大了!

使用Verilog/SystemVerilog硬件描述语言练习数字硬件设计

在实例化模块时,使用Verilog时有两种常用的方式来进行模块端口的信号连接:按端口顺序以及按端口名....

在时序逻辑中使用阻塞赋值会怎么样?

如例6.1所述,在多个“Always” 进程中使用阻塞赋值。程序块“Always”在时钟的正边缘触发....

如何用FPGA实现网络相关的功能

这几年DPU的概念越来越火,有和CPU、GPU并驾齐驱的势头,通俗的讲DPU分担的工作为虚拟化、网络....

Vitis HLS知识库总结

对于AMD Xilinx而言,Vivado 2019.1之前(包括),HLS工具叫Vivado HL....

关于数字硬件建模SystemVerilog

经过几周的更新,SV核心部分用户自定义类型和包内容已更新完毕,接下来就是RTL表达式和运算符。

使用Verilog/SystemVerilog硬件描述语言练习数字硬件设计

HDLBits 是一组小型电路设计习题集,使用 Verilog/SystemVerilog 硬件描述....

HDLBits: 在线学习SystemVerilog(三)-Problem 10-14

集合中的每个网络或变量称为数组元素。未压缩数组的每个元素的类型、数据类型和向量大小都完全相同。每个未....