编写 HDL 通常是 FPGA 开发中耗时最少的部分,最具挑战性和最耗时的部分可能是验证。根据最终应....

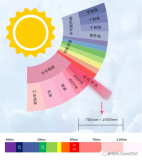

颜色空间转换是图像及视频中常用的解决方案,涉及hsv-rgb、rgb-ycrcb等一些常见的颜色空间....

Cynthion 是一款用于构建、测试、监控和试验 USB 设备的一体化工具。Cynthion 的数....

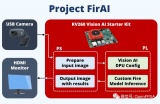

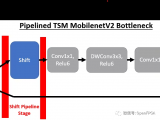

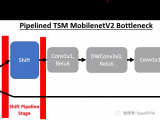

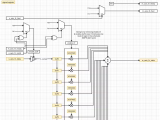

在这个项目中,将在线和离线 TSM 网络部署到 FPGA,通过 2D CNN 执行视频理解任务。 介....

TSM 是一种网络结构,可以通过 2D CNN 有效学习时间关系。在较高级别上,这是通过一次对单个帧....

这篇博客展示了在 AMD Zynq 设计中,如何用 Vitis Vision Library 中的函....

版图文件很大,需要处理的数据量非常大,但本身的逻辑判断并不复杂,所以通常不刚需高主频机型,但要求多核....

时钟是每个 FPGA 设计的核心。如果我们正确地设计时钟架构、没有 CDC 问题并正确进行约束设计,....

该项目包含使用高级综合 (HLS) 的 2D 中值滤波器算法的实现。该项目的目标是在不到 3 ms的....

Vivado综合默认是timing driven模式,除了IO管脚等物理约束,建议添加必要的时序约束....

Bluespec SystemVerilog (BSV) 是由Arvind 开发的 Bluesp....

Bluespec SystemVerilog (BSV) 是由Arvind 开发的 Bluespec....

MicroBlaze™ CPU 是可修改的拖入式预设 32 位/64 位 RISC 微处理器配置系列....

数字信号处理( Digital Signal Processing)技术广泛地应用于通信与信息系统、....

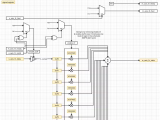

Vivado Schematic中的实线和虚线有什么区别?

FIFO 是FPGA设计中最有用的模块之一。FIFO 在模块之间提供简单的握手和同步机制,是设计....

它有两种操作模式:时钟和设置。时钟模式是标准模式,在此模式下,当前时间显示在数码管上。

《优秀的IC/FPGA开源项目》是新开的系列,旨在介绍单一项目,会比《优秀的 Verilog/FPG....

在上一篇文章中(FPGA 的数字信号处理:Verilog 实现简单的 FIR 滤波器)演示了在 Ve....

该项目介绍了如何使用 Verilog 实现具有预生成系数的简单 FIR 滤波器。

“把算法用RTL实现,怎么做?” 这个问题,对于芯片设计工程师、芯片算法工程师、FPGA工程师来讲,....

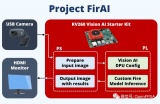

问题:近年来,不断增加的城市人口、更复杂的人口密集建筑以及与大流行病相关的问题增加了火灾侦查的难度。....

J.Bhasker 是IEEE PAR 1364.1 Verilog Synthesis Inter....

之前介绍过一种远程(无线)更新的方式,详见《起飞!通过无线WIFI下载调试FPGA》,这种方式缺点有....

FPGA和外围接口-基础版

从上面的工作可以看出DPU的核心是:网络。所以我们今天讲一个未来的发展核心之一:用FPGA实现NIC....

AMD FPGA支持的MultiBoot特性,可以使FPGA先尝试启动最新的配置(bit)文件,后续....

此次需求提供的十分明确,给出了编码规则及示例,明确了编解码端口要求;仿真模块根据设计进行适配。

对于DFF,之前理解的,DFF在时钟的上升沿进行对D端的数据采集,再下一个时钟的上升沿来临,Q端输出....

一直想做一个可以供大家学习、使用的开源IP库,类似OpenCores,OC上IP在领域内的IP很少,....